#### University of Windsor

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2010

### NoC Prototyping on FPGAs: Component Design, Architecture Implementation and Comparison

Matt Murawski University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Murawski, Matt, "NoC Prototyping on FPGAs: Component Design, Architecture Implementation and Comparison" (2010). *Electronic Theses and Dissertations*. 134.

https://scholar.uwindsor.ca/etd/134

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# NoC Prototyping on FPGAs: Component Design, Architecture Implementation and Comparison

By

Matt Murawski

#### A Thesis

Submitted to the Faculty of Graduate Studies

through Electrical and Computer Engineering

in Partial Fulfillment of the Requirements for the

Degree of Master of Applied Science at the

University of Windsor

Windsor, Ontario, Canada 2010

|   | © 2010 Matt Murawski                                                                                                                                                                                                      |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                                                           |

| 1 | All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium by any means without prior written permission of the author |

|   |                                                                                                                                                                                                                           |

|   |                                                                                                                                                                                                                           |

|   |                                                                                                                                                                                                                           |

|   |                                                                                                                                                                                                                           |

|   |                                                                                                                                                                                                                           |

# NoC Prototyping on FPGAs: Component Design, Architecture Implementation and Comparison By Matt Murawski

A.C. Sodan

Computer Science

J. Wu

Electrical and Computer Engineering

M. A. S Khalid, Advisor

Electrical and Computer Engineering

Dr. Rashidzadeh, Chair of Defense Electrical and Computer Engineering

### Author's Declaration of Originality

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

### Abstract

Continuing improvements in integrated circuit technology over the past few decades enables increasingly large and complex Systems-on-Chip. Due to the large number of components used, the traditional bus-based interconnect scheme becomes cumbersome and restrictive. Hence, the Network-on-Chip interconnect paradigm becomes appealing due to its many advantages such as scalability and superior performance. Much research remains to be done exploring NoC architectures using real world benchmarks. In this thesis we describe the design space exploration of two major NoC components; a flexible adapter based on the Altera Avalon standard and a parameterizable wormhole router. Two well known NoC architectures, torus and ring, were synthesized for Altera FPGAs using these NoC components. The architectures were compared on the basis of packet latency, area and throughput, using a benchmark application. Simulation results show that the ring architecture gives superior area versus performance tradeoffs for the benchmark used.

### Acknowledgements

It is an honor for me to have worked with Dr. Mohammed A. S. Khalid throughout my Masters degree here at the University of Windsor. His guidance, encouragement, wisdom and support carried me through the course of this thesis. My deepest gratitude goes out to him.

I would like to extend my gratitude to Dr. Jonathan Wu and Dr. Angela C. Sodan for serving on my committee and providing constructive criticism of this work. Dr. Rashid Rashidzadeh has been of tremendous help regarding CAD tool issues and I'd like to thank him for his patience and support.

My thanks goes out to my office colleagues, Mike, Mohan, Thuan, Krunal, Abdelrazag and Omar, for their friendly attitude and support whenever needed.

My gratitude goes to the ECE Dept. staff members Don Tersigni, Frank Cicchello and Andria Ballo for their help and assistance.

Gratitude goes to my parents and siblings for providing support and encouragement throughout my work. Their understanding has been greatly appreciated. My gratitude also goes to my brother, Peter, for all the cooking and cleaning I neglected to do!

My friends Dan and Nathan deserve acknowledgement. Thanks for the great stress relief of weekly Baldur's Gate and your understanding of Masters student hardships. We had great times in World of Warcraft every Friday with Matt, Mike, Trinh, and Chris. Scott, your friendship, aid and understanding will not go unnoticed.

Lastly, 7-11, thanks for all the pop.

## Table of Contents

| Author's Declaration of Originality    | iv   |

|----------------------------------------|------|

| Abstract                               | v    |

| Acknowledgements                       | vi   |

| List of Figures                        | x    |

| List of Tables                         | xii  |

| List of Abbreviations                  | xiii |

| Chapter 1 Introduction                 | 16   |

| 1.1 Thesis Objectives                  | 19   |

| 1.2 Thesis Organization                | 20   |

| Chapter 2 Background and Previous Work | 21   |

| 2.1 Network-on-Chip Overview           | 21   |

| 2.1.1 Application Layer - System       | 23   |

| 2.1.2 Transaction Layer – Adapter      | 24   |

| 2.1.3 Data Link Layer – Network        | 25   |

| 2.1.4 Physical Layer – Link            | 28   |

| 2.2 Standard Sockets                   | 28   |

| 2.2.1 Wishbone                         | 28   |

| 2.2.2 Avalon Interface                 | 34   |

| 2.3 FDGA Technology                    | 27   |

| 2.4 CAD Tools for NoC Implementation on FPGAs                     | 37 |

|-------------------------------------------------------------------|----|

| 2.4.1 Altera Quartus II                                           | 37 |

| 2.4.2 Altera SOPC Builder                                         | 38 |

| 2.4.3 Nios II Embedded Design Suite (EDS)                         | 38 |

| 2.4.4 Mentor Graphics ModelSim                                    | 39 |

| 2.5 Related Work                                                  | 39 |

| 2.6 Summary                                                       | 41 |

| Chapter 3 NoC Adapter and Router Design                           | 42 |

| 3.1 Adapter Overview                                              | 42 |

| 3.2 Router Overview                                               | 49 |

| 3.3 Summary                                                       | 53 |

| Chapter 4 NoC Implementation and Evaluation Framework             | 54 |

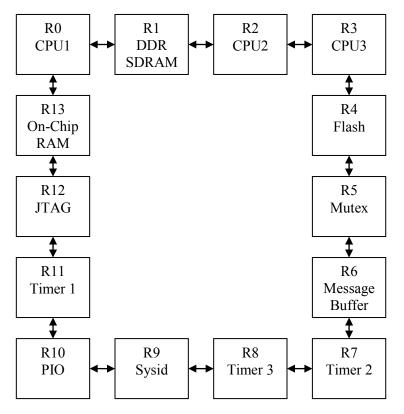

| 4.1 Multi-CPU Benchmark System                                    | 54 |

| 4.2 Implementation of NoC in SOPC Builder                         | 55 |

| 4.3 Nios II Programming                                           | 58 |

| 4.4 Modelsim Simulation Environment                               | 59 |

| 4.5 Summary                                                       | 60 |

| Chapter 5 FPGA Implementation of Torus and Ring NoC Architectures | 61 |

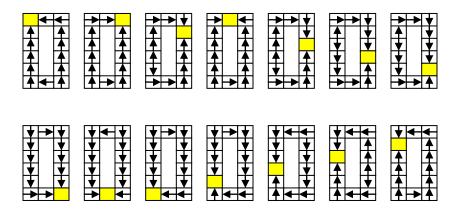

| 5.1 Topology                                                      | 61 |

| 5.2 Placement and Routing                                         | 63 |

| 5.3 NoC Generator                                                 | 66 |

| 5.4 Summary                                                       | 68 |

| Chapter 6 Component Evaluation and Architecture Comparison        | 69 |

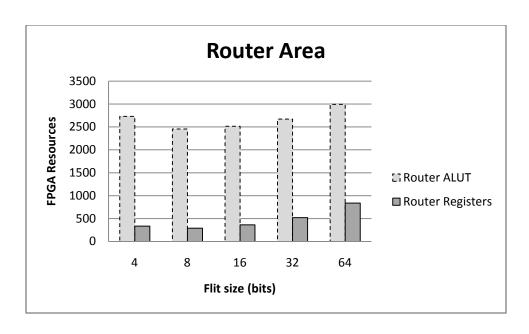

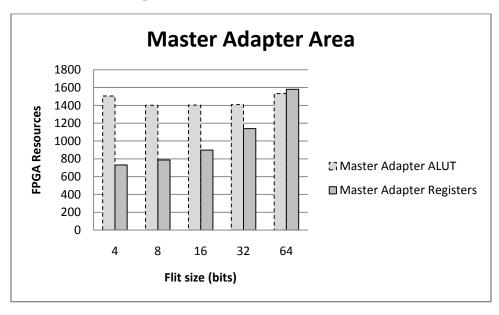

| 6.1 Design Space Exploration of Adapter and Router                | 69 |

| 6.2 Experimental Framework and Evaluation Metrics                 | 73 |

| 6.3 Comparison of Torus and Ring      | 74 |

|---------------------------------------|----|

| 6.4 Summary                           | 80 |

| Chapter 7 Conclusions and Future Work | 81 |

| References                            | 84 |

| VITA AUCTORIS                         | 89 |

# *List of Figures*

| Figure 1 - NoC Component Overview                                       | 17 |

|-------------------------------------------------------------------------|----|

| Figure 2 - NoC Example System                                           | 22 |

| Figure 3 – NoC OSI Layers                                               | 23 |

| Figure 4 - Components Used In NoC System                                | 23 |

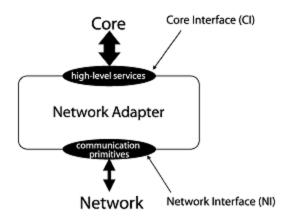

| Figure 5 - Network Adapter[4]                                           | 25 |

| Figure 6 - Example of Deadlock                                          | 27 |

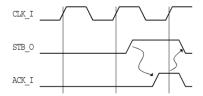

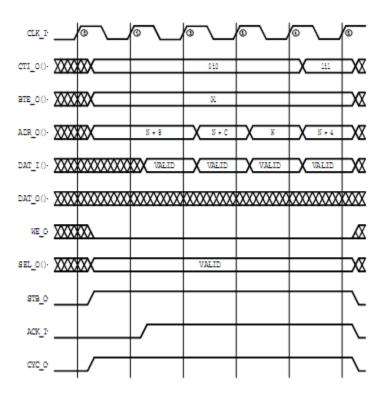

| Figure 7 - Single Transfer Handshaking Protocol for Wishbone            | 30 |

| Figure 8 - Single Read Transfer for Wishbone                            | 30 |

| Figure 9 - Single Write Request for Wishbone                            | 31 |

| Figure 10 - Wishbone RMW                                                | 32 |

| Figure 11 - Block Read Request for Wishbone                             | 33 |

| Figure 12 - Incrementing Bursts for Wishbone                            | 34 |

| Figure 13 - Example Avalon-MM Transfer                                  | 36 |

| Figure 14 - Quartus II Design Flow                                      | 38 |

| Figure 15 - Adapter Overview                                            | 43 |

| Figure 16 - Adapter Design Overview                                     | 45 |

| Figure 17 - Address to Destination Parameter Design                     | 46 |

| Figure 18 - Avalon-Wishbone Glue Logic for Master                       | 46 |

| Figure 19 - Master Sampler 3-Concurrent Process Flowchart in Burst Mode | 48 |

| Figure 20 - Slave Sampler 3-Concurrent Process Flowchart in Burst Mode  | 49 |

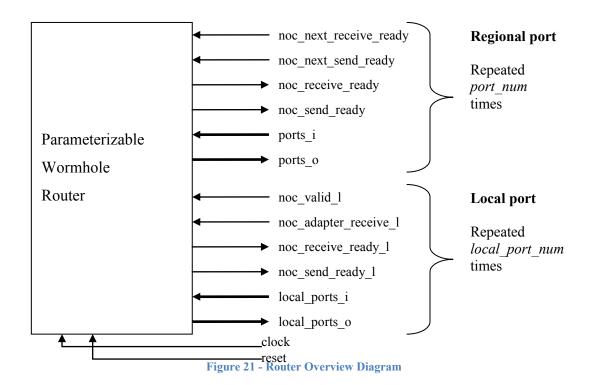

| Figure 21 - Router Overview Diagram                                     | 50 |

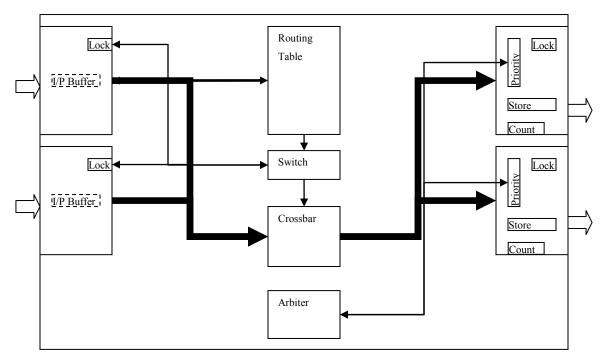

| Figure 22 - Internal Router Design                                      | 51 |

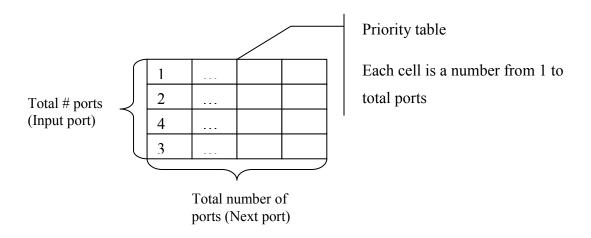

| Figure 23 - Priority Table Design                                       | 52 |

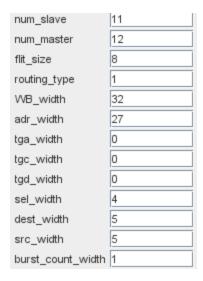

| Figure 24 - NoC Parameters in SOPC Builder                              | 56 |

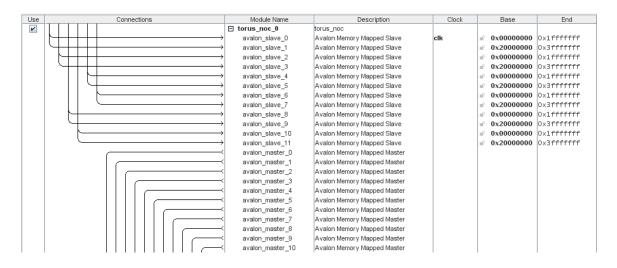

| Figure 25 - Torus NoC Implemented in SOPC Builder                             | 56 |

|-------------------------------------------------------------------------------|----|

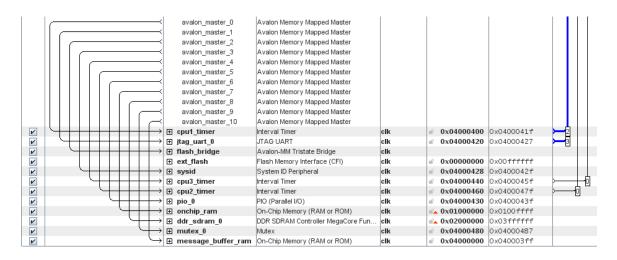

| Figure 26 - Torus NoC Connected to Slave Components                           | 57 |

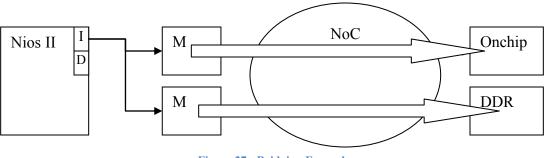

| Figure 27 - Bridging Example                                                  | 57 |

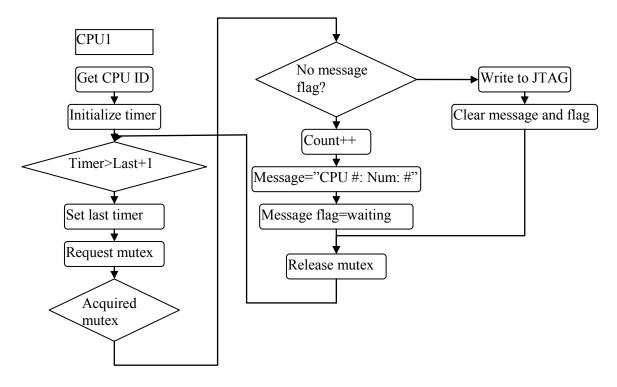

| Figure 28 - CPU 1 Benchmark Flowchart                                         | 58 |

| Figure 29 - CPU 2 and 3 Benchmark Flowchart.                                  | 59 |

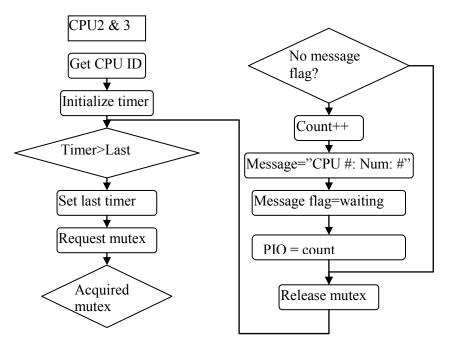

| Figure 30 - Router Regional Handshaking                                       | 60 |

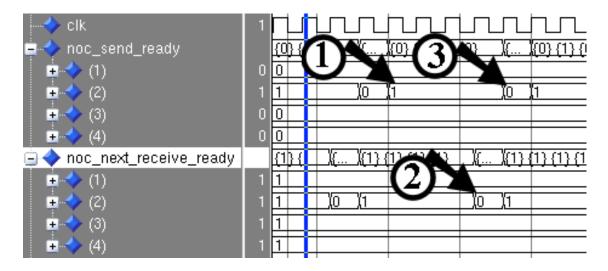

| Figure 31 - Mesh vs. Torus                                                    | 62 |

| Figure 32 - 10-Node Ring Example                                              | 62 |

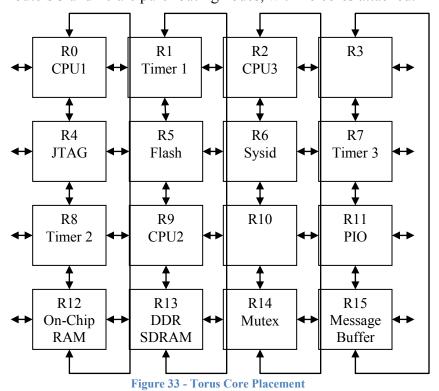

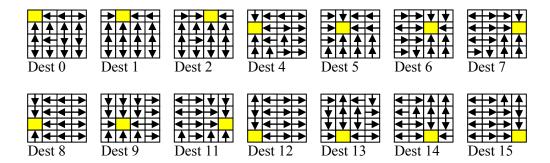

| Figure 33 - Torus Core Placement                                              | 63 |

| Figure 34 - Placement for Routing                                             | 64 |

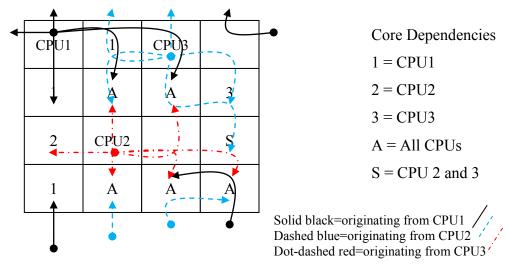

| Figure 35 - Torus CPU Routing                                                 | 65 |

| Figure 36 - Torus Source Routing Paths                                        | 65 |

| Figure 37 - Ring Placement                                                    | 66 |

| Figure 38 - Ring Routing                                                      | 66 |

| Figure 39 - Individual Router Area vs. Flit size                              | 70 |

| Figure 40 - Master Adapter Area                                               | 70 |

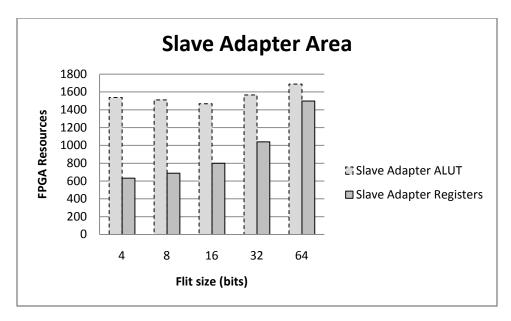

| Figure 41 - Slave Adapter Area                                                | 71 |

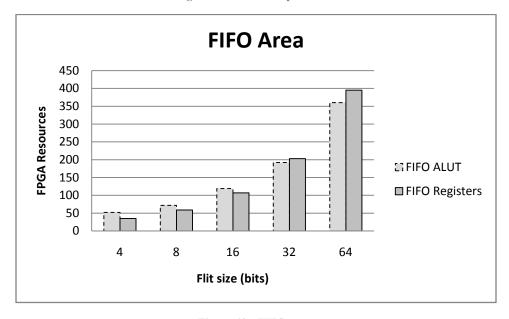

| Figure 42 - FIFO Area                                                         | 71 |

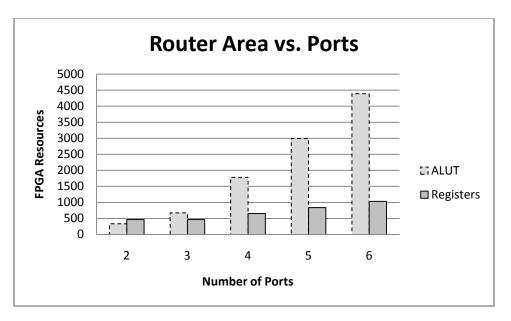

| Figure 43 - Router Area vs. Number of Ports                                   | 72 |

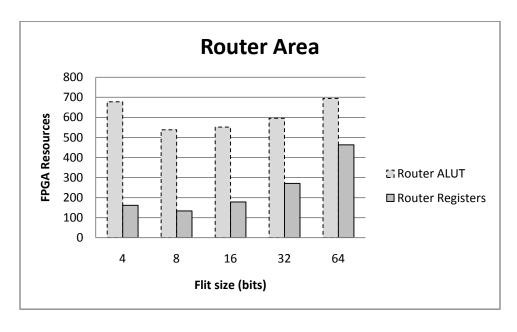

| Figure 44 - Router Area vs Flit Size                                          | 72 |

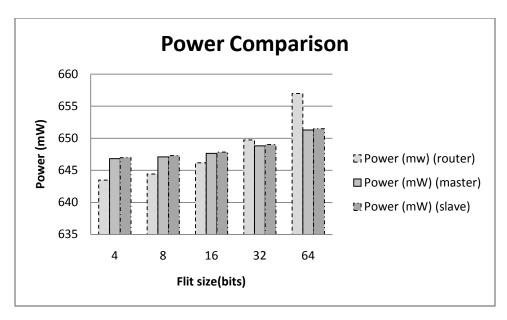

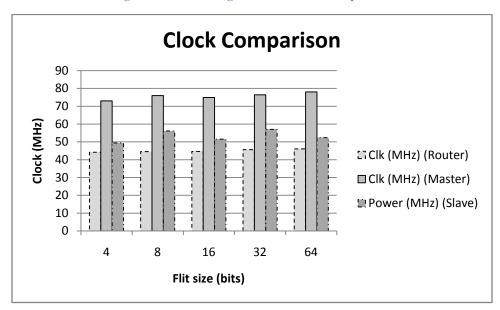

| Figure 45 - Power Usage of Discrete NoC Components                            | 73 |

| Figure 46 - Clock Frequency of Discrete NoC Components                        | 73 |

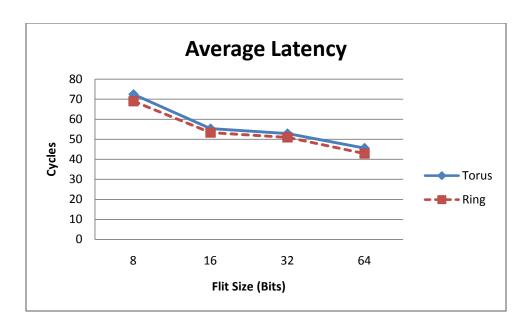

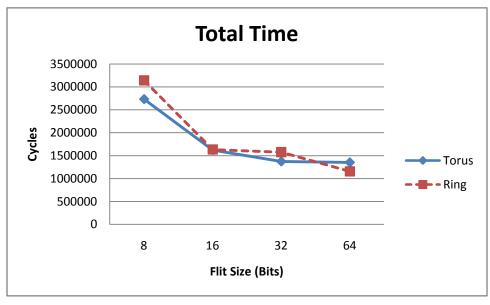

| Figure 47 - Average Latency of Two NoC Topologies                             | 75 |

| Figure 48 - Total Time to Complete Nios II Program                            | 75 |

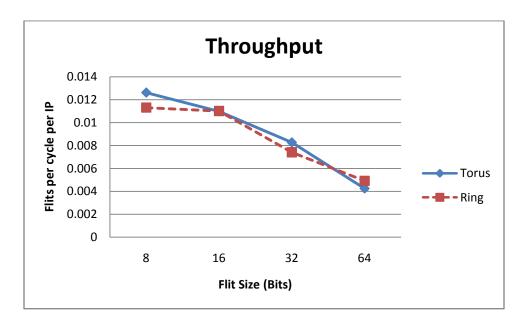

| Figure 49 – Throughput Comparison of Two NoC Topologies                       | 76 |

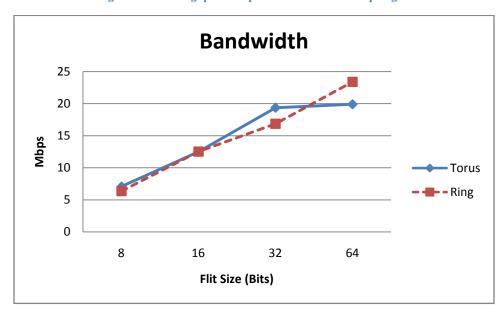

| Figure 50 – Bandwidth Comparison of Two NoC Topologies                        | 76 |

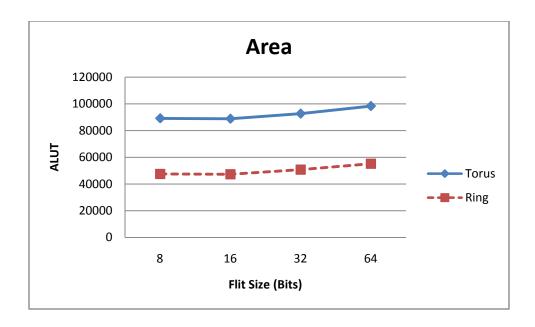

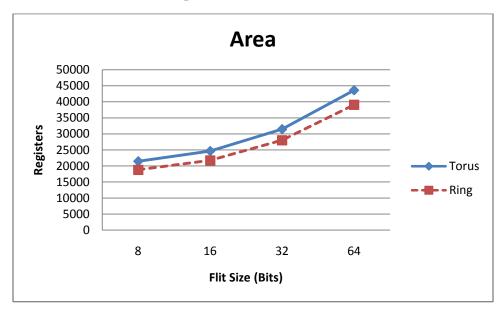

| Figure 51 - NoC Area – ALUTs                                                  | 77 |

| Figure 52 - NoC Area - Registers                                              | 77 |

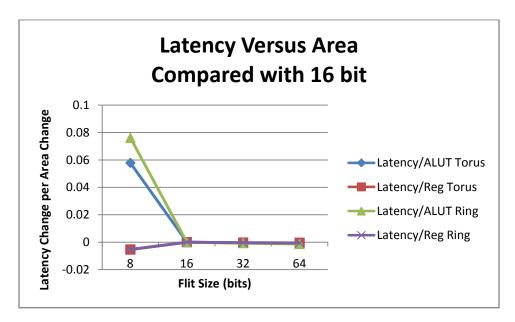

| Figure 53 - Latency Change vs. Area Change, with Respect To 16 Bit Flit Size  | 79 |

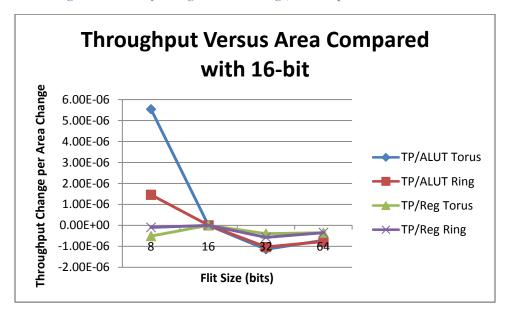

| Figure 54 - Throughput Change vs Area Change With Respect To 16 Bit Flit Size | 79 |

# List of Tables

| Table 1 - Cycle Type Identifier     | 33 |

|-------------------------------------|----|

| Table 2 - Burst Type Extension      | 34 |

| Table 3 - Request Type Design       | 44 |

| Table 4 - Master-Slave Dependencies | 65 |

# List of Abbreviations

| ASIC Application Specific Integrated Circuit AVM Avalon Master AVS Avalon Slave AWB Avalon-Wishbone BE Best Effort BTE Burst Type Extension CAD Computer Aided Design CLK Clock CPU Central Processing Unit CS Chip Select CTI Cycle Tag Identifier DDR Double Data Rate EDS Embedded Design Suite FIFO First In, First Out FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property IRQ Interrupt Request | Abbreviation | Definition                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------|

| AVM Avalon Master  AVS Avalon Slave  AWB Avalon-Wishbone  BE Best Effort  BTE Burst Type Extension  CAD Computer Aided Design  CLK Clock  CPU Central Processing Unit  CS Chip Select  CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                 | ALUT         | Adaptive Look Up Table                  |

| AVS Avalon Slave  AWB Avalon-Wishbone  BE Best Effort  BTE Burst Type Extension  CAD Computer Aided Design  CLK Clock  CPU Central Processing Unit  CS Chip Select  CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                    | ASIC         | Application Specific Integrated Circuit |

| AWB Avalon-Wishbone BE Best Effort BTE Burst Type Extension CAD Computer Aided Design CLK Clock CPU Central Processing Unit CS Chip Select CTI Cycle Tag Identifier DDR Double Data Rate EDS Embedded Design Suite FIFO First In, First Out FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                       | AVM          | Avalon Master                           |

| BE Best Effort  BTE Burst Type Extension  CAD Computer Aided Design  CLK Clock  CPU Central Processing Unit  CS Chip Select  CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                           | AVS          | Avalon Slave                            |

| BTE Burst Type Extension  CAD Computer Aided Design  CLK Clock  CPU Central Processing Unit  CS Chip Select  CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                           | AWB          | Avalon-Wishbone                         |

| CAD Computer Aided Design  CLK Clock  CPU Central Processing Unit  CS Chip Select  CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                     | BE           | Best Effort                             |

| CLK CPU Central Processing Unit CS Chip Select CTI Cycle Tag Identifier DDR Double Data Rate EDS Embedded Design Suite FIFO First In, First Out FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                   | BTE          | Burst Type Extension                    |

| CPU Central Processing Unit CS Chip Select CTI Cycle Tag Identifier DDR Double Data Rate EDS Embedded Design Suite FIFO First In, First Out FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                       | CAD          | Computer Aided Design                   |

| CS Chip Select CTI Cycle Tag Identifier DDR Double Data Rate EDS Embedded Design Suite FIFO First In, First Out FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                   | CLK          | Clock                                   |

| CTI Cycle Tag Identifier  DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                                                                                                        | CPU          | Central Processing Unit                 |

| DDR Double Data Rate  EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                                                                                                                                  | CS           | Chip Select                             |

| EDS Embedded Design Suite  FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                                                                                                                                                        | CTI          | Cycle Tag Identifier                    |

| FIFO First In, First Out  FPGA Field Programmable Gate Array  GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                                                                                                                                                                                   | DDR          | Double Data Rate                        |

| FPGA Field Programmable Gate Array GS Guaranteed Service HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                   | EDS          | Embedded Design Suite                   |

| GS Guaranteed Service  HDL Hardware Description Language  I/O Input / Output  IC Integrated Circuit  IDE Integrated Development Environment  IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                 | FIFO         | First In, First Out                     |

| HDL Hardware Description Language I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                            | FPGA         | Field Programmable Gate Array           |

| I/O Input / Output IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                              | GS           | Guaranteed Service                      |

| IC Integrated Circuit IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | HDL          | Hardware Description Language           |

| IDE Integrated Development Environment IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O          | Input / Output                          |

| IP Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IC           | Integrated Circuit                      |

| 1 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IDE          | Integrated Development Environment      |

| IRQ Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IP           | Intellectual Property                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IRQ          | Interrupt Request                       |

JPEG Joint Photographic Experts Group

JTAG Joint Test Action Group

KB Kilo Byte

LAN Local Area Network

LE Logic Element

LED Light Emitting Diode

MB Mega Byte

MPSoC Multi-Processor System on Chip

NA Network Adapter

NoC Network on Chip

OCP Open Core Protocol

OE Output Enable

OSI Open Systems Interconnection

PIO Peripheral Input Output

PWR Parameterizable Wormhole Router

QoS Quality of Service

RAM Random Access Memory

RISC Reduced Instruction Set Computer

S&F Store and Forward

SDRAM Synchronous Dynamic Random Access Memory

SoC System on Chip

SOPC System on Programmable Chip

TDM Time Division Multiplexing

UART Universal Asynchronous Receiver/Transmitter

VC Virtual Channel

VCI Virtual Component Interface

VCT Virtual Cut Through

VHDL Very High Speed Integrated Circuit Hardware Description

Language

VLSI Very Large Scale Integration

WB Wishbone

WBM Wishbone Master

WBS Wishbone Slave

WH Wormhole

### Chapter 1

### Introduction

As humankind pushes forward through the Information Age, digital technology becomes smaller, and more powerful. It follows without surprise that devices embedded with digital technology are becoming more widespread and common, such as cell phones, digital cameras, and global positioning systems. Such embedded computing systems, or simply "embedded systems", are structures of electronic hardware designed to perform singular functions repeatedly within tightly constrained design metrics [1].

As Moore's Law - Integrated Circuit (IC) designs double in capacity nearly every two years - continues to hold true for the past half decade, the design of embedded systems becomes increasingly difficult and complex. To combat this, designers have shifted their focus from micro-level design to macro-level system design through the employment of hardware reuse. This shift in focus is known as System-on-Chip (SoC) and involves interfacing pre-made hardware modules together to form a coherent system. Those hardware blocks are known as Intellectual Property (IP) cores and they vary from Central Processing Units (CPU), to Random Access Memory (RAM) modules, to counters and to other specific logic designs. Flexibility in IP cores is embraced by means of *parameters*, which offer increased compatibility and proficiency to otherwise blackbox modules.

In SoCs, interconnect structures between IP cores traditionally use a shared bus design, a point-to-point design or a hybrid thereof. Systems level designers have been facing constriction with bus-based, computation-centric interconnection systems [2].

While bus-based interconnections proved to be sufficient for small embedded systems involving few IP cores, the routing of the bus wires, the increasingly difficult custom interconnect design process (such as [3]) and the decreasing performance due to the increasing amount of cores attached to the bus/buses have shown that a paradigm shift is imminent. Borrowing from macro-network communication architectures, Network-on-Chip (NoC) provides a communication-centric design that shows promise in providing the scalability and performance needed for large SoCs [4].

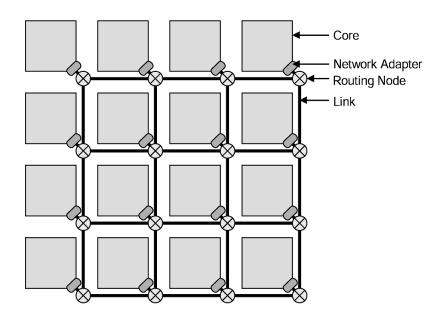

An NoC consists of four major components – IP cores, the network adapters, routing nodes and links. These are similar to the components in a macro computer network, where an IP core is similar to a desktop computer, the network adapters are the wireless network and LAN cards, the routing nodes are the switches and routers and the links are the physical cables connecting the system together. Figure 1 demonstrates an overview of NoC components in a simple 4x4 mesh topology with one core per routing node. As with macro networks, there are many different architectures, mechanisms, parameters and techniques involved in NoCs and hence, many areas remain open for research.

Figure 1 - NoC Component Overview

Numerous NoCs [5] [6] [7] [8] have been proposed to address the growing complexity of SoCs and their communication infrastructure needs. Due to the nature of

NoCs and the systems they are integrated in, designing and simulating test applications is troublesome and time consuming, hence the more favourable *traffic generator* evaluation tool is used. A traffic generator injects artificial distributions of network traffic in order to simulate a realistic system [9]. While traffic generators provide an elegant approach for NoC comparison, it provides a ham-fisted investigation which does not address specific applications and hence misses out on important optimizations due to unique or "bursty" traffic patterns (such as in [10]).

Furthermore, an assortment of NoC parameters, such as topology and channel width, requires additional exploration. The massive design space of NoCs means that even a simple design of an NoC component is a valuable research contribution since it expands on existing understandings and provides reinforcement to existing theories.

Existing IP cores utilize standard socket interfaces such as Wishbone [11], Avalon [12], AMBA [13] and CoreConnect [13], so conforming NoC protocols to these pre-existing bus protocols presents a practical challenge. Thus, the feasibility of instantiating NoCs in existing SoCs and their supporting Integrated Development Environments (IDE) holds as a valuable research topic since it ties theory with practicality.

The requirement for reducing time-to-market for digital designs has quickly led to the creation of Field Programmable Gate Arrays (FPGA). An FPGA is an integrated circuit containing pre-designed resources which can be programmed and configured to act like the desired digital hardware description. This provides a means of a quick prototyping medium for IC designs due to the flexibility of the programmable components, the liberty of manufacturing problems and the fast design cycles. These traits make FPGAs an irreplaceable platform for research purposes.

The task of this thesis is to explore the implementation of a practical NoC. It follows that discrete components need to be created and investigated in order to design an NoC, which includes a network adapter, router and supporting modules. This leads to the study of designing an NoC architecture, the automation of realizing NoC modules with C++ programs, the effects of different NoC parameters on high level NoC and FPGA evaluation metrics and the challenges and issues of using real world SoC software.

### 1.1 Thesis Objectives

The end goal of this research is to explore the feasibility, implementation, design space exploration and evaluation of a practical NoC, targeting FPGAs. In order to achieve this goal, discrete NoC components need to be designed and made flexible for use in an even further parameterizable NoC system. Thus, the effects on higher level evaluation metrics can be studied against an assortment of NoC parameters. There are several major objectives:

- Design and evaluate a network adapter to interface a standard socket with the NoC protocol, while providing easy and powerful flexibility through the use of VHDL generics.

- 2. Design and evaluate a worm-hole router that provides the parameters needed in order to be instantiated within a wide range of NoC architectures.

- 3. Design the required support modules needed for a functional NoC system.

- 4. Automate the construction of an NoC architecture using the above modules with a C++ program based on user input.

- 5. Create a series of NoCs with different topologies and channel widths for evaluation.

- 6. Instantiate the NoC architectures within a realistic benchmark SoC using existing design and simulation software.

- 7. Utilize high level evaluation metrics to obtain results in an automatic fashion and without adding additional resources or performance degradation.

- 8. Synthesize the NoCs targeting an FPGA for area results.

- 9. Synthesize individual NoC components with varying parameters targeting an FPGA for area, power and latency results.

After the NoC protocol was established in the NoC adapter, it was designed to address the initial goal of interfacing with a standard socket. Wishbone [11] was chosen due to its open source nature and was later adapted for Avalon [12] interface for use with Altera's SoPC Builder [14] design software. Using VHDL generics, the wormhole router was designed in order to be flexible enough to fit a designer's needs merely by specifying generic maps. FIFOs and address-to-destination modules were created in order to fulfill

goal number three to create a functional NoC component library. Goal four and five were addressed by using C++ and VHDL component maps to create full NoCs using user input. The sixth goal was validated by using Altera's Quartus II [15], SOPC Builder [14], Nios II IDE [16] and Mentor Graphic's Modelsim [17] to implement and simulate the NoC architectures. Using VHDL file I/O functions and Modelsim variable watching, throughput and average packet latency were measured with the aid of a C++ parser program in order to meet goal seven's requirements. For goal eight, Altera Quartus II [15] was used to synthesize the eight NoC variants for resource usage measurements. Finally, goal nine was achieved by using Altera Quartus II's synthesis, fitting, timing and power analyzer tools with the variations of individual NoC components.

### 1.2 Thesis Organization

This thesis aims to explore NoC prototyping on FPGAs through component design, implementation and parameter evaluation. It begins with background and related work regarding FPGAs and NoCs, granting the reader the needed technological understandings for the topics contained in this thesis. Chapter 3 continues on with in-depth descriptions of the adapter and router discrete NoC components. Chapter 4 covers the system benchmark and supporting topics required for high level NoC evaluation. In Chapter 5, the process of the design of the NoC is detailed, as well as the NoC Generator program. Chapter 6 explains the evaluations and results of the NoCs and discrete components. Chapter 7 concludes the thesis and explains possible future work.

### Chapter 2

### Background and Previous Work

This chapter covers a detailed overview of Network-on-Chip research beginning with its relation to the computer network OSI model. It then flows through each of the four related layers, beginning at the top-most layer, describing the aspects of the NoC paradigm. This is followed by the standard socket section, which goes in depth about the Avalon [12] and Wishbone [11] interfaces. Following this, FPGA technology is covered, detailing the benefits and some explanations about the technology. The CAD tools used in this thesis are briefed and the chapter concludes with a subsection describing related research.

### 2.1 Network-on-Chip Overview

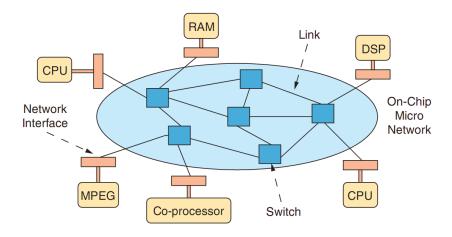

The Network-on-Chip (NoC) paradigm is an architecture inspired by macro computer networks, where data communication is enabled through the use of communication-centric hardware and protocols. [18] shows an excellent example of an NoC overview in Figure 2, where the switch nodes are responsible for routing data between the IP cores, the links are responsible for connecting the nodes, the network interfaces decouple the cores from the NoC and the IP cores carry out higher level functions.

Figure 2 - NoC Example System

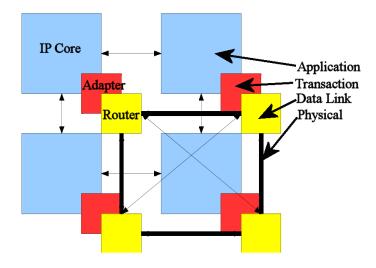

It follows that an NoC is similarly structured after the layered Open Systems Interconnect (OSI) model of macro networks, but due to the limited scope in which on-chip communication encompasses, some layers can be compressed [19]. A 4-layer stack can be utilized, based on a compressed OSI model.

The Application Layer is formed from the Application, Presentation and Session layers of the OSI model, which is the top-most layer. It consists of Intellectual Property (IP) cores and the communication between them. The Transaction Layer consists of the Transport and Network layers of the OSI models. This layer consists of the network adapters, which link the IP cores and the NoC through (de)packetization, error handling and end-to-end connection. The Data Link Layer consists of the inner workings of the routers themselves and is responsible for the flow of traffic between two routers. The Physical Layer is the actual link between the switches - the size of the links, as well as the handshaking protocol between them, lie within this layer's responsibilities. [20] illustrates these layers and how they are interconnected. A more practical structure for NoC architecture explanation uses four categories: System, adapter, network and link.

[4]

Figure 3 - NoC OSI Layers

### 2.1.1 Application Layer - System

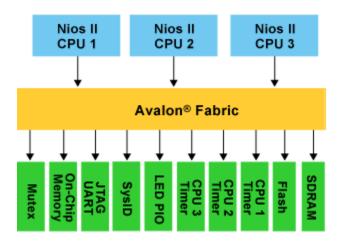

The Application layer covers the IP cores themselves, including communication between them. This thesis uses many IP cores, most of which are common and straightforward to a computer engineer, but the CPU itself is worthy of attention. Figure 4 contains the components used in this thesis.

Figure 4 - Components Used In NoC System

The Nios II is a general purpose RISC soft-core configurable CPU, provided by Altera Corporation in Quartus II [15] and SOPC [14] Builder software[21]. It can have features added and removed in order to optimize resource usage and meet performance requirements. The Nios II [21] CPU interfaces with other cores via the Avalon [12] system interconnect fabric. There are three basic versions of the Nios II: Nios II/e, Nios

II/s and Nios II/f, standing for Economy, Standard and Fast, respectively. The Economy is designed for the least area usage, while Fast provides the most features and performance. Standard provides a reasonable compromise between the two.

While the exact topology of the NoC does not lie within the Application layer, the mapping of the IP cores within the NoC does and is known as clustering. Clustering, or *mapping*, is when the NoC designer decides where different IP cores are embedded in the network in order to optimize certain metrics [22]. Methodologies for regular topologies to optimize energy usage and performance of IP mapping [23][24] have been proposed while irregular topologies is still an open area for research.

The IP cores are further divided by their homogeneity and granularity. Traditional parallel computers have course-grained and homogeneous cores, while NoCs are more flexible [4]. An MPSoC, using the Nios II CPU, was used to form homogeneous processing clusters to perform a JPEG encoding benchmark using a packet-switched NoC in [25].

### 2.1.2 Transaction Layer - Adapter

At this layer, the cores are interfaced with the NoC through a Network Adapter (NA). The NA encapsulates the messages from the cores into packets or streams usable by the NoC, effectively decoupling the cores from the network [4]. Through the use of standard socket protocols, such as OCP [26], Wishbone [27], Avalon [28] and VCI [29], the reusability of an adapter increases. This comes with a price, where conforming to a socket adds additional resources and latency. In a packet-switched NoC, the packets are delimitated into three sections: The packet, the flit and the phit. A message is the data generated by the core, which is encapsulated by the packet, which contains additional information such as source and destination addresses, tail information and so on. A packet is subdivided into flits, which is a basic datagram. The phit is the physical unit that can be transmitted, which is commonly the same as the flit.

Figure 5 - Network Adapter [4]

### 2.1.3 Data Link Layer - Network

The Data Link layer, or *network*, it the heart of the NoC since it is responsible for delivering the messages to their destination. Since there are so many different designs for this layer, it is further subdivided into sections – Topology, Protocol, Flow Control and Quality of Service (QoS).

### 2.1.3.1 Topology

Topology concerns the logical and physical layout of the network and is divided into regular and irregular topologies. While irregular topologies are generally superior, they are difficult to design and lack flexibility [30]. Regular topologies offer simpler physical mapping onto ASICs as well as simpler routing schemes and predictable power and area scaling. Typical regular topologies include mesh, torus, ring, star and binary tree. Mesh and torus are the most common topologies used in NoC research [31]. The main components which make up an NoC is the topology and protocol.

### 2.1.3.2 Protocol

The protocol of an NoC deals with the strategy of how data moves through the network. It is further broken down into three categories – switching, routing and connection mechanism.

Switching involves the methodology of data transportation while routing is the intelligence behind it. Circuit switching is akin to bus-based systems, where a path between cores is set up and data flows between them asynchronously. Packet switching

involves encapsulating messages within a datagram, which then pushes through the NoC by means of buffers. The key trade-off between the two is that circuit-switched techniques have increased bandwidth at the expense of channel set-up time, while packet-switched techniques allow reactive performance. It has been shown in [32] that packet-switched NoCs perform better when the amount of active links is below 40%.

Routing involves the specific path that the data takes through the NoC and is a key component in reducing congestion in the network as well as affecting average latency and power. Routing strategies are either deterministic or adaptive. A deterministic strategy's routing path is set according to the source and destination alone, where an adaptive strategy adjusts the path mid-traversal according to other factors, such as congestion and priority. A minimal routing scheme always utilizes the shortest path possible between cores, while a non-minimal scheme does not. The control mechanism for routing is either centralized or not; a bus-based system has a centralized arbiter, while a router can have routing decisions made locally inside each node.

The connection mechanism concerns the coordination of connection paths between cores. A connection-oriented mechanism creates the path between cores before transmission, while a connection-less mechanism performs pathing on a per-hop basis. A circuit-switching technique is always connection-oriented, while a packet-switched technique can be either.

#### **2.1.3.3** *Flow Control*

The flow control defines the mechanisms of how packets flow through the NoC routes, which in turn encompasses local and global issues [33].

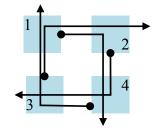

One concept of flow control is the Virtual Channel (VC). The VC involves sharing a physical link between routers by means of Time Division Multiplexing (TDM), which, at the expense of additional logic, reduces congestion, improves wire utilization, improves performance and reduces deadlocking. Deadlocking is a situation when network resources become indefinitely frozen waiting for successive interdependent resources to free. Figure 6 illustrates an example of deadlock. Router 1 needs to send to router 4's local port, router 2 needs to send to router 3's local port and so on, but router 1's east port is waiting for router 2's south port, whom is waiting for router 4's west port, whom is waiting for router 1's east port.

Virtual channels can break the loop, as can proper routing and placement to avoid these situations [4].

Figure 6 - Example of Deadlock

The forwarding strategy involves the methodology behind packet storage and flow within and between nodes for packet-switching techniques. The Store and Forward (S&F) strategy buffers the entire packet within a node and routes the whole packet through the network. While this offers a simple design, the routers have large buffers which consume a lot of area. Wormhole routing involves routing flits instead of packets. Each router contains one flit so the packet spans multiple nodes. This allows for reduced buffer space but it causes congestion issues as the worm spans multiple routers. The Virtual-Cut Through (VCT) strategy is a mix between worm-hole and store-and-forward strategies. Before the first flit is sent, look-ahead mechanisms guarantee an open path before creating a worm; if the path is blocked, then the packet is buffered, similar to store-and-forward.

### 2.1.3.4 Quality of Service

Quality of Service (QoS) is the set of priorities and guarantees regarding specific performance metrics provided to the cores by the network. The services could be latency, power, throughput, jitter and so on. There are two identities of QoS – Best Effort (BE) and Guaranteed Service (GS). Best Effort attempts to improve performance and resource use at the cost of reduced predictability of traffic. Guaranteed Service QoS is inherently connection-oriented and provides the maximum predictability for traffic.

### 2.1.4 Physical Layer - Link

Links are the physical or virtual channels between nodes in an NoC. While research regarding link design is more relevant to ASIC implemented NoCs, there are still some metrics regarding links on FPGAs. Handshaking protocol and bit width can reduce FPGA resource usage as well as power consumption. Most of the issues regarding physical wire problems, such as crosstalk, swing, noise and so on, are generally not issues on FPGAs.

### 2.2 Standard Sockets

SoC core reusability is increased by the use of standard sockets. The interfaces used in this thesis include Silicore/Opencore.org's Wishbone and Altera's Avalon.

#### 2.2.1 Wishbone

Wishbone is an open-source synchronous SoC interconnection architecture, intended to be a general purpose interface between IP core modules. A handshaking protocol for transfers allows variable transfer speeds.

#### 2.2.1.1 Signals

Wishbone has a variety of signals, used to provide flexibility and compatibility for attached IP cores. The signals common to both master and slave devices are:

*CLK\_I* – Clock input. All Wishbone output signals are registered on the rising clock edge.

*DAT I* – Input data array, with a maximum size of 64 bits.

DAT\_O – Output data array, with a maximum size of 64 bits.

RST\_I – Synchronous reset signal

*TGD\_I* – Input data tag array, containing information regarding the *DAT\_I* signal. The data tag contains user defined information.

TGD\_O – Output data tag array, associated with the DAT\_O signal.

Master signals include:

*ACK\_I* – Acknowledge signal used for the handshaking protocol, which indicates the termination of a bus cycle.

*ADR O* – Address output array

CYC\_O – Cycle output signal, indicating a valid bus cycle when asserted. For burst and block cycles, the CYC O signal is held high for multiple transfers until the final cycle.

*ERR\_I* – Error input signal, used as an alternative to *ACK\_I* to indicate a failed transfer. The exact functionality of this signal depends on the IP core.

*LOCK\_O* – Lock output signal, used to ensure a transfer is uninterruptable. The exact functionality of this signal depends on the IP core.

RTY\_I – Retry input signal, used as an alternative to ACK\_I. The exact functionality of RTY I depends on the IP core.

SEL\_O – Select output array, used for fine control over data granularity. The size of SEL\_O depends on the data width and granularity. For example, 8 bits are used for a 64 bit data bus with byte granularity.

STB\_O – Strobe output signal, used to indicate valid data transfer cycles. Unlike CYC O, STB O is deasserted after a transfer.

TGA\_O – Address tag output signal, used to contain tag information associated with the ADR\_O signal. For burst transfers, the TGA\_O tag contains Cycle Tag Identifier (CTI), and Burst Type Extension (BTE) tags regarding burst specifics.

*TGC\_O* – Cycle tag output signal, used to contain tag information regarding a bus cycle. It can be used to distinguish between a single, block or RMW cycle.

WE\_O – Write enable output signal, used to indicate a write transfer.

Slave signals receive the exact same master signals, but in an opposite direction. For example,  $CYC\_I$  receives the cycle output signal, whereas  $ACK\_I$  sends an acknowledge response from the slave to the master's  $ACK\_O$  signal. The types of Wishbone bus cycles are divided into three sections – Single, block and burst.

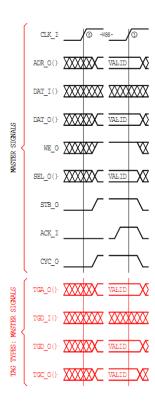

Single transfers use a handshaking protocol shown in Figure 7. The master core initiates a transfer with the strobe signal, where the slave responds with *ACK*, *ERR* or *RTY*. Strobe is held high until a response is received, where the stobe signal is then deasserted. A cycle termination signal (*ACK*, *RTY* or *ERR*) must be asserted according to the logical AND of *STB* and *CYC*.

Figure 7 - Single Transfer Handshaking Protocol for Wishbone

A more detailed waveform is shown in Figure 8, where a sample single read transfer is shown. *CYC* and *STB* are asserted to indicate a read request, where the address, selection and associated tags are also applied. The slave responds with an acknowledge signal at clock edge (1), as well as the data and associated tags.

Figure 8 - Single Read Transfer for Wishbone

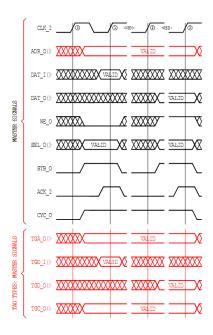

A single write request is very similar, shown in Figure 9, where *WE\_O* is asserted, data is provided by the master on *DAT\_O* and the slave terminates the transfer with an acknowledge at edge (1).

**Figure 9 - Single Write Request for Wishbone**

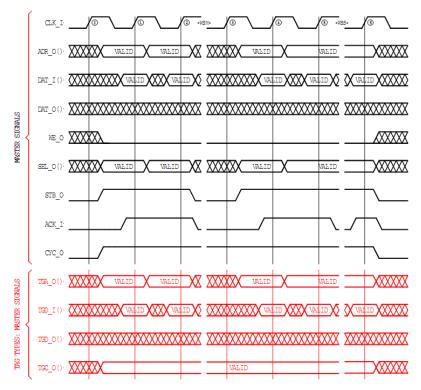

These two requests can be performed in a Read-Modify-Write (RMW) request, shown in Figure 10. The *CYC* signal is held high for the duration of the transfer, while the separate strobe signals perform the actual individual transfers.

Figure 10 - Wishbone RMW

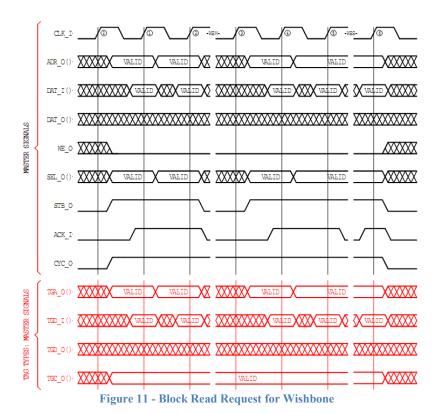

The block transfers operate slightly differently, where the acknowledge signal may be held high for a number of cycles for multiple transfers for increased bandwidth and reduced delay. A block read request is shown in

Figure 11. Note that *CYC* is asserted for the entire duration of the transfer.

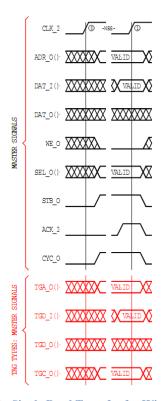

Burst transfers address the issue of the additional delays involved when cycle termination signals, in order to reduce wire routing delay, become synchronous. Additional tag signals are used in order to let the slave know of predictable transfers in advance. The Address Tag contains two additional identifiers, used to specify burst characteristics: Cycle Tag Identifier (CTI) and Burst Type Extension (BTE). CTI is 3 bits, and BTE is 2 bits. They are shown in Table 1 and Table 2.

| CTI(2:0) | Description                      |

|----------|----------------------------------|

| 000      | Classic cycle                    |

| 001      | Constant address burst cycle     |

| 010      | Incrementing address burst cycle |

| 011-110  | Unused                           |

| 111      | End-of-Burst                     |

**Table 1 - Cycle Type Identifier**

| BTE(1:0) | Description  |

|----------|--------------|

| 00       | Linear burst |

| 01 | 4-beat wrap burst  |

|----|--------------------|

| 10 | 8-beat wrap burst  |

| 11 | 16-beat wrap burst |

**Table 2 - Burst Type Extension**

The Classic Cycle is not a burst transfer, where no information about future master cycles is given. End-of-Burst is used to indicate that the current cycle is the last cycle in the burst. Constant address cycle causes a continual access to the same address, until End-of-Burst is given. Lastly, Incrementing address burst uses the Burst Type Extension tag to further define the address behavior. Consecutive addresses, based on BTE are applied. Linear burst simply adds one to the address per cycle, while the beat wrap bursts are modulo the wrap size. Figure 12 is an example of a incrementing address burst transfer.

**Figure 12 - Incrementing Bursts for Wishbone**

#### 2.2.2 Avalon Interface

Altera's Avalon interface is a flexible interconnection architecture aimed at SoCs on FPGAs. While Avalon has six different types of interface – Memory Mapped,

Streaming, Tristate, Clock, Interrupt and Conduit – the Memory Mapped interface will be the main focus due to the nature of the research. The other types will be briefly explained.

#### 2.2.2.1 Avalon-MM

The slave interface uses the following signals. Note that not all of them are required.

*Read – Read* is asserted to indicate a read transfer, where *readdata* is required.

Write – Write is asserted to indicate a write transfer, where writedata is required.

Address – Contains the address used for read and write requests, and can be up to 32 bits.

*Readdata* – Contains the data for a read response.

*Writedata* – Contains the data for a write request.

Byteenable – Used for fine control over data granularity. Selects a specific byte lane for transfer, and has the available bit widths of 1, 2, 4, 8, 16, 32, 64 and 128.

Begintransfer – Asserted for the first cycle of each transfer, regardless of waitrequest.

*Waitrequest* – Asserted by the slave to indicate that it is unable to respond to a request.

*Readdatavalid* – Asserted when data is supplied in response to a read request.

*Burstcount* – Indicates the number of transfers that a burst contains, with a maximum size of 32 bits.

Beginbursttransfer – Asserted on the first burst cycle to indicate the start of a burst transfer.

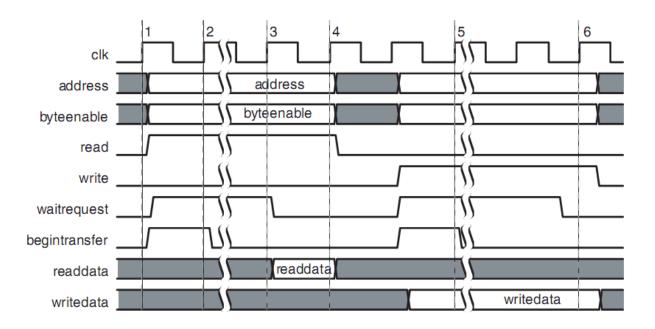

Figure 13 demonstrates examples of slave read and write transfers using Avalon-MM.

Figure 13 - Example Avalon-MM Transfer

#### 2.2.2.2 Avalon-ST

Avalon Streaming (Avalon-ST) interfaces are used for driving unidirectional and high bandwidth data, where applications include DSP, packets and multiplexed streams. Connected components act as either a source or a sink, with data flowing from the source into the sink.

#### 2.2.2.3 Avalon-MM Tristate

Avalon Memory-Mapped tristate interfaces allow off-chip components to be used. It is relatively similar to Avalon-MM, but with the inclusion of Chip Select (CS) and Output Enable (OE) signals, as well as a bidirectional data line. When chip select is present, all signals are ignored unless CS is asserted. When OE is deasserted, the slave will not drive its data lines.

#### 2.2.2.4 Clock

Clock provides synchronization for the Avalon interface and includes a synchronous reset signal. All internal logic returns to initial states when reset is asserted.

#### 2.2.2.5 Interrupt

Each applicable slave device has an interrupt output signal (IRQ), which is asserted when service is needed. The master device receives up to 32 interrupt signals and, depending on the IRQ scheme, services each interrupt according to a priority table.

#### 2.2.2.6 Conduit

The Conduit interface is used with Altera's SOPC Builder software and is used for exporting signals for connection with external FPGA pins.

### 2.3 FPGA Technology

Field Programmable Gate Arrays (FPGA) are special integrated circuits, which provide pre-fabricated components and switches. They can be used to instantiate user-defined logic with Hardware Description Lanuages (HDL), such as VHDL or Verilog. Since FPGAs have grown alongside traditional Application Specific Integrated Circuit (ASIC) manufacturing processes, they contain millions of gate elements and provide an excellent prototype medium for integrated circuit designs. A typical FPGA contains Logic Elements (LE), in the form of look-up tables, which are used to implement custom logic. Newer FPGAs contain more advanced components, such as DSPs, block memories, multipliers, registers and even CPUs. In this thesis, an Altera Stratix II EP2S60F672C3 FPGA is targeted for synthesis analysis in order to provide component area usage as well as power and clock frequency.

### 2.4 CAD Tools for NoC Implementation on FPGAs

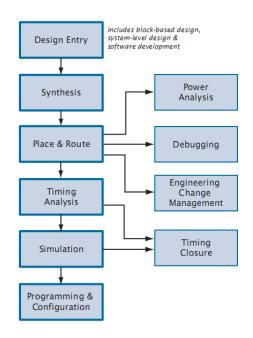

### 2.4.1 Altera Quartus II

Altera Corporation's Quartus II software is a design environment targeting Altera FPGAs. It provides solutions for all phases of FPGA design flow, shown in Figure 14. The Design Entry consists of writing the HDL files and setting their compilation hierarchy. Synthesis involves compiling and analyzing the design files in order to find the required FPGA resources and their connectivity to realize the design, and Place and Route fits the design onto the FPGA hardware using the available resources. Timing Analysis analyzes the performance of the logic and attempts to meet timing requirements.

Simulation is a verification tool, and the FPGA hardware implementation is the final Programming and Configuration stage. Version 9.0 running in CentOS 4.7 was used in this research, where Synthesis was only used for the NoC, and up to Timing Analysis is used for individual components.

Figure 14 - Quartus II Design Flow

#### 2.4.2 Altera SOPC Builder

System-On-a-Programmable-Chip (SOPC) Builder is included with the Quartus II software and allows for design of embedded systems using the softcore Nios II CPU. Devices use the Avalon interconnection fabric and the NoC component is imported and customized with VHDL generics.

### 2.4.3 Nios II Embedded Design Suite (EDS)

The Nios II EDS provides a design environment for configuring, programming, debugging and simulating the Nios II CPUs. The Eclipse IDE in the Nios II EDS provides a C/C++ compiler, linker and assembler for Nios II programs. Other such features include in-circuit debugging and Flash programming.

### 2.4.4 Mentor Graphics ModelSim

Mentor Graphic's ModelSim [17] is a simulation engine for VHDL and Verilog designs. It includes code coverage, assertion tests, breakpoints and in-depth signal and variable simulation that are otherwise not provided by Quartus II's [14] simulation engine. This tool was used to simulate and evaluate the NoC architectures.

### 2.5 Related Work

In this work, many different areas are touched on. We start with the Avalon-Wishbone glue logic and look at related work in that area. Next, we look at related work in the area of NoC adapters, followed by related work that builds an NoC with the Nios II CPU and supporting software. Other areas of related work include similar routers synthesized for FPGAs and their evaluation methodologies. Nevertheless, this paper demonstrates the similarity between the two standard sockets.

Regarding the glue logic between the Wishbone and Avalon interface sockets, a Wishbone compatible I2C controller was ported to the Avalon bus [34]. The glue logic was verified with simulation results. While the logic is correct for single transfers, there is much missing in the way of variable latency support and high speed Avalon block transfers. The *readdatavalid* signal is not supported in this paper and block transfers will not be queued and hence, forced into a wait state. Lastly, there is no mention of burst transfer glue logic.

A packet-switched wormhole router was implemented [27], utilizing Virtex-4 SRL16 components for FIFO implementation, which increases efficiency but decreases portability and design reuse. A Wishbone adapter was included, which supports burst transfers. Since the routers are input queued, deadlock becomes an issue and was solved by adding a separate read request buffer into the Wishbone adapters, which halts any incoming request when the buffer fills. They tested the design with 16 switches, memories and transaction generators. The individual router was synthesized for Xilinx FPGAs with four and five ports and was compared to related work.

In [35], a 4x4 packet-switched mesh NoC was implemented with SOPC Builder using Nios II CPUs. Multiple Stratix II FPGA boards running at 50MHz were used in order to fit the entire design, which results in an on-board throughput of 650Mbps. Inter-

board communication operates at 50Mbps. A software driver is used to access NoC functions within the Nios II CPUs. The system was verified by probing certain NoC components as a message traverses the network and returns to the sender, and thus was found that the maximum communication rate was 43.4 kPackets/s. This large difference between the theoretical bandwidth of 640Mbps is due to the large amount of time required for the packet to traverse the software routines.

In [36], a packet-switched wormhole router with input queuing was designed and analyzed. The router has four regional ports and one local port, and uses X-Y routing. A 3x3 mesh NoC architecture was implemented with traffic generators attached. The buffer size and traffic patterns were analyzed and explored, resulting in overall increased performance as buffer size increased. A 2x2 NoC was synthesized targeting a Xilinx XC2V1000 FPGA.

In [37], evaluation schemes for NoCs are developed in order to compare performance and characteristics of NoCs. Throughput is defined as the total number flits traversed per time per number of IP cores. Transport latency is defined as the average number of cycles required for a packet to traverse the network. These evaluation methodologies were analyzed using a wormhole router simulator contrasted with various network topologies. The topologies used were SPIN, OCTO, CLICHÉ, Folded torus and BFT. They also compared traffic generator injection loads with throughput and average transport latency. They conclude by stating that this is an important basis for NoC evaluation methodology.

Æthereal [7] is a wormhole-routing NoC developed at Philips Research Laboratories which provides two types of services – guaranteed and best effort, as a result of combing a GS and a BE router. A six port router was implemented for ASIC technology using 0.175 mm² and a four port network interface was implemented for the same technology, using 0.172 mm². They were both implemented on 0.13 μm technology running at 500 MHz.

In [38], a store-and-forward packet-switched router is designed targeting FPGAs. X-Y routing is used and the router is designed in order to reduce FPGA resource usage. A single five port router was found to use 352 Xilinx Virtex-II Pro FPGA slices (2.57% of a XC2VP30). A 3x3 mesh network is implemented, using 28% of the XC2VP30

FPGA. To conclude, timing results required to transmit a packet were shown for various flit sizes and mesh sizes.

### 2.6 Summary

This chapter has educated the reader on NoCs, socket standards, FPGAs and supporting software. It began with an overview of NoCs, which was further broken down into four sections based on the OSI model. Each section covered the details and design techniques involved in NoCs. The Wishbone and Avalon socket standards were discussed next, educating the reader on the operation of such standards. A brief description of FPGAs is covered, and is concluded with discussions on the software tools used in this work. Related work is discussed. Chapter 3 begins to detail the design and structure of the discrete NoC components developed in this thesis.

# Chapter 3

# NoC Adapter and Router Design

This chapter discusses the design and structure of the discrete NoC components developed in this thesis. It begins with the NoC adapter, where the NoC protocol is established as well as the supporting modules including *awb* and *adr2dest*. The chapter concludes with a discussion on the wormhole router's design and details.

### 3.1 Adapter Overview

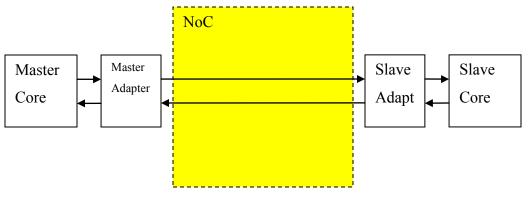

he PWR adapter is responsible for sending and receiving packets from the NoC and converting them into Wishbone [11] or Avalon [12] signals. It essentially makes the IP cores compatible with the NoC.

The PWR project began being Wishbone-compliant but switched to Avalon to make use of Altera's CAD tools. Thus, the Wishbone aspects of the adapter remain largely untested and are an open area for research.

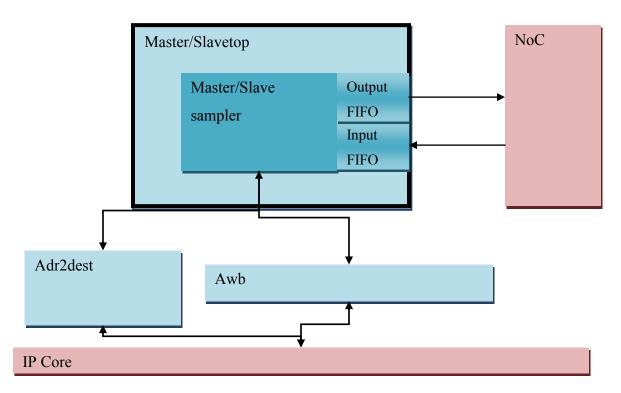

The adapter is divided into two types of adapters – Master and Slave. As illustrated in Figure 15, the Master adapter is responsible for receiving requests from a master component (such as a CPU) and applying the response signals. The Slave adapter is responsible for applying the master requests and receiving the slave responses.

Figure 15 - Adapter Overview

The adapter contains a variety of VHDL generics, offering a degree of design flexibility. The adapter is designed to be compatible with a wide range of signal widths and to conform to Avalon and Wishbone standards. Avalon interface compatibility is obtained through the use of a glue logic module. The logic utilization of the glue logic is very small, and hence negligible. These parameters are divided up into three sections: Interface, NoC and internal. Interface parameters provide flexibility with the Wishbone/Avalon interfacing. NoC parameters allow the adapter to operate in a variety of different NoC architectures. Internal parameters concern the internal operation of the adapter.

Common for both adapters, data width (WB\_width), address width (adr\_width), address tag width (tga\_width), cycle tag width (tgc\_width), data tag width (tgd\_width) and selection width (sel\_width) are VHDL generics used to specify Wishbone interface parameters. Specific to the slave adapter, cti\_lsb and bte\_lsb both indicate cycle type identifier and burst type extension least significant bit locations, respectively.

NoC parameters are *flit\_size*, *fifo\_depth*, *src\_width* and *dest\_width*. *Flit\_size* is the size of a flit, in bits. *Fifo\_depth* is the number of registers in the adapter's FIFOs, which allows the adapter to queue up flits if the NoC is congested. *Sr\_c* and *dest\_width* are the bit widths of the source and destination NoC addresses, respectively. They should both be equal, where the separate parameters are present for future optimization allowing lower bits for source addresses.

The internal parameters are <code>fast\_burst</code>, <code>burst\_depth</code>, <code>burst\_tag\_en</code>, <code>no\_ack</code>, <code>sdram\_delay</code> and <code>Avalon\_bursts</code>. <code>Fast\_burst</code> indicates that burst and block transfers are to be queued up using a burst buffer, thus opening request types 4 and 5. <code>Burst\_depth</code> is the size of the burst buffer – this parameter is useful if there is a small flit size but large packet size (due to large data width, for example) since more requests can be queued and hence the CPU does not get stalled. <code>Burst\_tag\_en</code> is used to enable burst tags for Wishbone transfers – 1 to enable, 0 to disable. <code>No\_ack</code> is used when there is no acknowledge signal for reads and writes – For this thesis, it is set to 1. <code>Sdram\_delay</code> is used with single transfers and delays forming a packet by one cycle – this was needed for interfacing with SDRAM in single transfer mode. <code>Avalon\_bursts</code> is used if Avalon block transfers are used – this distinction is required since Wishbone block transfers are different from Avalon's as explained in chapter 2.

Packets are made up of flits and the minimum packet size is three bits. The first three bits in a packet is always the request type, while the rest of the packet depends on the request type. The adapter analyses the request (or response) of the IP core and chooses the appropriate request type. Table 3 indicates all the request types and their size. In the case of this research, only request types 3, 4 and 7 are used due to the exclusive use of Ayalon block transfers.

| Single/burst read request from master  | Address tgd tgc tga C L S WSource Dest 001/011           |

|----------------------------------------|----------------------------------------------------------|

| Single/burst read response from slave  | Data A E R Dest 101/11                                   |

| Single/burst write request from master | Data Address tgd tgc tga sel C L S W Source Dest 010/100 |

| Single/burst write response from slave | A E R Source Dest 110/000                                |

**Table 3 - Request Type Design**

The complete adapter is formed of five modules – adr2dest, awb, fifo, master/slave sampler and master/slave top. Adr2dest is responsible for converting the address signals into NoC destinations. Awb is the Avalon-Wishbone glue logic. FIFO is the first-in, first-out register bank used to queue incoming and outgoing flits for the adapter. The sampler is the main logic of the adapter, responsible for packetizing and de-

packetizing the interface requests and responses. Finally, the 'top' module is responsible for the hand-shaking protocol between the sampler and FIFOs, and the sampler and NoC. Each component is described below.

Figure 16 - Adapter Design Overview

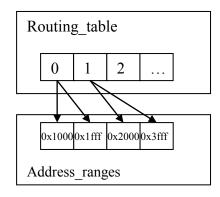

Adr2dest (address to destination) is a simple look-up table for destinations. For a specific range of addresses, a destination is output. There are two unique VHDL generics in this module: routing\_table and address\_ranges. Routing table is an array of integers and contains the destinations that are to be outputted. There are 33 elements in this array and can be expanded by editing the quick\_convert package. The quick\_convert package contains functions and VHDL types used in the source code. Address\_ranges contains the lower and upper addresses in order to output the destination. For address\_ranges 0 and 1, routing\_table 0 is outputted. For 2 and 3, routing\_table 1 is outputted and so on. Figure 17 demonstrates this functionality.

Figure 17 - Address to Destination Parameter Design

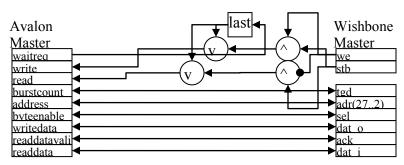

Awb is the Avalon-Wishbone glue logic. It contains both the slave and master adapter interfaces, indicated with a prefix wbs/wbm or avs/avm for Wishbone and Avalon, respectively. Most of the logic is simple name changes for the signals to make building in SOPC Builder [14] easier and the component interface conversion is bidirectional. There is additional clocked logic used to delay the de-assertion of Avalon read/write signals by one cycle since de-asserting these signals is not allowed immediately when the wait\_request signal is de-asserted as well. The connections are illustrated in Figure 18.

Figure 18 - Avalon-Wishbone Glue Logic for Master

FIFO is an array of registers, responsible for queuing flits in to and out of the adapter. An extra 'overflow' register is provided to help stop issues with control signal latency. The FIFO's depth is specified with VHDL generics. 'Empty' and 'Full' are used to indicate when the FIFO can be read from or written to.

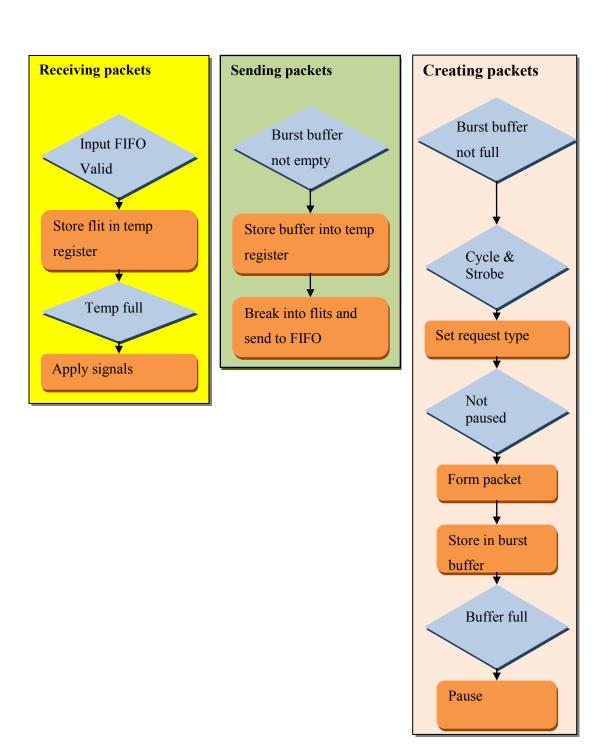

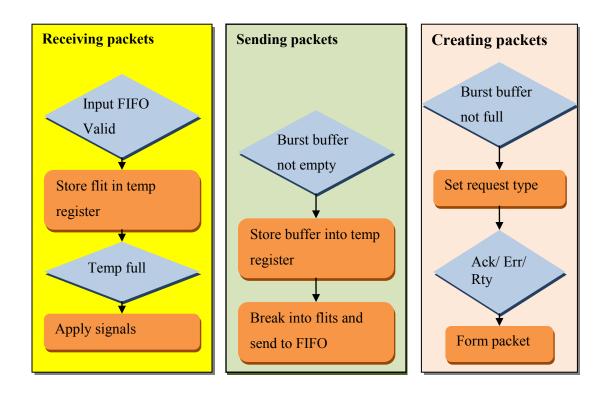

The samplers have two unique versions – master and slave. The operation of the samplers is based around the idea of 'sampling' and saving bus signals, yet the operation