## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1979

# A DESIGN PROCEDURE FOR A ROM IMPLEMENTATION OF A RESIDUE NUMBER SYSTEM BASED FFT PROCESSOR.

BEN-DAU. TSENG University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

TSENG, BEN-DAU., "A DESIGN PROCEDURE FOR A ROM IMPLEMENTATION OF A RESIDUE NUMBER SYSTEM BASED FFT PROCESSOR." (1979). *Electronic Theses and Dissertations*. 596. https://scholar.uwindsor.ca/etd/596

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada Collections Development Branch

Canadian Theses on Microfiche Service Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Rlease read the authorization forms which accompany this thesis.

# THIS DISSERTATION HAS BEEN MICROFILMED EXACTLY AS RECEIVED

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

AVIS

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

### LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS RECUE

# A DESIGN PROCEDURE FOR A ROM IMPLEMENTATION

OF A RNS BASED FFT PROCESSOR

BEN-DAU TSENG

Ъy

#### A Dissertation

Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial fulfillment of the requirements for the Degree of Doctor of Philosophy at The University of Windsor

Windsor, Ontario

2

# © Ben-Dau Tseng 1979

t ,

722862

#### ABSTRACT

This thesis considers some of the design problems associated with a read-only-memory implementation of a Residue Number System based Fast Fourier Transform processor. The principal design parameters identified in this work are the radix of the FFT structure, the number range associated with the processor, the values of scale factors, the manner in which scaling is distributed throughout the processor, the coefficients associated with the integer conversion of twiddle factors and the resolution, in terms of bits, that the related analogue-to-digital converter provides.

The value of the optimal radix that minimizes the number ofcascaded multiplications within the FFT structure has been found to equal four. Using this radix an expression for the theoretical upper bound for number growth in the FFT processor has been derived. Simulation studies have also been used to determine the number growth associated with sample functions that characterize typical inputs that would be applied to the processor.

The specification of a desired mean-squared-error of the frequency domain estimate computed by the FFT processor has been found as a useful criterion of optimality for the design procedure. A comprehensive study of quantization error sources was required in order to provide the theoretical basis for determining how the various design parameters influence the error of the estimate. This analysis has ultimately led to

i

a design procedure in which the values of design parameters that simplify the hardware realization and meet a specified error criterion can be determined.

#### ACKNOWLEDGEMENTS

The author wishes to express his sincere appreciation to his supervisor, Dr. W. C. Miller, for many valuable discussions and constructive criticisms throughout the study period. The advice and assistance of Dr. G. A. Jullien is gratefully acknowledged. Thanks are due to the other members of the department who helped the author in different ways.

Thanks and gratitude are also due to my wife for her diligence and perseverence in the typing of this dissertation.

#### TABLE OF CONTENTS

|                                                                                                                                                                                                                                                        | Page                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                               | i                                      |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                       | iii                                    |

| LIST OF FIGURES                                                                                                                                                                                                                                        | vi                                     |

| LIST OF TABLES                                                                                                                                                                                                                                         | viii                                   |

| LIST OF SYMBOLS                                                                                                                                                                                                                                        | x                                      |

| LIST OF APPENDICES                                                                                                                                                                                                                                     | xii                                    |

| CHAPTER 1: INTRODUCTION                                                                                                                                                                                                                                | 1                                      |

| 1.1 The Residue Number System and A ROM<br>Oriented Implementation                                                                                                                                                                                     | 1                                      |

| 1.2 Conventional FFT Algorithms and<br>Implementations                                                                                                                                                                                                 | . 2                                    |

| <ol> <li>1.3 Objectives of The Research</li> <li>1.4 Organization of The Thesis</li> </ol>                                                                                                                                                             | . 9<br>10                              |

| CHAPTER 2: THE RESIDUE NUMBER SYSTEM AND ITS<br>APPLICATION TO A FFT PROCESSOR                                                                                                                                                                         | 12                                     |

| <ul> <li>2.1 Residue Number System Concepts</li> <li>2.2 The Fast Fourier Transform</li> <li>2.3 A ROM Oriented FFT Structure</li> <li>2.4 Identification of Design Parameters</li> </ul>                                                              | 12<br>17<br>18<br>24                   |

| CHAPTER 3: FFT PROCESSOR CONSIDERATIONS                                                                                                                                                                                                                | ` <b>2</b> 6                           |

| <ul> <li>3.1 Optimal Radix Determination</li> <li>3.2 Number Growth</li> <li>2.1 Mean-square Bound</li> <li>2.2 Theoretical Worst Case Upper Bound</li> <li>2.3 Experimental Worst Case Upper Bound</li> <li>3.3 Quantization Error Sources</li> </ul> | 26<br>29<br>30<br>32<br>35<br>39       |

| CHAPTER 4: A DESIGN PROCEDURE FOR A FFT PROCESSOR.                                                                                                                                                                                                     | 41                                     |

| <ul> <li>4.1 Design Criteria</li></ul>                                                                                                                                                                                                                 | 41<br>41<br>45<br>56<br>63<br>70<br>77 |

#### 82 An Example Design Problem..... 4.5 85 CHAPTER 5: DISCUSSION OF RESULTS..... 85 5.1 5.2 Introduction...... Simulation of The FFT Processor..... 85 Comparison of Theoretical and 5.3 87, Simulation Results..... Ramifications..... 105 5.4 4.1 Fixed-point Arithmetic Number System. 105 109 4.2 The DIF Algorithm..... CHAPTER 6: CONCLUSIONS..... 113 APPENDICES ..... 116 139 REFERENCES ..... 143 VITA AUCTORIS .....

v

#### Page

#### LIST OF FIGURES

ι,

| Ē | ligure |                                                                    | Page |

|---|--------|--------------------------------------------------------------------|------|

|   | 1.1    | Block Diagram of A FFT Basic Calculation                           |      |

|   |        | Unit and Its Auxiliary Memories                                    | 6    |

|   | 1.2    | Block Diagrams of Five Different Realizations                      | 6    |

|   | 2.1    | Block Diagram of A ROM for A Modulus m                             | 14   |

| • | 2.2    | Pipelined Array for The Function $ (a \cdot b)+(c \cdot d) _{m_1}$ | 16   |

| • | 2.3a   | Simplified Representation of An r-Point                            |      |

|   |        | Transform DIT Algorithm                                            | . 19 |

|   | 2.3Ъ   | Simplified Representation of An r-Point                            | i.   |

|   |        | Transform DIF Algorithm                                            | . 19 |

|   | 2.4a   | Simplified Integer Representation of An                            |      |

|   |        | r-Point Transform DIT Algorithm                                    | . 21 |

|   | 2.4b   | Simplified Integer Representation of An                            |      |

|   | ,      | r-Point Transform DIF Algorithm                                    | . 21 |

|   | 2.5    | Conceptual Block Diagram of A FFT Processor                        | . 23 |

|   | 3.1    | Radix-4 DIT Basic Calculation                                      | . 36 |

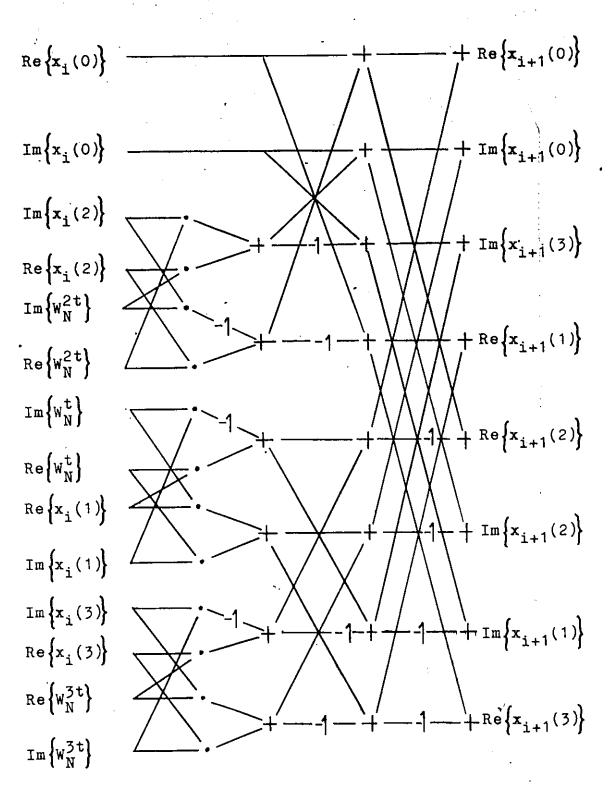

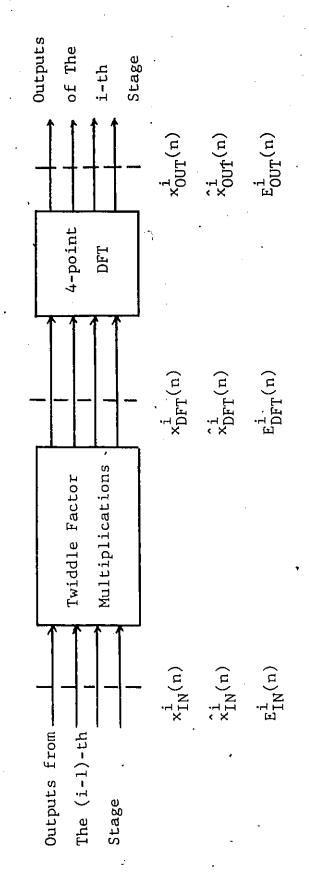

|   | 4.1    | Basic Module of The i-th Stage of A Radix-4                        |      |

|   |        | FFT Processor                                                      | . 47 |

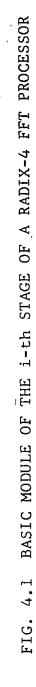

|   | 4.2    | Scaling Schemes of The FFT Processor                               | . 53 |

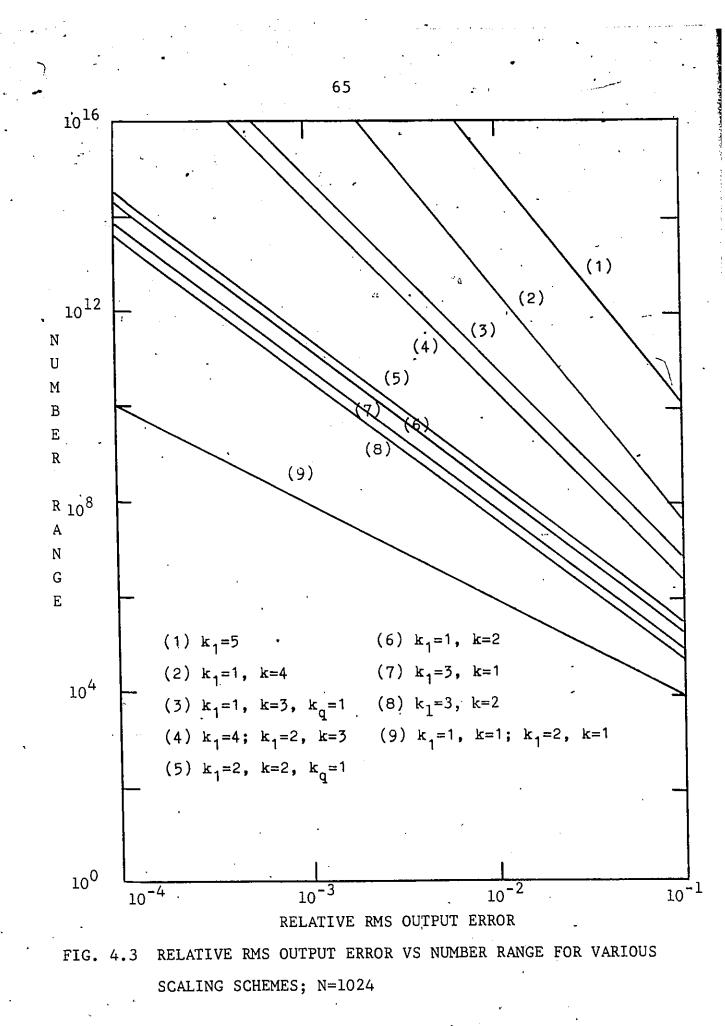

|   | 4.3    | Relative RMS Output Error vs Number Range                          |      |

|   | •      | for Various Scaling Schemes; N=1024                                | . 65 |

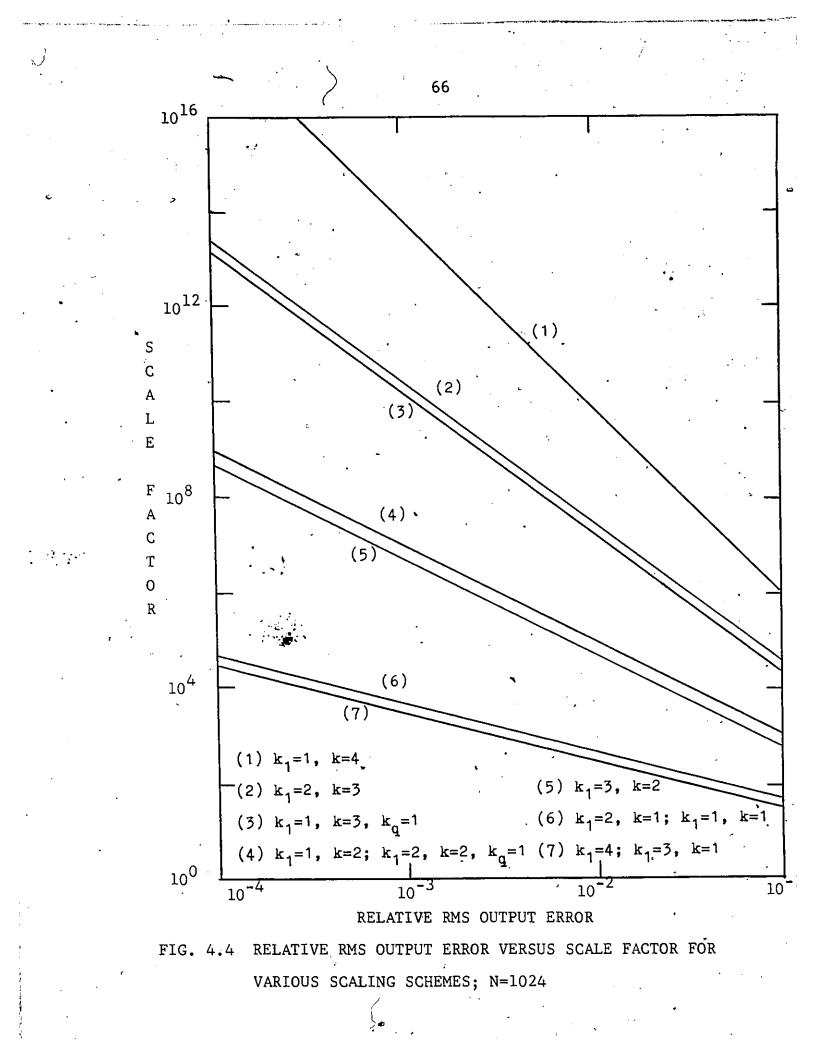

|   | 4.4    | Relative RMS Output Error vs Scale Factor                          |      |

|   |        | for Various Scaling Schemes; N=1024                                | . 66 |

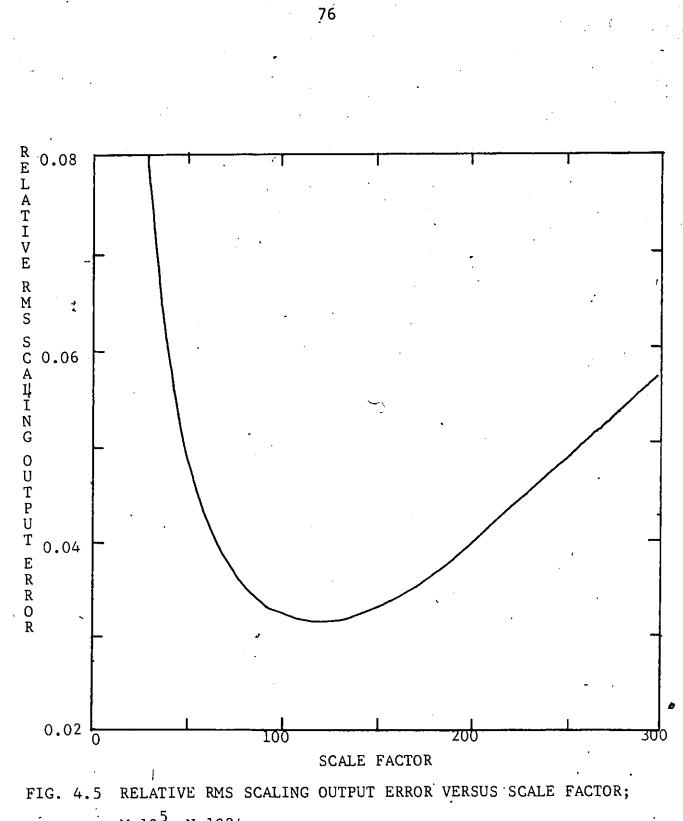

|   | 4.5    | Relative RMS Scaling Output Error vs Scale                         |      |

|   |        | Factor; M=10 <sup>5</sup> , N=1024                                 | . 76 |

| ] | Figure        |                                                               | Page  |

|---|---------------|---------------------------------------------------------------|-------|

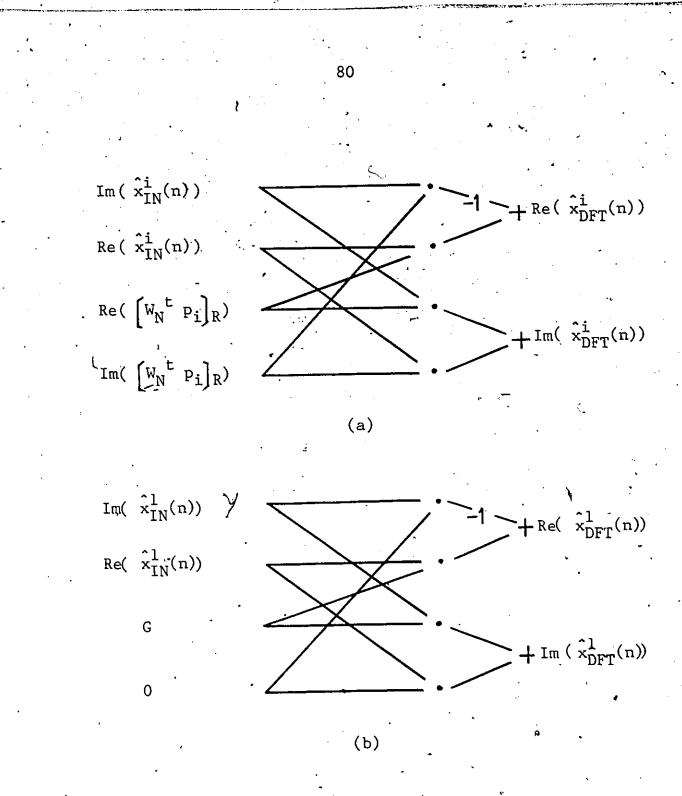

|   | 4.6a          | Twiddle Factor Multiplications                                | 80    |

|   | 4 <b>.</b> 6b | Artificial Twiddle Factor Multiplications                     | • • . |

| _ |               | at The First Stage                                            | 80    |

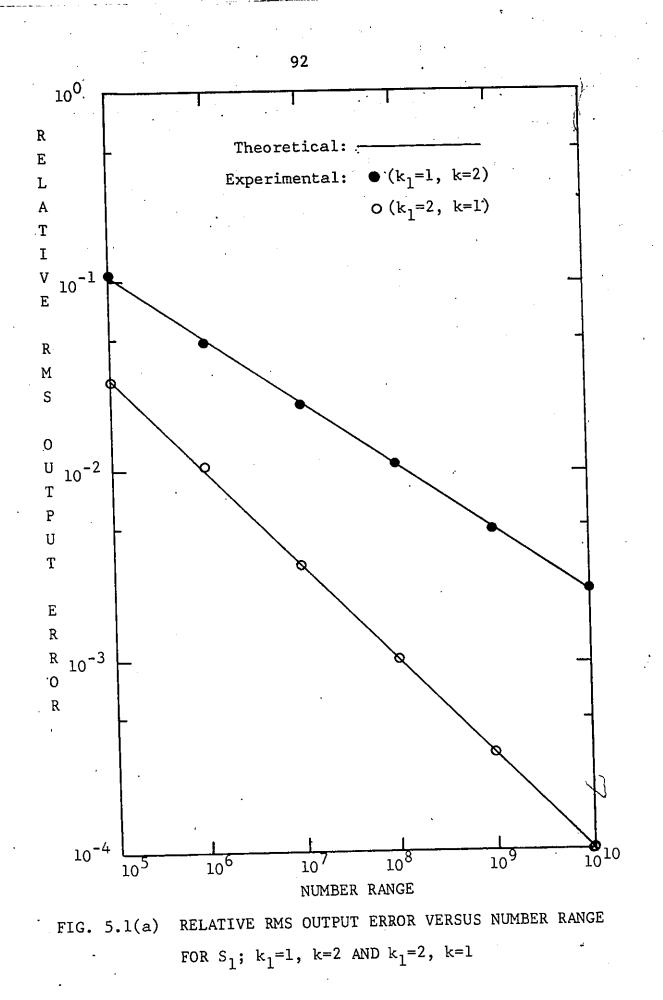

|   | 5.la          | Relative RMS Output Error vs Number Range                     |       |

|   |               | for $S_1$ ; $k_1 = 1$ , $k = 2$ and $k_1 = 2$ , $k = 1$       | 92    |

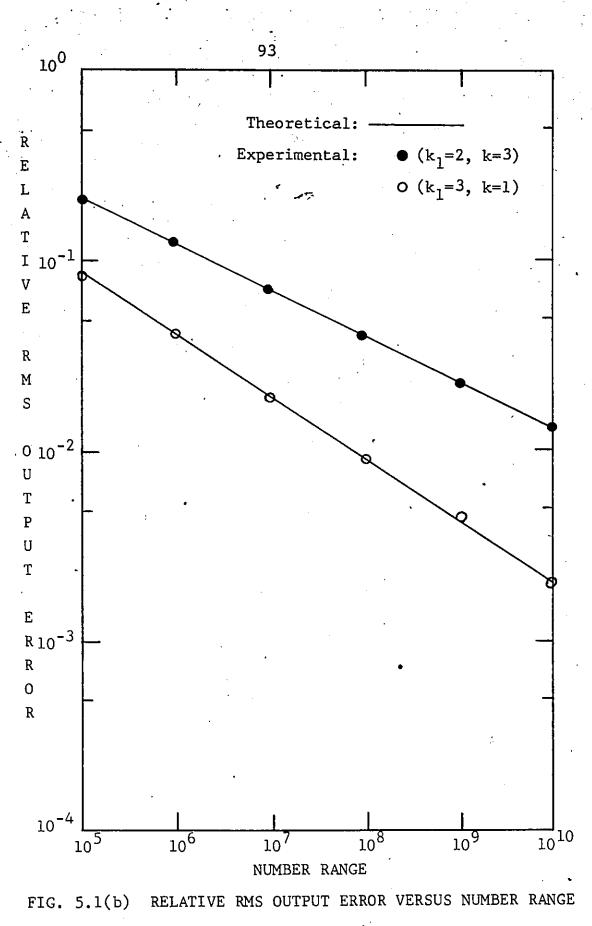

|   | 5.1b          | Relative RMS Output Error vs Number Range                     |       |

|   |               | for $S_1$ ; $k_1 = 2$ , $k = 3$ and $k_1 = 3$ , $k = 1$       | 93    |

|   | 5.2           | Relative RMS Output Error vs Number Range                     | ι     |

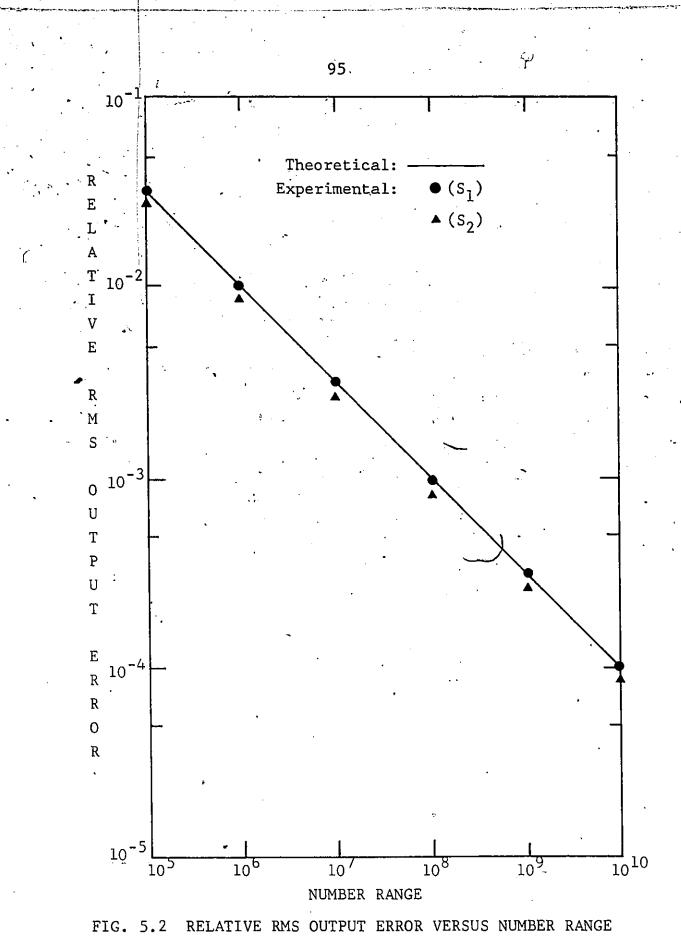

|   |               | for $S_1$ and $S_2$ ; $k_1 = 2$ , $k = 1$                     | 95    |

|   | 5.3           | Relative RMS Output Error vs Number Range                     |       |

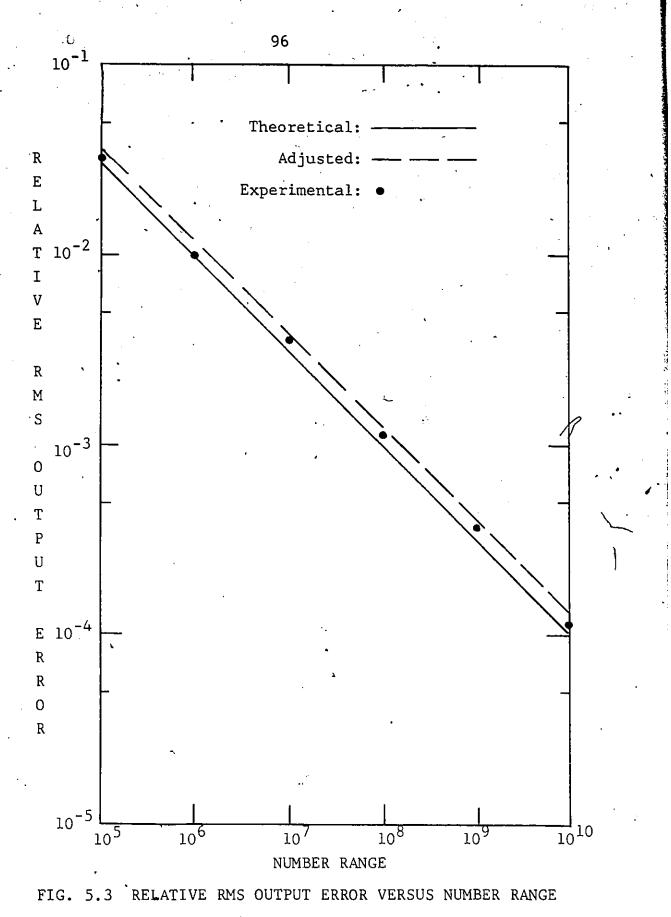

|   |               | for $S_3$ ; $k_1 = 2$ , $k = 1$                               | · 96* |

|   | 5.4           | Relative RMS Output Error vs Number Range                     |       |

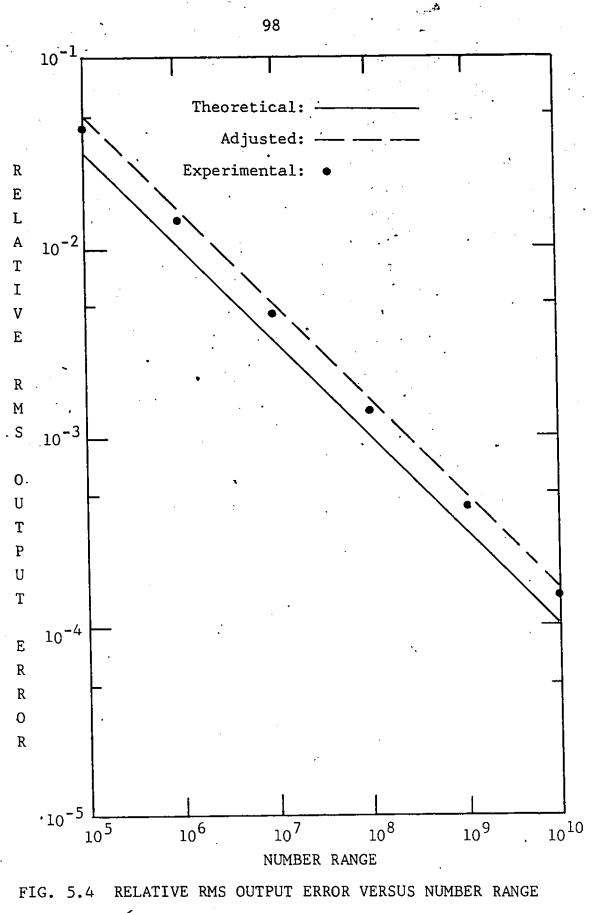

|   |               | for $S_4$ ; $k_1 = 2$ , $k = 1$                               | 98.   |

|   | 5.5           | Relative RMS Output Error vs Number Range                     |       |

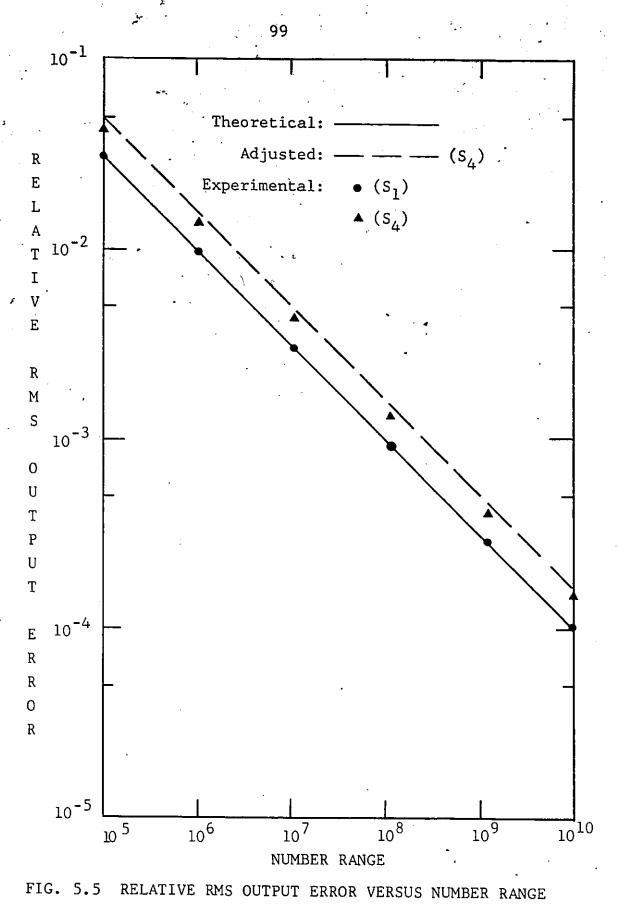

|   |               | for $S_1$ and $S_2$ ; $p_2 \neq P$ , $k_1 = 2$ , $k = 1$      | 99    |

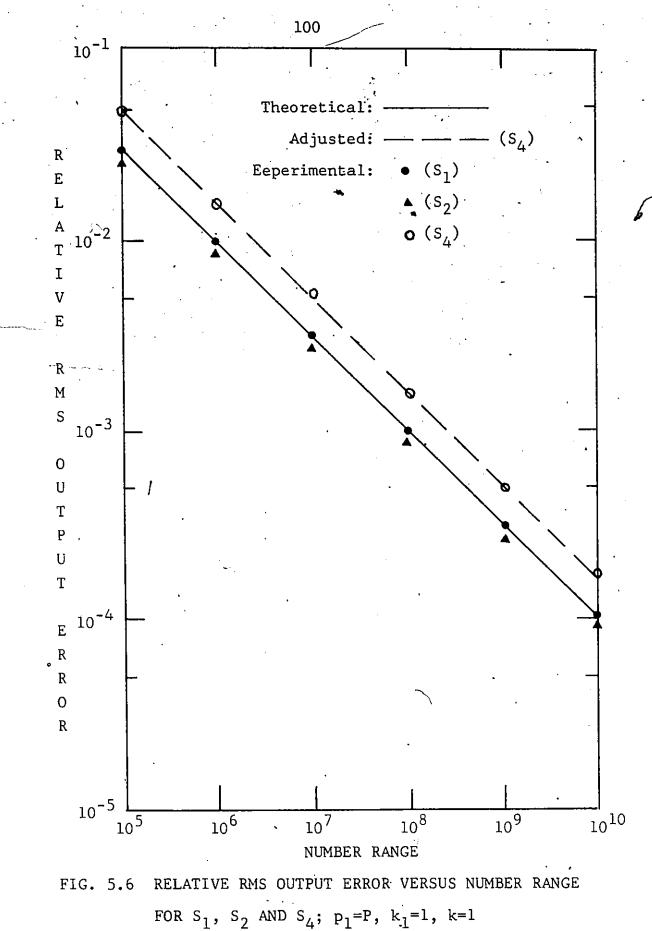

|   | 5.6           | Relative RMS Output Error vs Number Range                     |       |

|   |               | for $S_1$ , $S_2$ and $S_4$ ; $p_1 = P$ , $k_1 = 1$ , $k = 1$ | 100   |

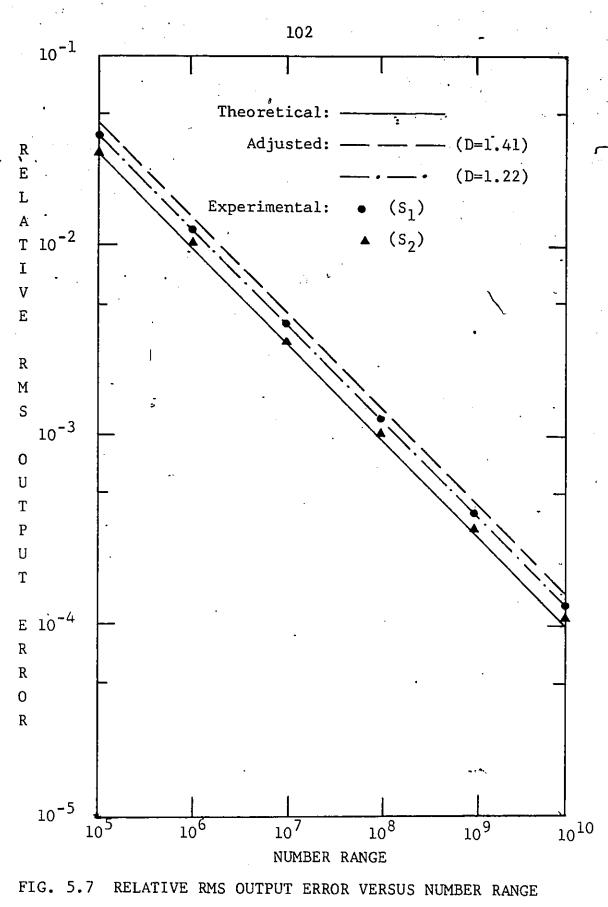

|   | 5.7           | Relative RMS Output Error vs Number Range                     |       |

|   |               | for $S_1$ and $S_2$ with Real Input; $k_1 = 2$ , $k = 1$ .    | 102   |

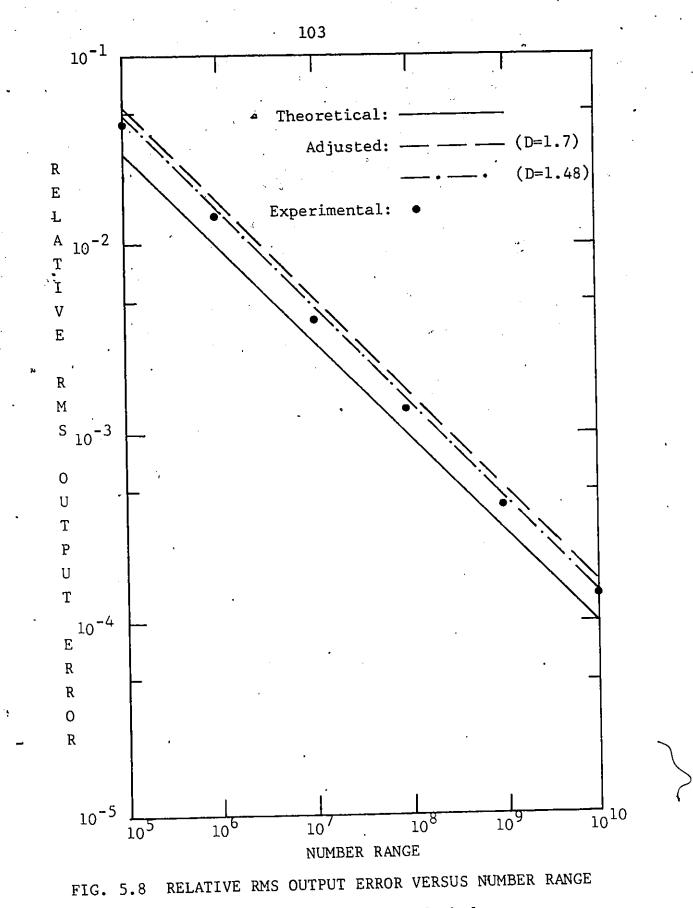

|   | 5.8           | Relative RMS Output Error vs Number Range                     |       |

|   | <b>.</b> .    | for $S_3$ with Real Input; $k_1 = 2, k = 1$                   | 103   |

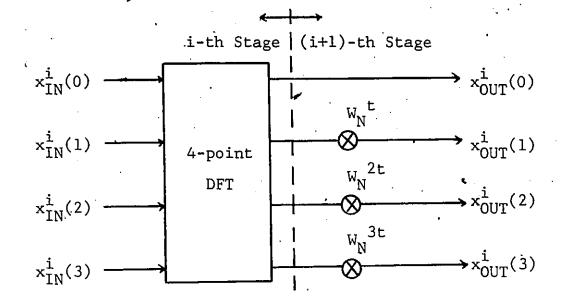

|   | 5.9a          | Basic Module of An Original Radix-4 DIF FFT.                  | 110   |

|   | 5.9Ъ          | Basic Module of A Modified Radix-4 DIF FFT                    | 110   |

|   |               |                                                               |       |

# LIST OF TABLES

| m_11.        |                                                                          | <u>Pa</u>   | <u>ge</u> |

|--------------|--------------------------------------------------------------------------|-------------|-----------|

| <u>Table</u> | Comparison of Five Different FFT Realizations.                           | ;<br>• • •  | 7         |

| 1.1<br>2.1   | Number of Cascaded Non-integer Multiplica-                               |             |           |

| ∠,• ⊥        | tions for Radices of 2, 4, 8 and 16                                      |             | 28        |

| 3.la         | - A Marsh Cose Upper Bound of The                                        |             |           |

|              | Number Growth at Each Stage of A Radix-4                                 |             | •         |

|              | DIT FFT                                                                  | • • •       | 34        |

| 3.1b         | Theoretical Worst Case Upper Bound of The                                |             |           |

|              | Number Growth at Each Stage of A Radix-4                                 |             |           |

|              | DIF FFT                                                                  | <b></b><br> | 34        |

| 3.2          | Simulation Study of Worst Case Upper Bound                               |             |           |

| •            | of The Number Growth at Each Stage of A                                  |             |           |

|              | Radix-4 DIT FFT                                                          | • • • •     | 38        |

| 4.1          | Optimum Functional Relationships between                                 |             |           |

|              | Various Parameters of A Radix-4 DIT FFT;                                 | •           |           |

|              | N=1024                                                                   |             | 62        |

| 4.2          | Comparison of The Total Number of Look-up                                | •           |           |

|              | Tables Required for The Cascade Realizations                             |             |           |

|              | for Four Different Scaling Scheme; N=1024                                |             |           |

|              | 𝒜 <sub>1</sub> =0.01                                                     | • • • • •   | 69<br>    |

| 4.3          | Optimum Functional Relationships between                                 |             | - 1       |

|              | $\alpha_1$ , M and P for Various N; $k_1=2$ , $k=1$                      | ••••        | 11        |

| 4.4          |                                                                          |             |           |

|              | ships of various farameters of a                                         | •           |           |

|              | Different Cases, $p_2=P$ and $p_2\neq P$ ; $k_1=2$ , $k=1$<br>and N=1024 |             | • 75      |

|              | and N=1024                                                               |             | , ,       |

| Table |                                                | Page  |

|-------|------------------------------------------------|-------|

| 5.1   | Properties of Simulation Input Sequences       | . 90  |

| 5.2   | Simulation Study of Worst Case Upper Bound     |       |

|       | of The Number Growth at Each Stage of A        | · ,   |

|       | Real Input Radix-4 DIT FFT                     | 104   |

| 5.3   | Comparison of Word Length Required at Various  | •     |

|       | Units of A Radix-4 FFT Processor for Two       | •     |

|       | Different Methods Using Fixed-point Arithmetic | • 108 |

| 5.4   | Simulation Study of Worst Case Upper Bound     |       |

|       | of The Number Growth at Each Stage of A        |       |

|       | Modified Radix-4 DIF FFT                       | • 111 |

1.....

ix

# LIST OF SYMBOLS

|                             | •                                                 |

|-----------------------------|---------------------------------------------------|

| B.                          | A/D converter width in bits                       |

| E <sup>i</sup> IN(n)        | error at the input of the i-th stage              |

| $E_{DFT}^{i}(n)$            | error at the input to the 4-point DFT of the i-th |

|                             | stage                                             |

| E <sup>i</sup> OUT(n)       | error at the output of the i-th stage             |

| eQ                          | A/D converter quantization error                  |

| eŢ                          | twiddle factor integer conversion rounding error  |

| e <sub>s</sub> '            | scaling rounding error                            |

| j                           | $\sqrt{-1}$                                       |

| · · K                       | scale factor                                      |

| k                           | number of stages between scaling operations       |

| k <sub>i</sub>              | number of stages between the (i-1)-th and i-th    |

| • •                         | scaling operations                                |

| <sup>:</sup> k <sub>q</sub> | number of stages after the (q-1)-th scaling       |

| ų                           | operation                                         |

| L                           | total number of moduli used in the RNS            |

| M                           | number range of the RNS                           |

| m                           | total number of stages in the FFT                 |

| m <sub>i</sub>              | the i-th modulus of the RNS                       |

| I N                         | total number of samples in the FFT                |

| Р                           | integer conversion constant                       |

| P <sub>i</sub>              | integer conversion factor at the i-th stage       |

| ď                           | number of scaling operations required to produce  |

| •                           | a scaled output                                   |

| r                           | radix of the FFT                                  |

|                             |                                                   |

· x

|   | · <b>····</b>                        |                                                   |

|---|--------------------------------------|---------------------------------------------------|

|   |                                      | xi<br>S                                           |

|   | S                                    | number of scaling moduli                          |

|   | W <sub>N</sub>                       | $exp(-j2\pi/N)$                                   |

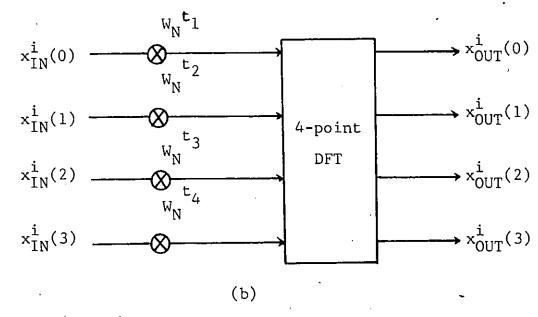

|   | x <sup>i</sup> <sub>IN</sub> (n)     | true value at the input of the i-th stage         |

|   | x <sub>DFT</sub> (n)                 | true value at the input to the 4-point DFT of the |

|   | ۱<br>۲                               | i-th stage                                        |

|   | x <sup>i</sup> OUT(n)                | true value at the output of the i-th stage        |

|   | $\hat{x}_{IN}^{i}(n)$                | scaled integer value at the input of the i-th     |

|   |                                      | stage                                             |

|   | $\hat{x}_{\text{DFT}}^{i}(n)$        | scaled integer value at the input to the 4-point  |

|   |                                      | DFT of the i-th stage                             |

| • | $\hat{x}_{OUT}^{i}(n)$               | scaled integer value at the output of the i-th    |

|   |                                      | stage                                             |

|   | ່ ຝ <sub>1</sub><br>ຜູ <sup>2</sup>  | relative RMS output error .:                      |

|   | ⊲ <sub>Q</sub> ∠                     | relative mean-squared output error due to A/D .   |

|   | 0                                    | converter quantization                            |

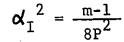

|   | <b>α</b> <sub>1</sub> <sup>2</sup>   | relative mean-squared output error due to integer |

|   | 2                                    | conversion rounding                               |

|   | , <b>∝</b> <sub>s</sub> <sup>2</sup> | relative mean-squared output error due to scaling |

|   | 2                                    | rounding                                          |

|   | $\sigma^2$                           | mean-squared value of the input sequence          |

|   | $Im(\cdot)$                          | imaginary part of the term enclosed               |

| , | Re(•)                                | real part of the term enclosed                    |

|   | [•] <sub>R</sub>                     | the closest integer to the term enclosed          |

-

# LIST OF APPENDICES

| -                                       | Page                                |   |

|-----------------------------------------|-------------------------------------|---|

| APPENDIX A.                             | Number Growth at Each Stage of      |   |

| ``````````````````````````````````````` | A Radix-r DIF FFT117                |   |

| APPENDIX B.                             | An Error Analysis of A Sequentially |   |

|                                         | Realized Radix-4 DIT FFT120         | I |

| APPENDIX C.                             | Simulation Details122               | • |

| APPENDIX D.                             | An Error Analysis of A Radix-4      |   |

|                                         | DIT FFT with Real Input131          | • |

| APPENDIX E.                             | An Error Analysis of A Rounding     | 7 |

|                                         | Effect on The Output of The         |   |

| ,<br>,                                  | Twiddle Factor Multiplications135   | 5 |

#### CHAPTER 1

#### INTRODUCTION

# 1.1 The Residue Number System and A ROM Oriented Implementation

The residue number system (RNS) has received varying degrees of attention from workers in the field during the last two decades. In the early to middle 1960's, considerable work was done on implementation of RNS arithmetic for general purpose computing (1), (2). After years of work much was learned about RNS arithmetic, it was essentially abandoned for general purpose computing because sign detection, magnitude comparison and general division are difficult operations, although fast and simple integer operations of addition and multiplication were demonstrated (1).

However, with the recent advances in high density memories technology that appears eminently suited to performing high speed operations in the parallel RNS structure, interest in RNS arithmetic has been revived. Although some current work is being directed at the problem of building a general floating point arithmetic processor, using the RNS (3), a number of more immediate applications appear to lie in the direction of special purpose digital signal processing hardware, where for many of their operations a pure integer number system such as RNS is all that is required.

Recent, independent, investigators have discussed the RNS based realization of high speed digital filters. Jenkins and Leon [4] investigated RNS techniques for non-recursive filters,

while Soderstrand [5] and Jullien [6] discussed the implementations of recursive filters. The concept of a read-onlymemory (ROM) oriented implementation of the fast Fourier transform (FFT) based on the RNS has been described by TSeng, Miller, Jullien et al [7]. The common feature that emerges from these works, is the use of ROMs to provide parallel arrays of look-up tables for performing the RNS arithmetic operations.

In order to apply RNS principles to hardware structures, it is necessary to convert the conventional digital number system into and out of the residue code. The conversion from binary input into the residue code can be easily implemented using ROMs [6]. But the conversion from residue code into an analog voltage or a binary code is, in general, more difficult. A technique based on a mixed radix conversion to convert residue code into a binary code has been discussed by Baraniecka and Jullien [40]. Two approaches to the design of residue-to-analog conversion were described by Jenkins [8] 1.2 Conventional FFT Algorithms and Implementations

The FFT was first introduced by Cooley and Tukey [9], although it has a long complicated history as described by Cooley, Lewis and Welch [10]. The FFT algorithm is an efficient way of computing the discrete Fourier transform (DFT) of a time series data. Since the DFT is an important computation in most digital signal processing problems, the FFT algorithms have been explored very quickly. Detailed explanation and derivation of the FFT algorithms can be found

ົ

in [11] . Examples of applications to which the FFT has contributed were also discussed in [11] .

In general, there are two basic versions of the FFT algorithms, namely, the decimation-in-time (DIT) algorithm and the decimation-in-frequency (DIF) algorithm [11]. Both of the two versions have various structures which require ordered or scrambled input and generate scrambled or ordered output. The radix-2 DIT algorithm with scrambled input and ordered output, and the DIF algorithm with ordered input and scrambled output are two well-known ones, because their twiddle factors can be easily generated recursively.

In fact, the radix-2 algorithms are special cases for their simplicity. The efficiency of FFT computation can be improved byusing a higher radix algorithm. If the number of samples, N, is an integer power of 2, then the higher the radix is, the better the efficiency is [12]. However, the program becomes more and more complicated for higher radix algorithms. Thus, in most applications only radix 2, 4, or 8 has been used. If, however, for some problems N is not an integer power of 2, one can always append enough number of zeros to make N an integer power of 2 such thata radix 2, 4 or 8 algorithm can be used. Alternatively, a mixed radix FFT algorithm can be used, if N can be decomposed into a product of some small factors [13].

Recently, the concept of the conversion of a DFT to convolution has been used to develop two new algorithms, which are called prime-factor FFT and Winograd Fourier transform

algorithms [14], [15]. Using these algorithms, the number of samples, N, must be a product of some relatively pairwise prime factors. By using the Chinese Remainder Theorem to regroup the input data, these two new algorithms do not require any twiddle factors, while individual factors' DFTs are written in a very efficient way to minimize the number of multiplications.

Since the development of the FFT algorithm by Cooley and Tukey [1], many efforts have been spent on finding faster hardware implementations. Due to the sequential operations of a general purpose computer, software implementations can not operate at a very high speed. For some problems, which have an inherent real time constraint or have a large volume of data, speed becomes very important. Thus, a special purpose hardware designed for performing the FFT algorithm is required.

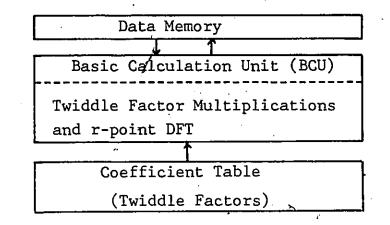

Figure 1.1 shows a block diagram of a basic calculation unit (BCU) and its auxiliary memories for a FFT processor. The BCU performs the required r-point DFT operations and twiddle factor multiplications. The data memory may consist of several submemories, which depends on how it is realized. In most implementations, the BCU is implemented using TTL logic. Recently, some of the BCUs are implemented by mixing TTL logic and ROMs [16].

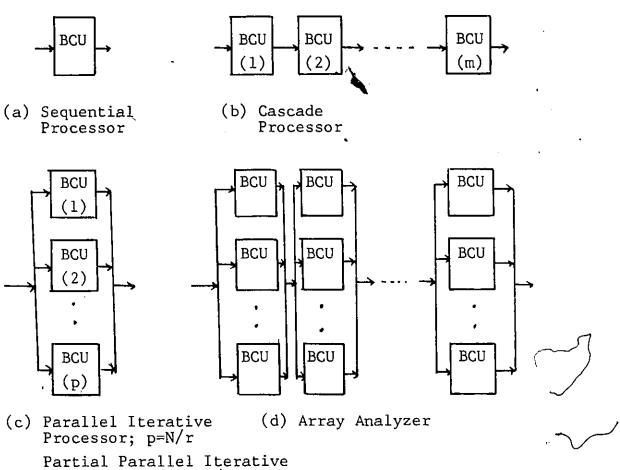

Based on the forms of the realizations, Bergland [17] divided the FFT hardware processor into four different ones, namely, the sequential, cascade and parallel iterative processors, and the array analyzer. In addition, there is another

See.

type of realization, which will be called partial parallel iterative professor. These five different realizations are shown in Figure 1.2. Table 1.1 also shows some of the features of the five different realizations, where N is the total number of stages. The first realization is the simplest but slowest The costs of the fourth and fifth realizations are one. very high, which limit their applications. For a higher speed system, the second realization is usually used. For efficient implementation, the number of BCUs required in the third realization, p, must be an integer power of r. When p is equal to r, they are called Dual-2 and Quad-4 processor for radices of 2 and 4, respectively [18]. In fact, when  $r \leq m \leq 2r$ , the third realization with p equal to r is better than the second realization as far as both the speed and cost are concerned.

Due to the hugh amount of literature, a complete survey of FFT hardware implementations is not attempted. In order to show the tendency of FFT hardware realization, a discussion of some realization will now be given.

Bergland and Hale [19] first proposed a cascade FFT processor to compute spectra, where the twiddle factors were generated recursively. Using the principle introduced by Stockham [20], O'leary described a non-recursive digital filter using cascade FFT [21], where two independent data can be transformed simultaneously. Groginsky and Works [22] proposed a similar structure, and introduced a technique of pipelining, such that the new data can enter

- <u>-</u>

FIG. 1:1 BLOCK DIAGRAM OF A FFT BASIC CALCULATION UNIT AND ITS AUXILIARY MEMORIES

Processor; 1< p<N/r.

FIG 1.2 BLOCK DIAGRAMS OF FIVE DIFFERENT REALIZATIONS

TABLE 1.1

# COMPARISON OF FIVE DIFFERENT FFT REALIZATIONS

| Realization (N = r <sup>m</sup> ) Calculation Unit<br>(1) Sequential 1<br>(2) Cascade m | tion Unit |                 |                  |                        |

|-----------------------------------------------------------------------------------------|-----------|-----------------|------------------|------------------------|

|                                                                                         |           | r<br>Parallel   | in<br>Sequential | Time                   |

|                                                                                         |           | 1               | m•(N/r)          | ш•(N/r)•D <sup>*</sup> |

|                                                                                         |           | E<br>,          | , N/r            | 2•(N/r)• D             |

| (3) Partial Parallel P<br>Iterative                                                     | بې        | ф.              | ш((N/r)/p)       | ш•(d/(т/N))•ш          |

| (4) Parallel . N/r .                                                                    | /1        | N/r             | L<br>L           | Qu                     |

| (5) Array m.(N/r)                                                                       | /r)       | $m \cdot (N/r)$ | 1                | D<br>N                 |

D is the time required for performing one basic calculation \*

\*\* 1 < p < N/r

continuously into the processor, while the processing of earlier data is carried out. Veenkant [18] introduced a different type of realization which uses r BCUs to increase the number of parallel operations at each stage.

Pease [23] brought out an idea to use slow memory efficiently by splitting main memory into several submemories. Corinthios [24 - 27] utilized Pease's idea and reported a series of improved realizations. He first proposed a sequential processor with a wired-in design to minimize control circuitry [24]. Two memories, input and output memories, were used. The output memory collects the intermediate results and feeds them back to the input memory, which becomes the input data for the next stage. Using a binary counter to control the ordering of feedback from the output memory, the processor can receive input data in natural order and generate output data in natural order, too. Then he developed a machine oriented FFT algorithm [25]; where both the input and output memories were partitioned into r submemories such that the shuffle operations were carried as an inherent part of the feedback of each stage. Furthermore, the feedback was completely eliminated by interchanging the role of the input and output memories [26]. Finally, a radix-4 256-point FFT processor was actually constructed, with a sampling frequency of 1.6 MHz Specifically, a fixed-point arithmetic was used. [27].

- Martinson and Smith [28] introduced a modified floatingpoint arithmetic, which uses fewer components than the fixedpoint arithmetic with an equivalent performance level. They also suggested that a ROM may be used to implement a multiplier.

For example, a 5x5 bits multiplier with rounding to 8 bits can be implemented using 8K ROM. Liu and Peled [16] further utilized the idea of trading memories for logical gates. A new approach, which uses the technique of "bit slice" to store all possible outcomes of arithmetic operations into ROMs, was developed.

1.3 Objectives of The Research

, The FFT algorithm has been used to compute the DFT in a number of diverse applications [29 - 31]. The hardware realizations of these processors have ranged from general purpose digital computer to dedicated larger scale integrated circuits. Recently, ROM implementations of the FFT have been considered because of their potential for a high speed parallel architecture [7].

This thesis considers some of the design problems associated with a ROM implementation of a RNS based FFT processor. Normally a ROM oriented scheme, based on table look-up methods, would not be feasible in a weighted magnitude system for any realistic dynamic range, due to the number of possible combinations. The use of the RNS allows a number to be represented with respect to a number of moduli. The operations with respect to the various moduli can be carried out independently of each The resulting small dynamic range makes it possible to other. use ROM table look-up techniques and independent parallel operations capability provides the basis for a very high speed pro-Since memory technology is evolving rapidly, the processor. posed realization can take immediate advantage of any decreased access times.

Since, in general, a FFT can not be implemented exactly, the specification of a desired root-mean-square (RMS) error of the frequency domain computed by the FFT processor can be used as a criterion of optimality of the design procedure. A comprehensive study of quantization error sources is required in order to provide the theoretical basis for determining how the various design parameters influence the error of the estimate.

There are quantization error problems associated with the proposed RNS implementation that have not been fully treated in the literature. The most closely related papers

[32], [33] deal primarily with the radix-2 FFT and consider only fixed-point arithmetic. This thesis presents an analysis of radix-4 FFT quantization error based on a consideration of scaling, integer conversion, dynamic range of the number system, number of stages and A/D quantization. This analysis then leads to a design procedure in which the values of all design parameters, that simplify the hardware realization and meet a specified error criterion, can be determined.

#### 1.4 Organization of The Thesis

In Chapter 2, the mathematical concepts of the RNS is introduced through a discussion of its basic properties. It is shown that the RNS is much more suitable for parallel structure than the weighted magnitude representations (such as the binary number system), because arithmetic operations are fully independent digits. The implementation of residue arithmetic using ROMs is described, and the advantages using

arrays of ROMs are also discussed. Following a brief description of the FFT, a ROM oriented FFT structure is proposed. Also, all design parameters are identified in this chapter.

As residue arithmetic is carried out in the integer number system, the magnitudes of numbers increase very rapidly after multiplication operation, and hence it is necessary to determine the radix of the FFT that minimizes the number of cascaded multiplications for a given number of samples. The optimal radix is shown to be equal to 4 in Chapter 3. Other considerations which include the number growth at each stage and different quantization error sources in the FFT processors are also discussed./

In Chapter'4, a quantization error analysis of the radix-4 FFT is developed. Errors due to A/D quantization, coefficient (twiddle factor) rounding and scaling quantization are explicitly covered. A general expression for the relative RMS output error has been derived which is a function of the parameters associated with the desired realization. Certain of the parameters have been set to practical values and a simplified design procedure has been obtained. Finally, an example is given to show how to use the design procedure.

A discussion of the theoretical and simulation results is treated in Chapter 5. This chapter also contains a description of some ramifications of the theoretically derived expressions.

In Chapter 6, the conclusions that can be obtained from the research are summarized.

#### CHAPTER 2

# THE RESIDUE NUMBER SYSTEM AND ITS APPLICATION TO A FFT PROCESSOR

#### 2.1 <u>Residue Number System Concepts</u>

The RNS [1] is of particular interest because of the separable nature of the arithmetic. The arithmetic operations of addition and multiplication can be easily carried out using look-up tables [6]. In fact, using current technology, all the possible results of these arithmetic operations can be stored in high density ROMs.

A number in the RNS is represented by the L-tuple X =  $(x_1, x_2, \ldots, x_L)$  where  $x_i = X \mod m_i$ ; this is written  $x_i = |X|_{m_i}$ . If all the moduli,  $\{m_i\}$ , are relatively pairwise prime, the range of numbers that can be uniquely represented in residue code is equal to the product of all moduli

$$M = \prod_{i=1}^{L} m_i$$

(2.1)

.)

Thus, the RNS forms a ring of integers modulo M. If the RNS does not have a sufficient range of numbers to represent the result generated by arithmetic operation from a finite set of real integers, then the RNS will have overflow and the result will be a modulo M remainder of the true value.

In the RNS, binary operations of addition and multiplication, modulo M, between two numbers X and Y have the following property  $Z = \begin{bmatrix} X & o & Y \end{bmatrix}_M$

·12

$$Z|_{m_{i}} = z_{i} = |x_{i} \circ y_{i}|_{m_{i}}$$

$$(2.2)$$

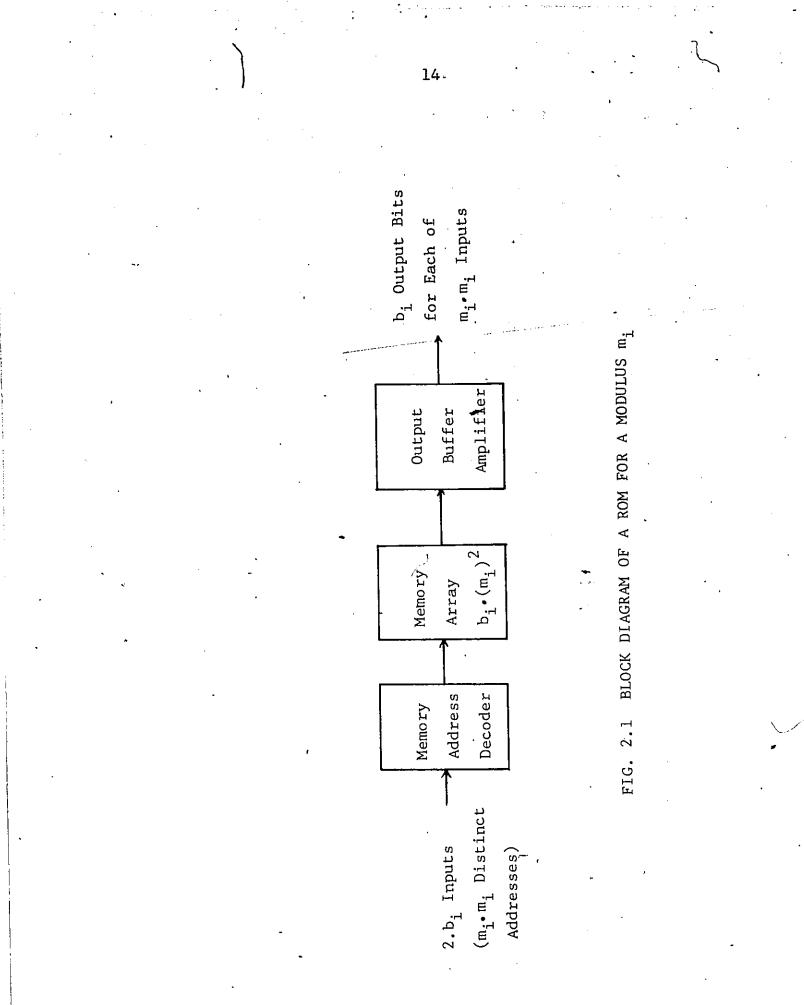

where  $o = + \text{ or } \cdot$ . In other words, the RNS does not have a carry mechanism and there is complete independence between operations on the residues. This separable nature of the arithmetic offers advantages to implementing multiplication and addition in a high speed parallel manner. Moreover, if the  $m_i$  are made small enough, then the results of operations, on all combinations of inputs, can be prestored in ROMs, and, by combining a sufficient number of rings, a viable dynamic range, M, for the number systems can be gene-This allows computations performed over a large rated. dynamic range to be realized, independently, in system's with much smaller dynamic ranges. Figure 2.1 shows a block diagram of a ROM for a modulus  $m_i$ . In order to generate the m<sub>i</sub> • m<sub>i</sub> possible input combinations (address), 2•b<sub>i</sub> input terminals are necessary at the memory address decoder, where '  $\mathbf{b}_{\mathbf{i}}$  is the number of bits required to represent the maximum integer,  $m_i - l$ , within the look-up tables of modulus  $m_i$ . Thus, if  $M = \prod_{i=1}^{n} m_i$ , then the memories required in terms of bits for the RNS is equal to  $\sum_{i=1}^{L} b_i \cdot m_i^2$ . The minimum memory requirements for various moduli have been discussed in [6].

The sign of numbers in the RNS is not explicitly shown. In general, the numbers in the range 0 to  $\frac{M}{2}$  - 1 are assigned to be positive, and the numbers in the range  $\frac{M}{2}$  to M-1 are assigned to be negative such that  $|x_i + y_i|_{m_i} = 0$  where

$y_i = |-X|_{m_i}$  and X denotes a positive integer. Since the rules of ordinary signed arithmetic will be preserved, there is no real need for an explicit knowledge of the sign of a number during arithmetic operations. For the signed RNS, the range of positive and negative integers is reduced to approximately one-half of the total possible range of the residue representation.

The division process for residue code is complicated. If we define scaling as division by a predetermined set of constants, then this restricted operation is much easier than general division. In order to scale efficiently, the scale factor or predetermined set of constants must be chosen to be a product of some of the moduli used in the RNS [1].

There have been many previous reports of high speed FFT realizations [16], [27], [34], however, these have used the binary number system in which to perform the required arithmetic operations. This invariably leads to a proliferation of binary adders and multipliers which have to be interconnected in a pipeline arrangement, for high throughput; a job made difficult by the radically different structure of each In using an array of ROMs, an extremely simple network. structure emerges that offers identical characteristics for any required operation and is inherently simple to pipeline. As an example, consider the problem of pipelining an array designed to compute the function  $Z = (a \cdot b) + (c \cdot d)$ . Figure 2.2 shows the array for one of the moduli in the system. The only control function required is a latch pulse. The

buffers are used to provide both power gain and delay. The delay allows the (i + 1)-th stage to capture data before the address lines of the i-th stage change. The system throughput rate is the inverse of the ROM access plus latch times. Conservatively 10 MHz. A further, hidden, advantage when using ROMs, is that binary operations with constants can be pre-calculated and stored in the ROM. This turns out to be important when designing scaling arrays [6], and leads to a significant hardware saving.

#### 2.2 The Fast Fourier Transform

The DFT pair of the complex N point sequence  $\{x(n)\}$ , is defined as

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk} \qquad k = 0, 1, \dots, N-1 (2.3)$$

and

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_{N}^{-nk} \qquad n = 0, 1, \dots, N-1 (2.4)$$

61

where  $j = \sqrt{-1}$ ,  $W_N = \exp(-j2\pi/N)$ , and  $\{X(k)\}$  are complex.

The FFT is simply an efficient method for computing the DFT. In fact, when N is a composite number, the N-point DFT can be computed as a collection of smaller DFT's in conjunction with additional coefficients commonly called twiddle factors [35]. If N =  $r^m$ , where r and m are positive integers, the factors of N are equal to r and the algorithm is called a radix-r algorithm. When an N-point DFT is computed using

a radix-r algorithm, a structure with m stages, where each stage includes N/r basic r-point transforms results. The basic forms of the resultant r-point transforms with DIT and DIF<sup>+</sup>are given by

$$x_{i+1}(k) = \sum_{n=0}^{r-1} x_i(n) (W_N^t)^n W_r^{nk}$$

(2.5)

and

$$x_{i+1}(k) = \sum_{n=0}^{r-1} x_i(n) W_r^{nk} (W_N^t)^k$$

, (2.6)

respectively, where  $\{x_i(n)\}$  denote the numbers at the input of the i-th stage, and  $(W_N^t)^n$ ,  $(W_N^t)^k$  are the appropriate twiddle factors.

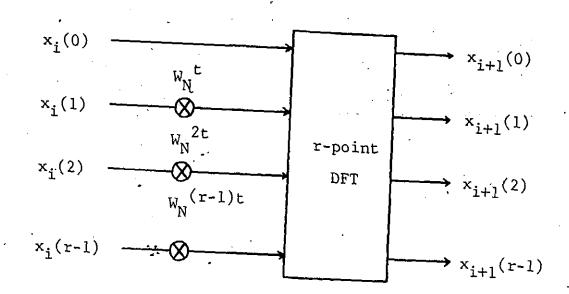

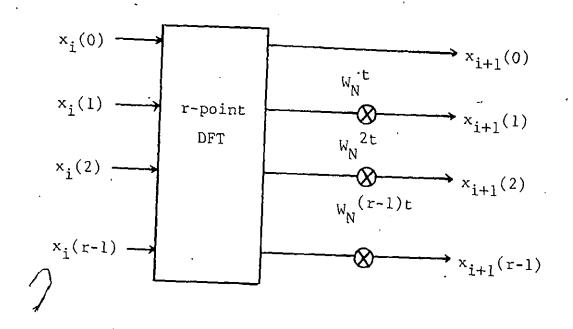

The basic calculation of the r-point transform, as shown in equation (2.5), can be decomposed into two steps. First the r-input points are multiplied by twiddle factors. Then the r-point DFT is computed. The above procedure is reversed for the DIF algorithm. Figures 2.3(a) and (b) show the simplified representations of the r-point transform DIT and DIF algorithms, respectively.

2.3 A ROM Oriented FFT Structure

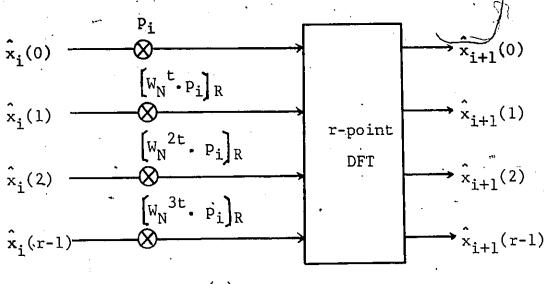

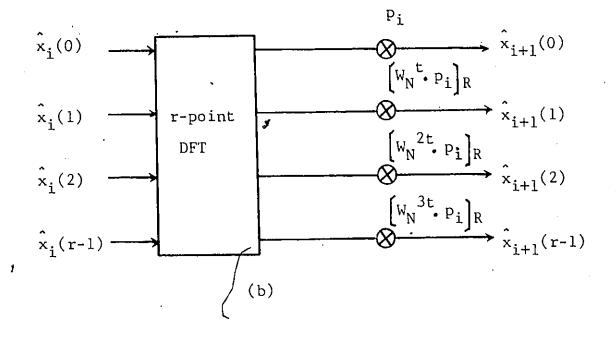

Since the RNS is an integer number system, all non-integer coefficients in the FFT, which include twiddle factors and non-trivial coefficients in the r-point DFT, must be converted to integers. These can be done by introducing integer conversion factors. Figure 2.4 shows the simplified integer

<sup>+</sup> The DIT (or DIF) algorithms are based on the decomposition of the DFT computation by forming successively smaller subsequences of the input (or output) sequence.

FIG. 2.3 SIMPLIFIED REPRESENTATION OF AN r-POINT TRANSFORM

a,

- (a) DIT ALGORITHM

- (b) DIF ALGORITHM

representations of r-point transform algorithms, where p<sub>i</sub> is the integer conversion factor for twiddle factors at the i-th stage, which may be varied from stage to stage. It should be noted that if there are non-trivial coefficients required in the r-point DFT, then another integer conversion factor is also needed. In Figure 2.4, the superscript "." denotes an integer value.

Without any loss of generality, we will assume that the binary number from the A/D converter is treated as an integer number; therefore, all the required arithmetic operations in the FFT can be computed using integer arithmetic, after introducing the integer conversion factors. In fact, the RNS concepts may be applied to the integer based FFT.

From Section 2.1, it is clear that the residue arithmetic can be efficiently implemented using table look-up ROM arrays, if the  $\{m_i\}$  are made small enough, and, by combining a sufficient number of moduli, a large dynamic range can also be generated. Thus, it is possible to have a ROM oriented FFT structure, if the number range of the RNS is sufficient for the dynamic range of the FFT. In practice, scaling operations are used to scale down the number within the limited range of the RNS.

In the RNS, scaling is difficult, because the digits do not convey any immediate information about the magnitude of the number. It is possible to scale fairly efficiently when the scale factor is a product of some of the moduli, but even in this case the hardware cost is fairly high [6]. If X is

(a)

FIG. 2.4 SIMPLIFIED INTEGER REPRESENTATION OF AN r-POINT TRANSFORM

- (a) DIT ALGORITHM

- (b) DIF ALGORITHM

21

the original number, K the scale factor, and Y, the scaled number, the scaling process can be represented by the following rational system,

$$X \simeq \frac{\hat{X}}{D} \quad \text{with} \quad \left| \hat{X} \right| \leq \frac{M}{2} - 1$$

$$Y = \frac{X}{K} \simeq \frac{\hat{X}}{D} \approx \frac{\left( \hat{X} \right)_{R}}{K} \qquad (2.7)$$

where  $\hat{X}$  is an integer with the denominator, D, to normalize its magnitude, and  $\left(\begin{array}{c} \right)_R$  denotes the integer round-off procedure. A viable scaling procedure requires that the scale factor must be pre-determined (no dynamic normalization is allowed) and scaling operations must be kept to a minimum. In order to satisfy both requirements, we will, in general, perform several exact arithmetic operations before scaling by a pre-determined constant. In this case, the dynamic range of the numerator may grow considerably after each operation. In order to preserve the rational system, it is necessary to increase the denominator to match the range growth of the numerator when cascading multiplications. Since the denominators are known a priori at every stage, one needs only to analyze the operations performed on the numerator. One can, therefore, consider that the number system is purely integer.

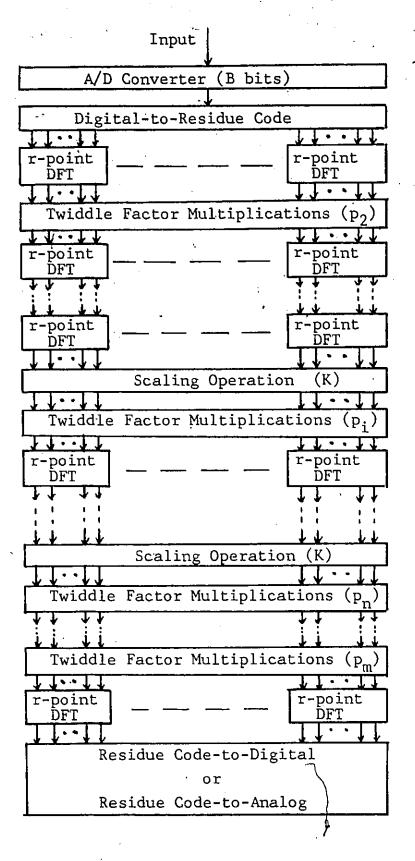

Figure 2.5 shows a conceptual block diagram of the proposed FFT structure with the indication of some parameters, which will be discussed in the next section. From Figure 2.5, it is seen that the analog input must be first converted

. **.**

FIG. 2.5 CONCEPTUAL BLOCK DIAGRAM OF A FFT PROCESSOR

to binary digital form, and then to residue code. The number of r-point DFT's required depends on how the FFT is realized.

## 2.4 Identification of Design Parameters

In order to construct a ROM oriented FFT processor, all the related design parameters have to be properly identified. From the proposed structure, as shown in Figure 2.4, some of design parameters are explicitly indicated. There are, however, several other parameters which can not be directly shown in the proposed structure. The importance of each parameter will be discussed in the following.

The most important parameter of the proposed structure is the number range, M, of the RNS. This parameter can also be recognized as the maximum word length for a conventional binary number implementation. In fact, the memory requirements for the ROM oriented FFT structure depend mainly on the value of M.

The A/D converter width in bits, B, is the number of bits used to represent the input data. To have accurate representations of analog input, a large number for B is required. Since this corresponds to a larger magnitude of the digitized input data, and the range of the RNS is limited, a compromise between the accuracy and the magnitude of the input data must be taken into consideration.

The integer conversion factor, p<sub>i</sub>, is used to convert the non-integer coefficients into integers. Without introducing this factor, it is not possible to have an integer based FFT. The consideration given for the A/D converter quantization bits also hold true here.

Scaling is important, since in practice we are not interested in computations modulo M, rather we require to approximate to calculations carried out in the infinite field of real (or complex) numbers. For a fixed number range, a smaller scale factor requires more frequent scaling operations. The choice of the scale factor results in different scaling distributions. In other words, we can use either larger scale factor with less scaling operations or smaller scale factor with more scaling operations.

In addition to the above mentioned parameters, there is an inherent parameter of the FFT, which is the number growth at each stage. Once number growth has been determined, it can also be used to establish not only scale factor but also the manner in which gain in number growth is distributed through the system.

### CHAPTER 3

### FFT PROCRSSOR CONSIDERATIONS

## 3.1 Optimal Radix Determination

Since integer based arithmetic is used to perform the required arithmetic operations in the FFT, and exact integer results are always obtained from the basic calculations of addition, subtraction and multiplication in the RNS, then the results at the output of each BCU in the FFT must be retained with full accuracy. As multiplication results are retained to full accuracy, the magnitude of numbers at subsequent stages of the FFT increase very rapidly due to the cascaded integer multiplications. In the RNS, the range of numbers that can be uniquely represented in residue code is equal to the product of all moduli, and hence all numbers must be properly scaled within the range of this number system to prevent overflows.

In terms of using integer arithmetic, we are interested in maximizing the ratio of the number of binary operations to the number of scaling operations. This is especially important when the RNS is used, as scaling operations are cumbersome to implement in hardware [6]. Since the magnitude of numbers in the FFT are increasing mainly due to multiplications, then a radix-r FFT having a minimum number of cascaded multiplications is obviously desirable from a scaling. point of view.—In the FFT, the occurrance of multiplications are due to internal multiplications in the r-point DFT and

twiddle factor multiplications. When the radix of the FFT is either 2 or 4, there will be no non-trivial internal coefficients requiring multiplication operations in the r-point DFT. This results from the fact that  $W_r^{nk}$  in equations (2.5) and (2.6) equals  $0, \pm 1$ , or  $\pm j$  when r=2 or 4. It is thus apparant that 4 is the largest radix without internal multiplications occurring in the r-point DFT.

When the number of samples, N, is equal to a power of 2, the FFT may be realized using radices of  $2^k$ , where k is a non-negative integer. Table 2.1 shows the number of cascaded multiplications for various values of r and N. The analytic relationships are shown in the last column. Here we assume that the 8 and 16-point DFT's in the basic calculations of the radix-8 and -16 FFT's are computed in the same manner as small-N WFTA's described by Silverman [15],[36]. Thus Table 2.1 has been generated on the basis that there is only one multiplication level within the r-point DFT for r=8 and 16. For radices of 2 and 4, the numbers shown in Table 2.1 represent the number of cascaded twiddle factors only; while for radices of 8 and 16, the numbers represent the sum of the cascaded twiddle factors and cascaded internal multiplications in the r-point DFT's.

From Table 2.1, it can be seen that the radices of 4 and 16 have the smallest number of cascaded multiplications, and thus the use of these radices will minimize the number of scaling operations required. In general, the hardware necessary to realize the BCU of a radix-16 FFT is much more NUMBER OF CASCADED NON-INTEGER MULTIPLICATIONS FOR RADICES OF 2, 4, 8 AND 16

TABLE 2.1

- 75

ネ

| T      | 2*     |                | (m-1) + m <sup>**</sup> | (m-1) + m <sup>**</sup> | trivial                                                        |

|--------|--------|----------------|-------------------------|-------------------------|----------------------------------------------------------------|

|        | ш 2*   | ו<br>E •       | (m-1)                   | (m-1)                   | ors are                                                        |

| 4096   | . 10   | <u>ب</u>       | ۲ .                     | , S                     | EFT there are two stages where the twiddle factors are trivial |

| 2048   | 6      | <u></u>        |                         |                         | the twi                                                        |

| 1024 . | ∞      | . 4            | · .                     |                         | es where                                                       |

| 512    | *~     |                | ú                       | <u></u>                 | two stao                                                       |

| 256    | 9      | ۳ <sup>۱</sup> |                         |                         | are<br>are                                                     |

| 128    | ى<br>ب |                |                         |                         | 4                                                              |

| 64     | 4      | 5              | <del>ر</del>            | `                       | T - + +                                                        |

| r<br>r | . 2    | 4              | œ                       | 16                      | )<br>4<br>1<br>1<br>1<br>1                                     |

- there is only one stage having these ÷, two stages Otherwise, are or integers, such as Ó, ±1, ±j. properties. In the radix-2 FFT, there ×

- The second term, m, is the number of cascaded internal multiplications in the r-point DFT's. \*\*

complex than for a radix-4 FFT. The choice between radix 4 or 16 from a speed and cost point of view depends upon the manner in which the FFT processor is realized. However, a radix-16 realization severly limits the viability of a processor due to the number of samples, N, that can be selected. Thus radix 4 is considered as the optimal realization radix, when the number of samples, N, is a power of 2.

When the number of samples is not a power of 2, a mixedradix FFT, prime-factor FFT or Winograd Fourier transform may be used. However, these algorithms have some disadvantages in the hardware implementations, although they may require less computation time than the radix-r FFT as far as the software implementations are concerned. The main disadvantage is that the basic calculation at each stage is different, which makes the hardware very difficult to be pipelined. Furthermore, the realizations for these algorithms are not flexible, and, in fact, they must be realized in a cascade form, which is also due to the different structure of basic calculation at each stage.

Now we can conclude that radix 4 is the optimal realization radix. If, however, the number of samples is not a power of 4, then we can append enough number of zeros to the original data, and still perform a radix-4 algorithm.

3.2 Number Growth

In this section, some properties of the radix-4 FFT will be examined. Specifically, the mean-square value and the maximum magnitude of numbers at the output of each stage will be determined. The mean-square bound, which is

independent of input data, can be determined exactly. While the maximum magnitude can be determined both theoretically and experimentally for the worst cases only.

3.2.1 Mean-square Bound

In order to analyze the RMS error in the radix-4 FFT, the mean square value at the output of each stage must first be known. It has been shown in [32] that the mean square value will increase by 2 for a DIT radix-2 FFT. In the following, we will derive the mean-square bound in a more generalized manner.

Applying Parseval's theorem to equation (2.3), one obtains

$$\sum_{k=0}^{N-1} \left| X(k) \right|^2 = N \sum_{n=0}^{N-1} \left| x(n) \right|^2$$

or

$$\frac{1}{N} - \sum_{k=0}^{N-1} |X(k)|^2 = N \cdot \frac{1}{N} - \sum_{n=0}^{N-1} |x(n)|^2 \quad (3.1)$$

Equation (3.1) indicates that the mean-square value of the result is N times the mean-square value of the initial sequence. Since there are m similar stages for a radix-r FFT ( $N=r^{m}$ ), we can show that the mean square value will increase by r at each stage, as follows.

Letting  $y_i(n) = x_i(n)(W_N^t)^n$  in equation (2.5), one obtains

$$x_{i+1}(k) = \sum_{n=0}^{r-1} y_i(n) W_r^{nk}$$

(3.2)

Equation (3.2) can be recognized as an r point DFT with  $y_i(n)$  and  $x_{i+1}(k)$  as the input and output, respectively. Applying Parseval's theorem again, one obtains

$$\sum_{k=0}^{r-1} \left| x_{i+1}(k) \right|^2 = r \sum_{n=0}^{r-1} \left| y_i(n) \right|^2$$

(3.3)

Since

$$|\mathbf{y}_{i}(n)|^{2} = |\mathbf{x}_{i}(n)|^{2} |(\mathbf{W}_{N}^{t})^{n}|^{2}$$

and  $|(W_N^t)^n|^2 = 1$ , then equation (3.3) becomes

$$\sum_{k=0}^{r-1} |x_{i+1}(k)|^2 = r \sum_{n=0}^{r-1} |x_i(n)|^2$$

(3.4)

Equation (3.4) can be generalized as

$$\frac{1}{N} \sum_{k=0}^{N-1} |x_{i+1}(k)|^2 = r \cdot \frac{1}{N} \sum_{n=0}^{N-1} |x_i(n)|^2 (3.5)$$

Equation (3.5) shows that the mean-square value will increase by r at the output of each stage for a radix-r DIT algorithm. This property also holds for a radix-r DIF algorithm, and the proof is shown in Appendix A. 3.2.2 Theoretical Worst Case Upper Bound

In the proposed FFT processor the upper bound of number growth must be derived in order to be able to avoid overflow problems. Specifically, one would like to know the maximum magnitude of both the real and imaginary parts that occurs at the output of each stage.

We now consider the radix-4 DIT algorithm. When r=4 in equation (2.5), one obtains

$$x_{i+1}(k) = \sum_{n=0}^{3} x_i(n) (W_N^t)^n W_4^{nk}$$

(3.6)

From equation (3.6) one can compute a worst case upper bound for the number growth at each stage. Recognizing that

$$(W_N^t)^n = \cos \frac{2\pi nt}{N} - j \sin \frac{2\pi nt}{N}$$

(3.7)

one can rewrite equation (3.6) as

$$x_{i+1}(k) = \sum_{k=0}^{3} \left\{ (\operatorname{Re}(x_{i}(n))\cos\frac{2\pi nt}{N} + \operatorname{Im}(x_{i}(n))\sin\frac{2\pi nt}{N}) + j(\operatorname{Im}(x_{i}(n))\cos\frac{2\pi nt}{N} - \operatorname{Re}(x_{i}(n))\sin\frac{2\pi nt}{N}) \right\} W_{4}^{nk} (3.8)$$

where  $Re(\cdot)$  and  $Im(\cdot)$  denote the real and imaginary parts of the terms enclosed, respectively. Since, for a 4-point DFT, each output point (real or imaginary part) is always computed by adding or subtracting 4 input points, then, from equation (3.8), one obtains

$$\max\left\{ \left| \operatorname{Re}(x_{i+1}(k)) \right|, \left| \operatorname{Im}(x_{i+1}(k)) \right| \right\} \leq \\ \max\left\{ \left| \operatorname{Re}(x_{i}(n)) \right|, \left| \operatorname{Im}(x_{i}(n)) \right| \right\} \sum_{n=0}^{3} \left\{ \left| \cos \frac{2\pi \operatorname{nt}}{N} \right| + \left| \sin \frac{2\pi \operatorname{nt}}{N} \right| \right\}$$

or

$$\frac{\operatorname{Max}\left\{\left|\operatorname{Re}(x_{i+1}(k))\right|, \left|\operatorname{Im}(x_{i+1}(k))\right|\right\}}{\operatorname{Max}\left\{\left|\operatorname{Re}(x_{i}(n))\right|, \left|\operatorname{Im}(x_{i}(n))\right|\right\}} \leq \sum_{n=0}^{3} \left\{\left|\cos\frac{2\pi nt}{N}\right| + \left|\sin\frac{2\pi nt}{N}\right|\right\}$$

(3.9)

Similarly, one can show (see Appendix A) that the theoretical worst case upper bound associated with the DIF algorithm is given as

$$\frac{\operatorname{Max}\left\{\left|\operatorname{Re}(x_{i+1}(k))\right|, \left|\operatorname{Im}(x_{i+1}(k))\right|\right\}}{\operatorname{Max}\left\{\left|\operatorname{Re}(x_{i}(n))\right|, \left|\operatorname{Im}(x_{i}(n))\right|\right\}} \leq 4 \left\{\left|\cos\frac{2\pi \operatorname{kt}}{\operatorname{N}}\right| + \left|\sin\frac{2\pi \operatorname{kt}}{\operatorname{N}}\right|\right\}$$

(3.10)

It is seen from (3.9) and (3.10) that the theoretical worst case upper bound depends only on the magnitudes of twiddle factors which are themselves independent of the magnitude of the input sequence. It is also seen that the upper bound associated with the DIF algorithm depends only on one particular twiddle factor, while it depends on all twiddle factors within one basic 4-point transform for the DIT algorithm. The upper bounds computed according to (3.9) and (3.10) are given in Table 3.1 for N ranging from 64 to 4096. From Table 3.1 it can be seen that the upper bound

# TABLE 3.1a

THEORETICAL WORST CASE UPPER BOUND OF THE NUMBER GROWTH AT EACH STAGE OF A RADIX-4 DIT FFT

| Stage No.<br>N | 1 | 2       | 3     | 4     | 5     | 6     |

|----------------|---|---------|-------|-------|-------|-------|

| . 64 .         | 4 | 5.027   | 5.042 |       |       |       |

| 256            | 4 | - 5.027 | 5.042 | 5.058 |       |       |

| 1024           | 4 | 5.027   | 5.042 | 5.058 | 5.058 |       |

| 4096           | 4 | 5.027   | 5.042 | 5.058 | 5.058 | 5.058 |

## TABLE 3.1b

THEORETICAL WORST CASE UPPER BOUND OF THE NUMBER GROWTH AT EACH STAGE OF, A RADIX-4 DIF FFT

₹...

| ;              |                 |       |       |       |       |   |

|----------------|-----------------|-------|-------|-------|-------|---|

| Stage No.<br>N | l ·             | 2     | 3     | 4     | 5     | 6 |

| 64             | 5.657           | 5.657 | 4     |       |       |   |

| 256            | 5.657           | 5.657 | 5.657 | 4     |       |   |

| 1024           | •5 <b>.</b> 657 | 5.657 | 5.657 | 5.657 | 4     |   |

| 4096           | 5.657           | 5.657 | 5.657 | 5.657 | 5.657 | 4 |

on number growth for a given stage is independent of the number of samples, N. In addition, for any given value N, the upper bound associated with the DIT algorithm is seen to increase as the number of stages increase until, for all practical purposes a maximum value is reached, and no worst case upper bound for number growth greater than 5.058 was seen to occur. For the case of the DIF algorithm, the upper bound at each stage is kept to a constant value, 5.567, except at the last stage where it is equal to 4. The particular value, 5.567, is, in fact, due to a twiddle factor of angle  $\pi/4$  which exists at every stage, but not at the last stage. At the last stage, the twiddle factors are equal to 1 and hence the upper bound is equal to 4.

If we compare the upper bounds between the DIT and DIF algorithms, from Table 3.1(a) and (b), we see that overall number growth is smaller for the DIT algorithm. Therefore, in the following, we will only consider the radix-4 DIT algorithm. A detailed radix-4 DIT basic calculation is shown in Figure 3.1.

Scaling factors determined from the theoretical worst case bound will definitely ensure the overflows do not occur but at the same time unrealistically constrain the dynamic range of the hardware.

3.2.3 Experimental Worst Case Upper Bound

Besides the theoretical upper bound developed in section 3.2.2 it is desirable to experimentally determine the number growth that is associated with commonly occurring input sequences,

. (

# FIG. 3.1 RADIX-4 DIT BASIC CALCULATION

in order to obtain a more realistic value.

To facilitate the experimental determination of number growth, a radix-4 DIT FFT program was written and executed on a large scale general purpose digital computer. The number of samples, N, Was chosen to be 1024. Three different sets of input sequences, including uniformly distributed pseudo random numbers, sine waves plus pseudo random number, and speech signals were used.

In one set of experiments, the inputs were comprised of pseudo random numbers for both the real and imaginary components. These components were uncorrelated and fell within the set (-1,1) for the first case, and (0,1) for the second case. The experimental upper bound on number growth determined for these two cases is shown in rows one and two, respectively, of Table 3.2.

In the second set of experiments two sine waves plus pseudo random numbers were used as the input sequences. The general form of the input sequence is given by

$a(n) + 0.5 \sin \frac{n\pi}{256} + 0.25 \sin \frac{n\pi}{128} + 0.25 \sin \frac{n\pi}{64}$  (3.11)

where in the first case  $\{a(n)\}\$  are pseudo random numbers lying in the range -0.5 < a(n) < 0.5 and in the second case pseudo random numbers lying in the range 0 < a(n) < 1. The experimental upper bound on number growth associated with these two cases are shown in rows three and four, respectively, -of Table 3.2. TABLE 3.2

SIMULATION STUDY OF WORST CASE UPPER BOUND OF THE NUMBER GROWTH AT EACH STAGE OF A RADIX-4 DIT FFT ),

٠ ٢.

| 5                       | 2.62 | 4.04          | . 3.95  | 4.04 | 4,00  |

|-------------------------|------|---------------|---------|------|-------|

| 4                       | 2.74 | 3 <b>.</b> 98 | 3.78    | 3.98 | .4.01 |

| m                       | 2.72 | . 3.79        | 3.35    | 3.79 | 3.32  |

| . 2                     | 2.93 | 3.64          | 3.04    | 2.59 | 2.95  |

|                         | 3.97 | 3.98          | 3.17    | 3.37 | 2.66  |

| Stage No.<br>Input Type |      | 7             | °.<br>M | 4    |       |

The number growth associated with typical speech waveforms was also investigated. The corresponding upper bound on number growth is shown in the fifith row of Table 3.2.

Each of the experiments delineated in Table 3.2 were repeated sixty times. The upper bounds shown in Table 3.2 represent  $M + 3\sigma$ , where M and  $\sigma$  are the mean values and standard deviations for the samples generated, respectively.

From Table 3.2 it can be seen that an experimentally determined upper bound on number growth equal to 4 is quite reasonable for the input sequences considered.

## 3.3 Quantization Error Sources

The subject of error in the FFT has been reported in a ... number of papers. Error associated with the radix-2 FFT floating-point arithmetic have been analyzed in [37]. The error problems of FFTs using fixed-point arithmetic were first discussed by Welch [32], where different methods to avoid overflow were also examined. Recently, Brigham and Cecchini [33] developed a nomogram for determining fixed-point FFT system dynamic range. These papers were concerned primarily with the error characteristics of radix-2 FFT's. There are quantization problems associated with the proposed RNS implementation that have not been fully treated in the literature.

When the radix-4 FFT is implemented using the RNS, three forms of quantization errors, A/D converter quantization, coefficient rounding and scaling errors are presented. Strictly speaking, there are several different error sources other than A/D quantization error in an A/D converter, such as

saturation and aperture errors [38], [39]. Since the input to the A/D converter can be properly adjusted, quantization error is usually considered to be the dominant one. The coefficient rounding error is due to finite precision (or integer) representations of twiddle factors. The scaling error is introduced by scaling to keep the data within the limited dynamic range.

### CHAPTER 4

A DESIGN PROCEDURE FOR A FFT PROCESSOR

4.1 Design Criteria

In the proposed FFT structure, overflow is not tolerable in the RNS. In section 2.4, all the design parameters associated with the proposed processor have been identified. Further, the number growth at each stage in the FFT has been studied. Therefore when the number range is fixed, it is always possible to determine the rest of the parameters using trial and error methods to avoid overflows. However, only

considering the overflow problem is not sufficient to obtain an efficient design. In fact, the arbitrary choice of parameters may lead to a waste of memory requirements.

It is well-known that when digital signal processing elements are implemented with hardware, errors due to finite word length always exist. In order to achieve an acceptable level of error for some chosen word length, the characteristics of these errors must be known. In this thesis, we will consider the relative RMS error at the output of the FFT processor as the design criterion.

4.2 <u>General Design Parameter Relationships</u>4.2.1 Statistical Error Models

In this section quantization errors associated with A/D conversion, twiddle factors and scaling operations are considered. In order to determine their effects on a FFT processor, it is first necessary to establish the error models being used

to characterize each source of error.

A/D quantization error model

There are a number of different types of error that may be introduced by an A/D converter [38], [39].

Errors associated with quantization and saturation are the most common types. As the input level can always be adjusted to minimize saturation effects, only quantization error will be considered here.

If sampled data is represented by B bits, including the sign bits, and the input signal falls within the range  $\frac{+}{-}$  U then the converter step size, Q, is equal to

$$Q = \frac{U}{2^{B-1}} \tag{4.1}$$

It is noted that Q = 1 in the integer number system. When the quantization noise is assumed to be uniformly distributed with zero mean value, the mean and variance of the converter quantization error have been shown [39] to be

$$\overline{e_Q} = 0, \quad \overline{e_Q^2} = \frac{1}{12} \quad Q^2 = \frac{1}{12}$$

(4.2)

The statistical assumptions have been considered adequate to represent quantization error, even though correlation effects have been neglected, because for practical values of B the magnitude of the quantization error introduced by the converter, when compared with twiddle factor and scaling errors, is small. 2. Twiddle factor error model

In the proposed realization of the FFT processor, the error associated with the integer representation of the twiddle factor must be considered. An integer conversion factor, p<sub>i</sub>, must be introduced as shown in Figure 2.4.

In the ROM oriented implementation envisaged, the integer conversion factor,  $p_i$ , for the twiddle factors, must be predetermined and the integer representations of the twiddle factors stored in ROMs. The error associated with the integer conversion of a twiddle factor, c, is defined as

$$e_{I} = Re(e_{I}) + j Im(e_{I})$$

$$= p_i c - \left( p_i c \right)_R$$

$$= (p_i \operatorname{Re}(c) - [p_i \operatorname{Re}(c)]_R) + j (p_i \operatorname{Im}(c) - [p_i \operatorname{Im}(c)]_R)$$

(4.3)

1.43

where  $\left(\begin{array}{c}\right)_{R}$  denotes the integer round-off procedure. The round-off procedure is such that the errors  $\text{Re}(e_{I})$  and  $\text{Im}(e_{I})$  are uniformly distributed in the range (-0.5, 0.5) and thus

and

$\overline{e_{I}} = 0$

$$\frac{|e_{I}|^{2}}{|e_{I}|^{2}} = \frac{1}{(\text{Re}(e_{I}))^{2}} + \frac{1}{(\text{Im}(e_{I}))^{2}} = \frac{1}{6} \qquad (4.4)$$

3. Scaling error model

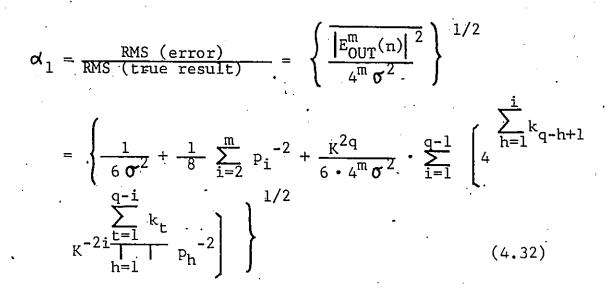

In the ROM oriented implementation considered, the magnitude of the numbers that occur at each stage must be known. The study of number growth given in section 3.2.3 allows one to choose a scale factor capable of constraining the number growth to a desired value.