# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1988

## A Unix based VLSI design workstation.

Alger W. K. Yeung University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Yeung, Alger W. K., "A Unix based VLSI design workstation." (1988). *Electronic Theses and Dissertations*. 858.

https://scholar.uwindsor.ca/etd/858

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# **;**

### National Library of Canada

Canadian Theses Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada

Service des thèses canadiennes

ç,

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

NOTICE

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

42

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

AVIS

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé, ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, tests publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

ana

# A Unix Başed VLSI Design Workstation

by

Alger W.K. Yeung

ł

F

15

٩<sub>Y</sub>

Ð

<u>e</u>

A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

> Windsor, Ontario January, 1988

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

٤,

43.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission. L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-43783-9

### Abstract

As VLSI technology evolves the complexity of the design process is contantly increasing. The existence of a powerful, easy-touse, and flexible VLSI design, workstation is essential if one is to successfully design a complex VLSI circuit. This thesis deals with the design of a VLSI workstation based on the DEC VAXstation II/GPX minicomputer operating in an Ultrix (Unix) and X-Window environment.

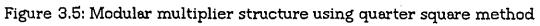

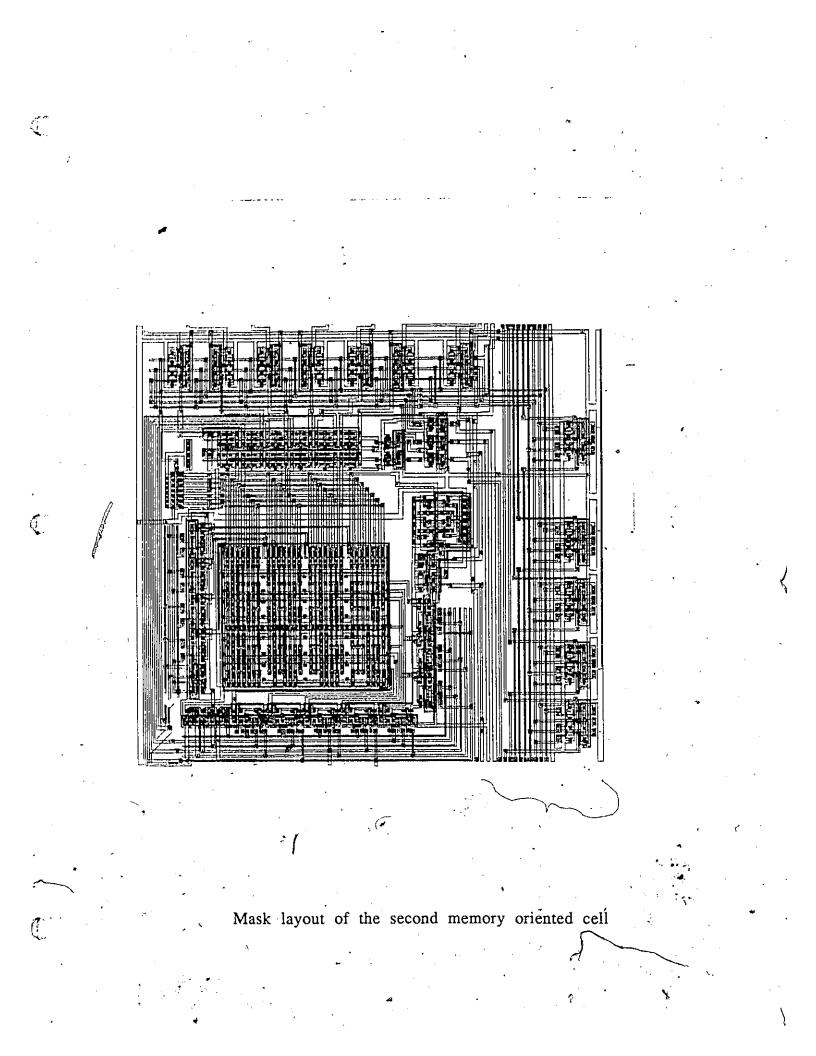

A special silicon compiler called Memory Oriented Silicon Compiler (MOSC) has been developed by the author and is available on the workstation together with a number of utility programs and two public domain programs. The public domain programs, Electric · and Relax2, have been modified and tailored to interact with MOSC in the Ultrix and X-Window environment. A full-custom hierarchical VLSI design methodology has also been identified in order to ensure that the VLSI design tools can be used effectively. A number of circuit designs have been carried out to illustrate the capabilities of the workstation. The MOSC silicon<sup>¬</sup> compiler is an application specific CAD tool. It was developed in order to afford the designer a simple manner for exploiting Residue Number System concepts and implementing pipelined memory oriented structures for digital signal processing applications. The MOSC program is capable of synthesizing 5-bit modular adders, subtractors, multipliers and constant operators in an integrated manner with the Electric design system. The utility programs developed include plotting routines, drivers for graphic

iii

devices, and a file format translator that allows the exchange of files with other VLSI design software available in the VLSI Research Laboratory.

The software developed and subsequently implemented on the VLSI design workstation has proven to be powerful and easy-to-use tool for designing VLSI circuits.

iv

### Acknowledgments

The author would like to acknowledge the guidance and supper provided by Dr. W.C. Miller and Dr. G.A. Jullien. The ideas and suggestions by other member of the VLSI Research Group were . also-greatly appreciated.

| Table of Contents                                                                                                                                   | •                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Abstract                                                                                                                                            | iii               |

| Acknowledgments                                                                                                                                     |                   |

| Table of Contents                                                                                                                                   | • V               |

|                                                                                                                                                     | V1                |

| List of Figures                                                                                                                                     | vii               |

| List of Tables                                                                                                                                      | viiir             |

| I. Introduction                                                                                                                                     | 1                 |

| II. A Complete VLSI Design Environment                                                                                                              | 9                 |

| A. Morphology of VLSI Design                                                                                                                        | 10                |

| B. Role of Silicon Compiler                                                                                                                         | . 29              |

| III. A Special Class of Silicon Compiler                                                                                                            | 32                |

| A. General Survey of Silicon Compilers                                                                                                              | 32                |

| B. Residue Number System and RNS Arithmetic Oper                                                                                                    | rations 36        |

| C. Memory Oriented Structure for RNS Operations                                                                                                     | 40                |

| D. Hardware Realization of RNS Adder and Multiplier                                                                                                 |                   |

| E. Implementation of the Silicon Compiler                                                                                                           | 51                |

| F. Software Development Environment                                                                                                                 | 59                |

| G. Design Examples of MOSC                                                                                                                          | 62                |

| IV. Results and Discussion                                                                                                                          | 70                |

| V. Conclusion                                                                                                                                       | 80                |

|                                                                                                                                                     | 00                |

| References                                                                                                                                          | 84                |

| Bibliography                                                                                                                                        | . 96              |

| Dionography                                                                                                                                         | .86               |

| Appendix I: Ultrix, windowing, and communication fa                                                                                                 | cilities 87 ·     |

| Appendix II: Electric design environment                                                                                                            | 109               |

| Appendix III: Circuit designs and simulations                                                                                                       | 124               |

|                                                                                                                                                     | 145               |

| Appendix IV: Graphic SPICE manual                                                                                                                   | 1 - 7 (1          |

| Appendix V: Macro functions                                                                                                                         | 179               |

| Appendix V: Macro functions<br>Appendix VI: Plotting facilities                                                                                     | 187               |

| Appendix V: Macro functions<br>Appendix VI: Plotting facilities<br>Appendix VII: ECIFIN/DCIFIN translator                                           | 187<br>208        |

| Appendix V: Macro functions<br>Appendix VI: Plotting facilities                                                                                     | 187               |

| Appendix V: Macro functions<br>Appendix VI: Plotting facilities<br>Appendix VII: ECIFIN/DCIFIN translator<br>Appendix VIII: Program listing of MOSC | 187<br>208<br>216 |

| Appendix V: Macro functions<br>Appendix VI: Plotting facilities<br>Appendix VII: ECIFIN/DCIFIN translator<br>Appendix VIII: Program listing of MOSC | 187<br>208<br>216 |

*L* -

# List of Figures

| Figure | 1.1: VLSI Design facilities in the VLSI Research Laboratory | 3,              |

|--------|-------------------------------------------------------------|-----------------|

|        | 1.2: Research activities involved in the project            | 5               |

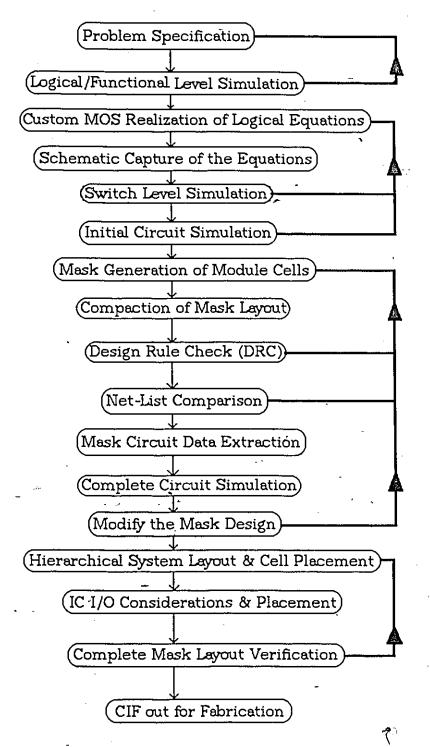

| Figure | 2.1: Full-custom hierarchical VLSI design methodology       | 11              |

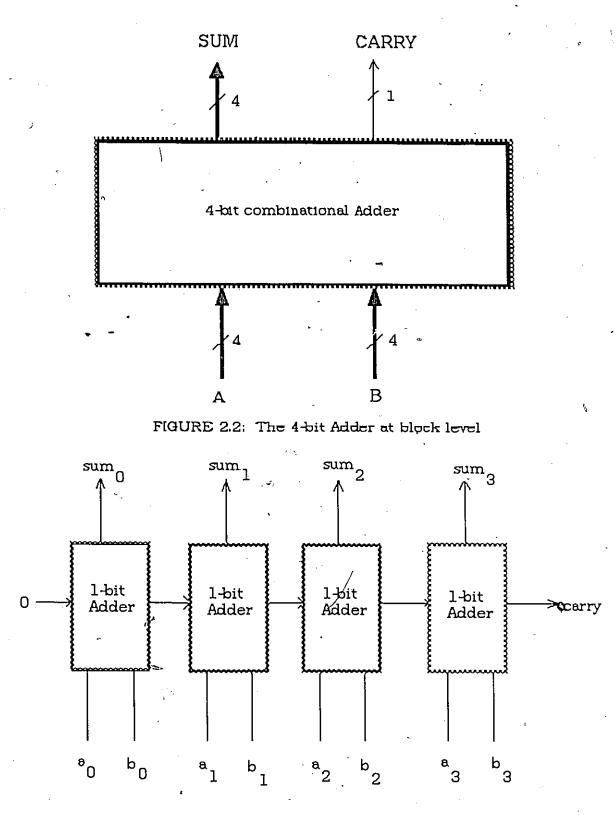

| Figure | 2.2: The 4-bit adder at block level                         | 1-3             |

|        | 2.3: The 4-bit adder at sub-block level                     | 13              |

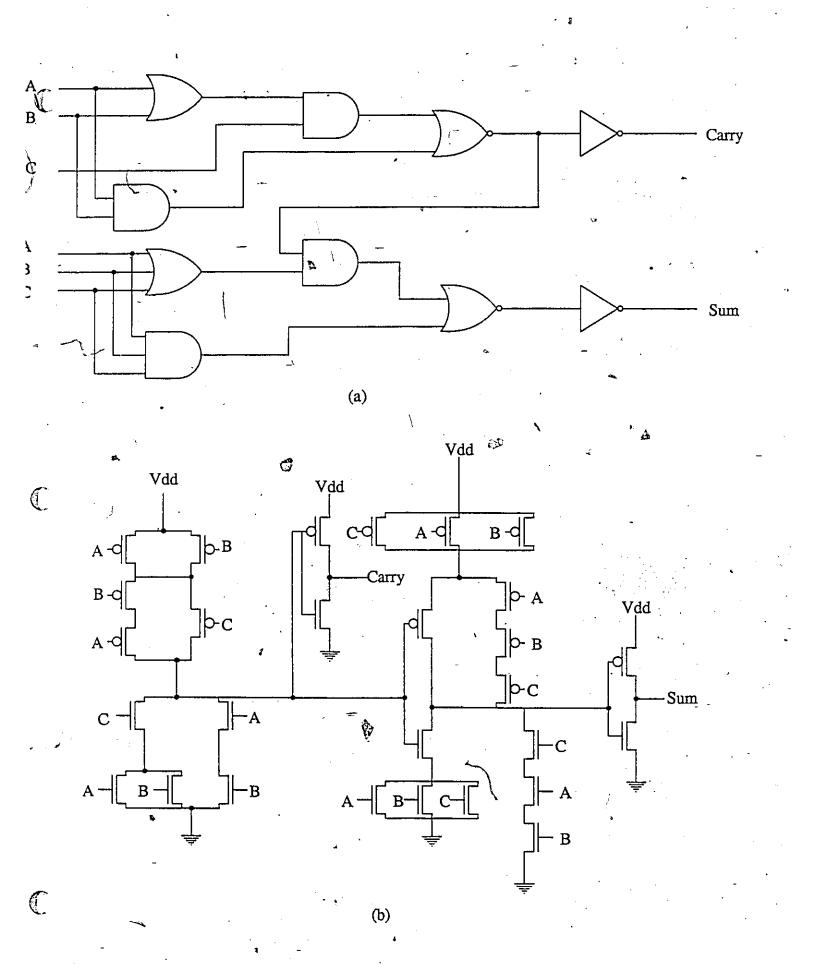

| Figure | 2.4: (a) Gate-level schematic capture of 1-bit adder        | 16              |

|        | (b) Transistor-level schematic capture of 1-bit adder       |                 |

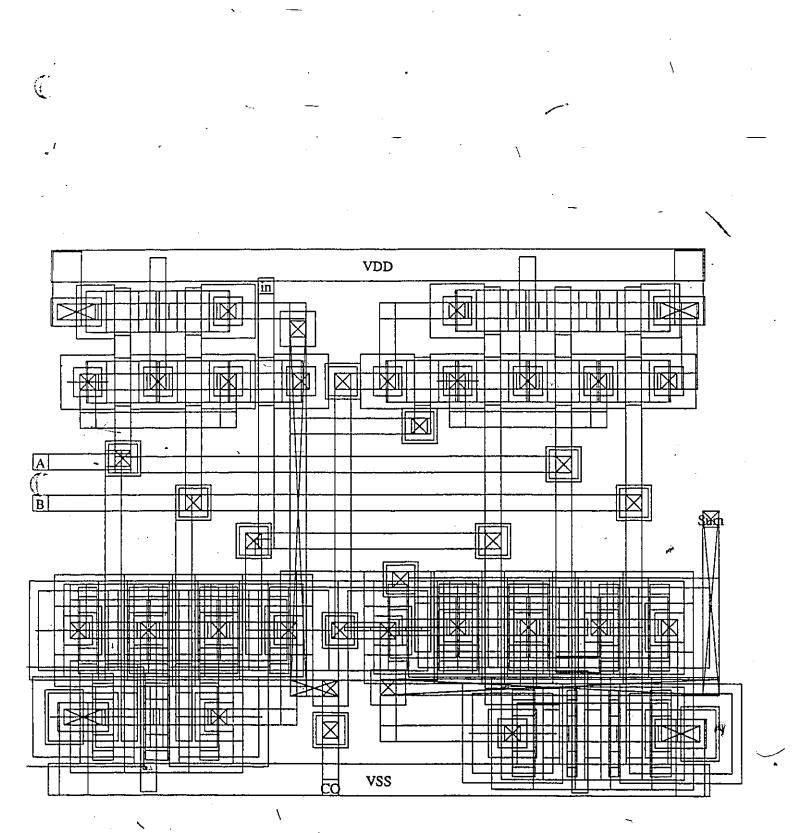

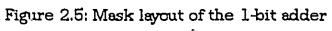

| Figure | 2.5: Mask layout of the 1-bit adder                         | 20              |

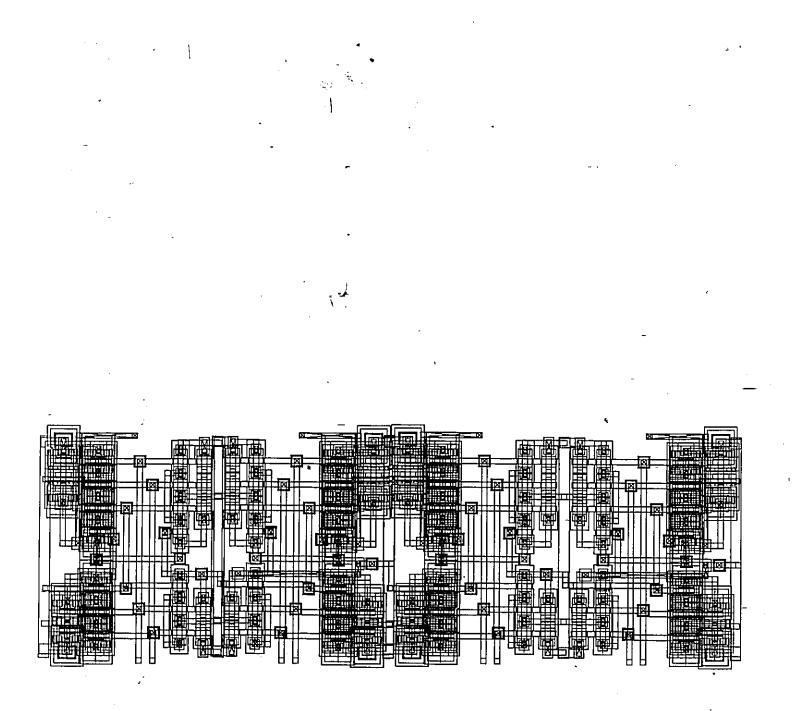

| Figure | 2.6: Complete mask layout of ripple carry adder             | 24              |

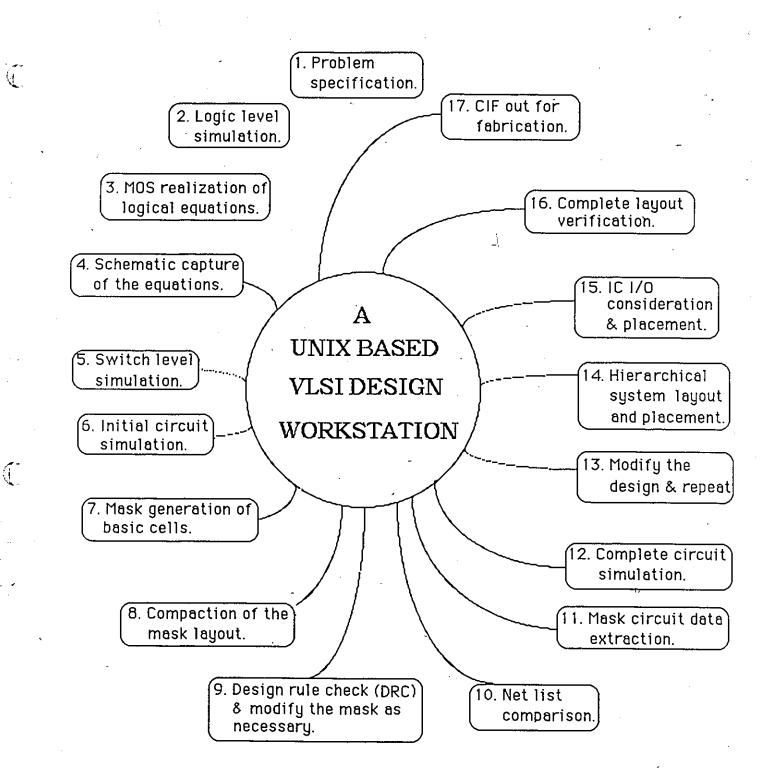

| Figure | 2.7: Relationship between the methodology and the           |                 |

|        | workstation                                                 | 26              |

| Figure | 2.8: Schematic diagram for transmission gate XOR circuit    | 2.8             |

| Figure | 3.1: Major components in closed RNS operations              | 41              |

| Figure | 3.2: A typical ROM structure                                | 42              |

| Figure | 3.3: Memory oriented structure for RNS operations           | 45              |

| Figure | 3.4: Modular 5-bit RNS adder                                | 45              |

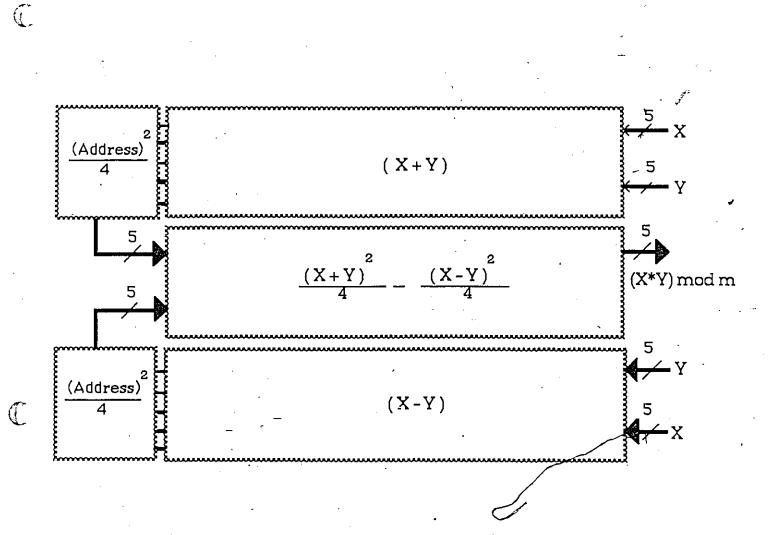

| Figure | 3.5: Modular multiplier structure using quarter square      |                 |

|        | method                                                      | 50              |

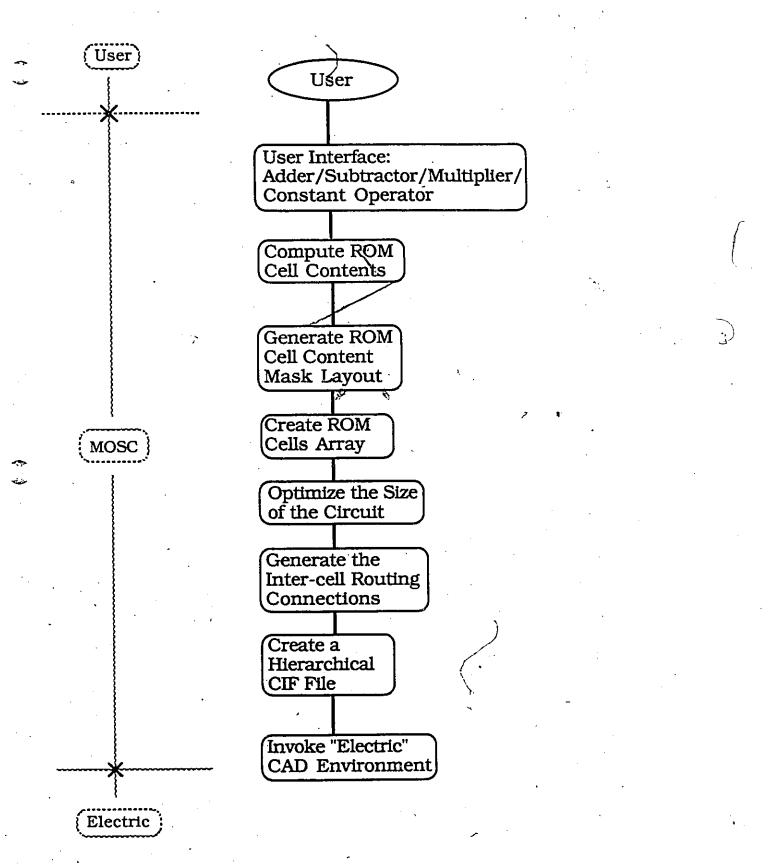

| Figure | 3.6: MOSC process structure                                 | 53 <sup>.</sup> |

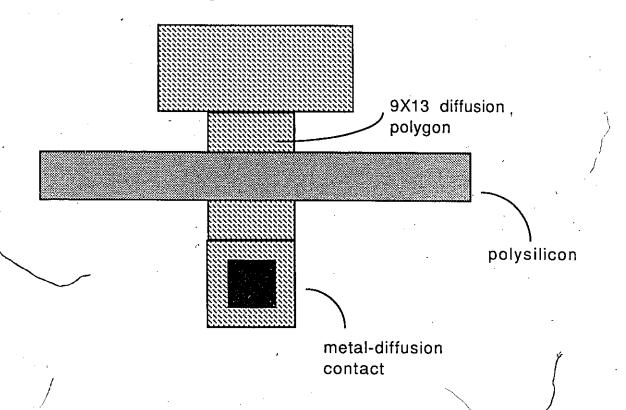

| •      | 3.7: Detail structure of the first memory cell              | 54              |

| Figure | 3.8: "1" bit transistor                                     | 55              |

| Figure | 3.9: Flow chart of the MOSC silicon compiler                | 57              |

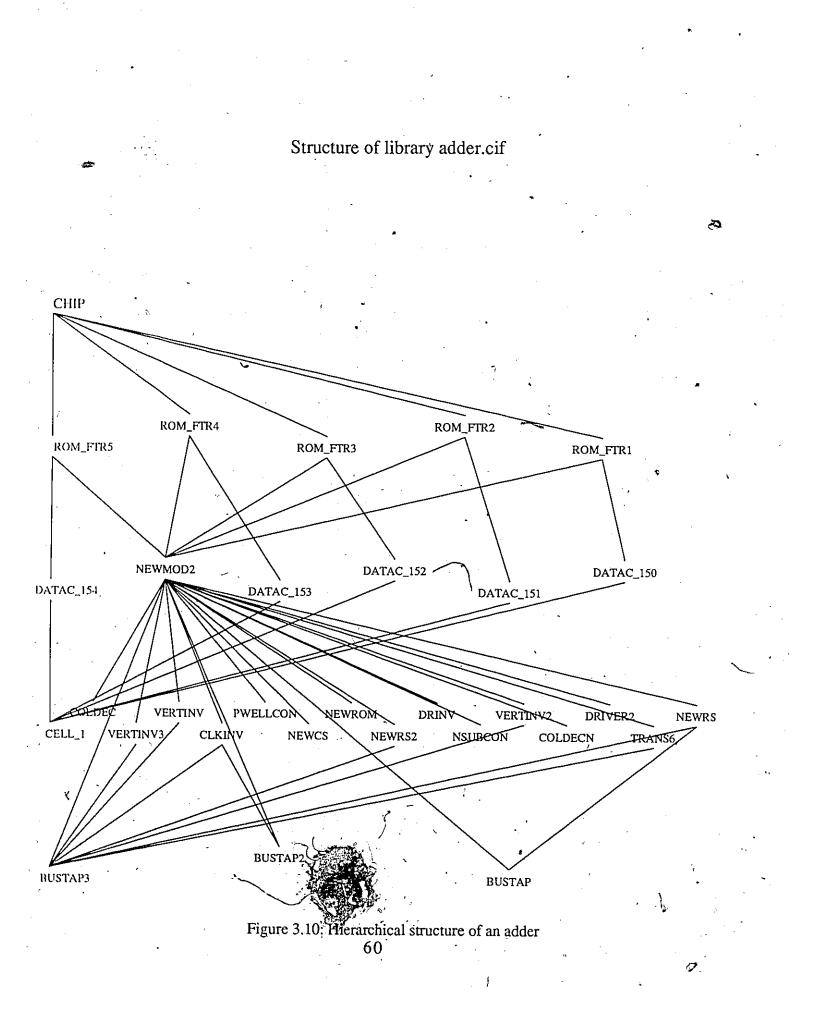

|        | 3.10: Hierarchical structure of an adder                    | 60              |

| -      | 3.11: Command file for creating a RNS multiplier.           | 62              |

| Figure | 3.12: Input example of a 4-adder to MOSC                    | 63              |

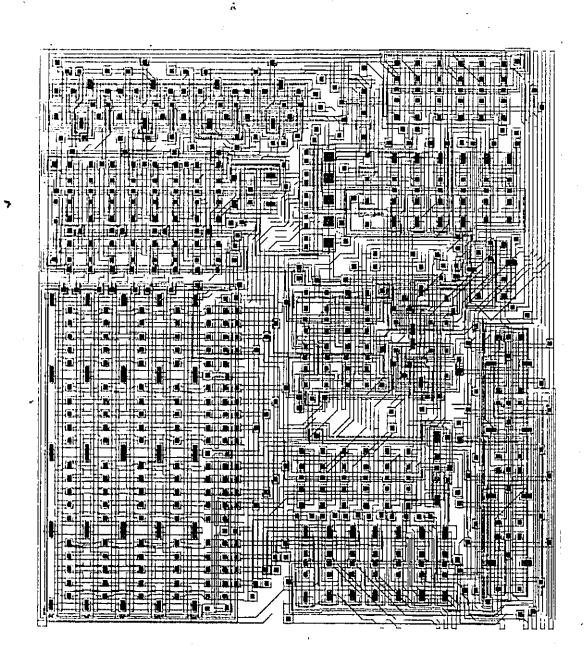

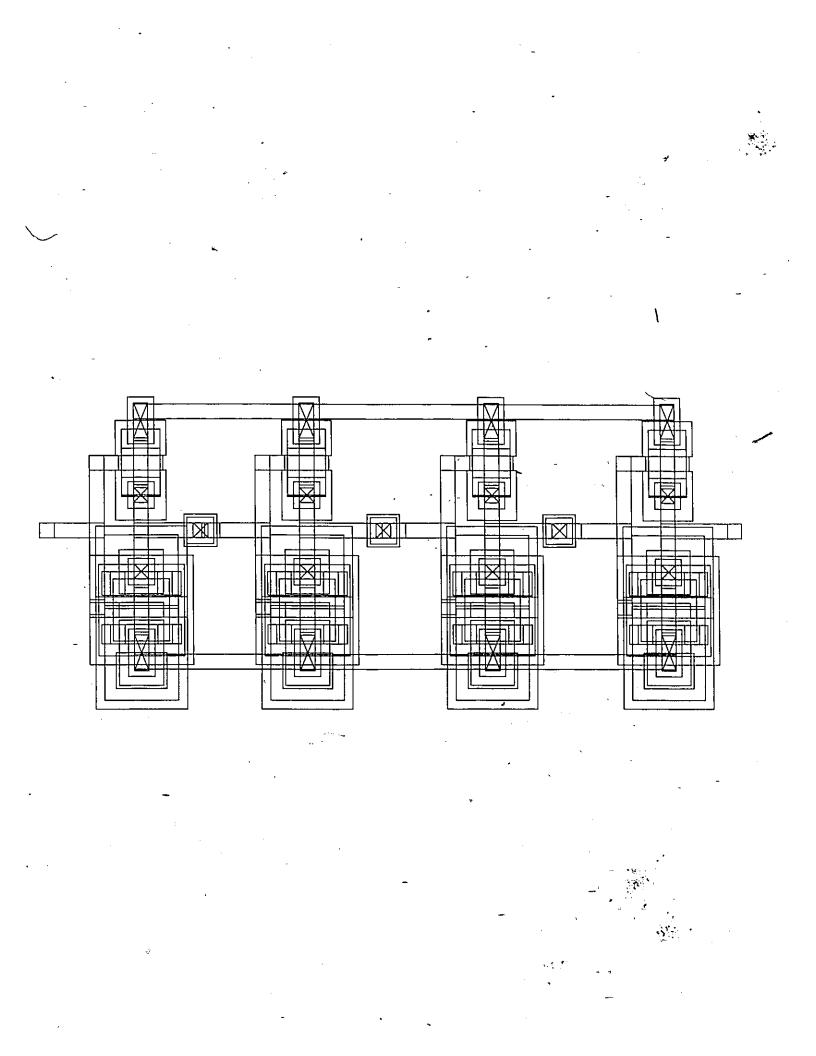

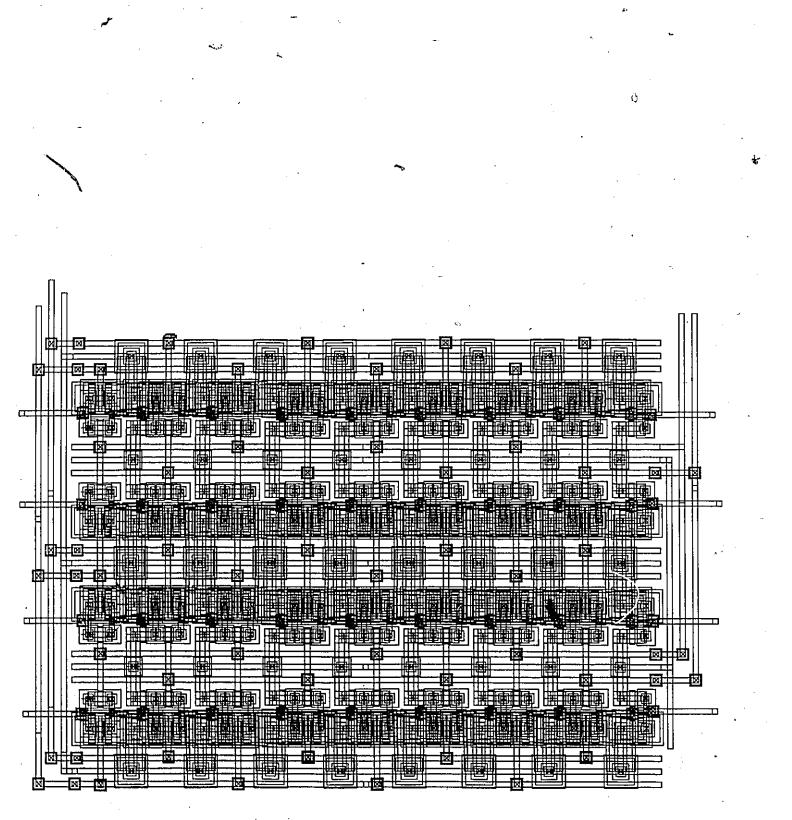

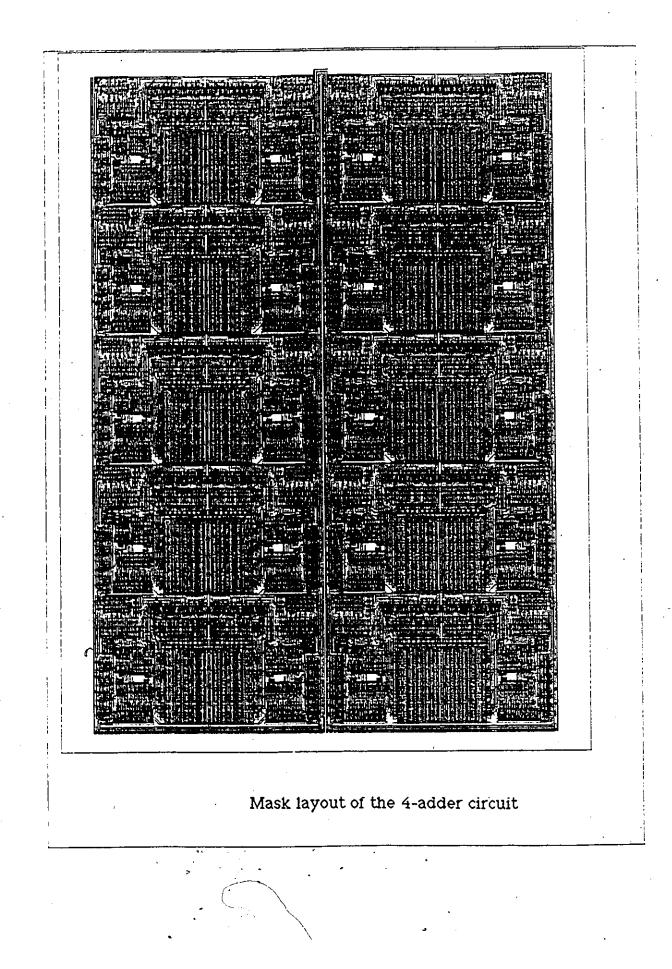

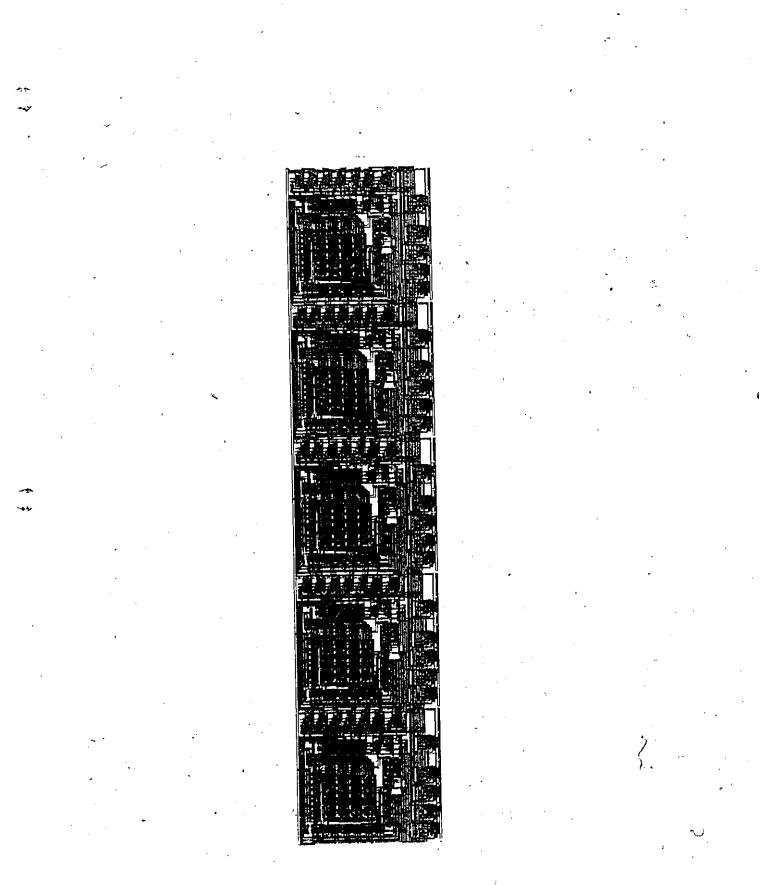

| Figure | 3.13: Mask layout of the 4-adder                            | 64              |

|        | 3.14: Input example of a modular multiplier to MOSC         | 65              |

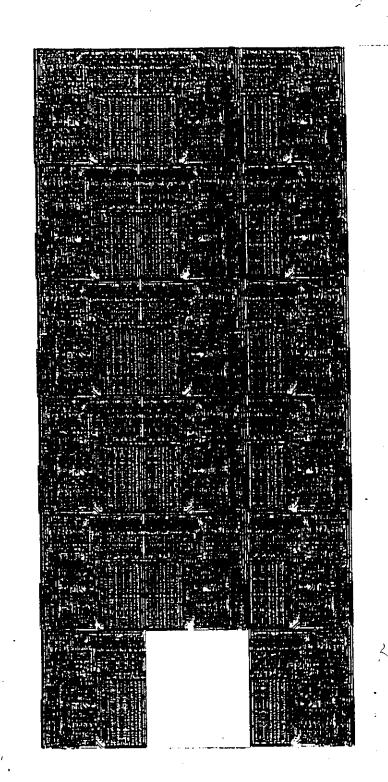

| Figure | 3.15: Mask layout of the multiplier                         | 66              |

|        | 3:16: Input example of constant operator                    | 67              |

|        | 3.17: Mask layout of the constant operator                  | 68              |

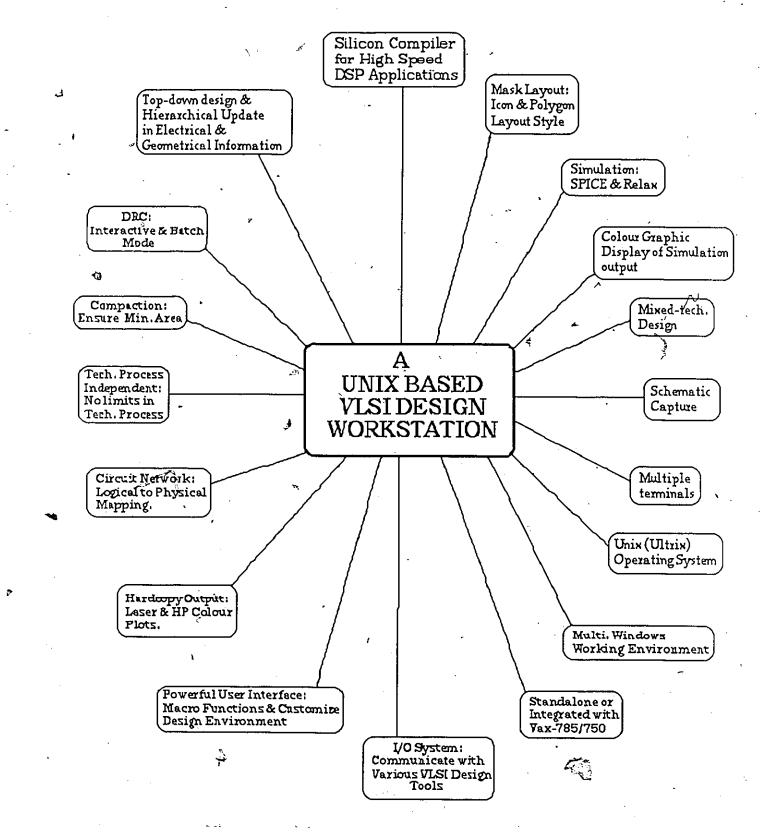

|        | 4.1: Capabilities of the Unix based VLSI design workstation | 78              |

| Figure | 4.2: VLSI design facilities with the Unix based VLSI design |                 |

|        | workstation                                                 | 79              |

# List of Tables

| Table 2.1: Truth table of a 1-bit adder        |            | 14 |

|------------------------------------------------|------------|----|

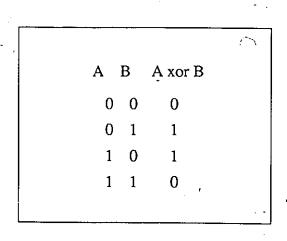

| Table 2.2: Truth table of an XOR gate          |            | 28 |

| Table 3.1: Memory content for 5-bit modulo-31  | adder      | 46 |

| Table 3.2: Memory content for 5-bit modulo-31  | subtractor | 48 |

| Table 3.3: Memory content of quarter square of | perator    | 51 |

`~

yiii

2

ÿ

¥

К,

### CHAPTER ONE

### Introduction

As the design and fabrication technology associated with Very Large Scale Integration (VLSI) circuits advances, the complexity of VLSI circuit design is constantly increasing. Each year more complex architectures involving a larger number of transistors can be implemented in a smaller silicon area. Accordingly circuit designers must then rely more and more on computer-aided design (CAD) tools. Many CAD tools have been developed to simplify the design tasks during the past decade and consequently the design time required for a successful design has been reduced from years to months or weeks. However, as the complexity of VLSI circuits increases viable CAD tools must be much more sophisticated. In some cases, the tools are difficult and inflexible to use.

For successful VLSI circuit design, the actual design morphology is only half the battle, and the other half is learning how to use the CAD tools effectively and in a straight forward manner. Therefore, a powerful, easy-to-use and flexible CAD tool for VLSI design is needed to aid in the solution of complex design tasks.

The objectives of this research are to create a fully functional Unix based VLSIO design workstation, to identify a full-custom hierarchical VLSI design methodology, and to develop a special class of silicon compiler for high speed digital signal processing (DSP) applications. The workstation is based on the DEC VAXstation II/GPX

]

minicomputer located in the VLSI Research Laboratory at the University of Windsor.

The development of the fully functional VLSI design workstation has been influenced by a number of reasons. First of all, Ultrix, the Digital version of the Unix operating system, is selected to run on the workstation because the VLSI research community in most other universities uses Unix as the most popular operating system. In order to communicate with and be compatible with other universities a Unix based facility for VLSI design must be installed in our research laboratory.—In addition, we wish to be able to use the large number of public domain VLSI design software programs developed in a Unix environment that are available.

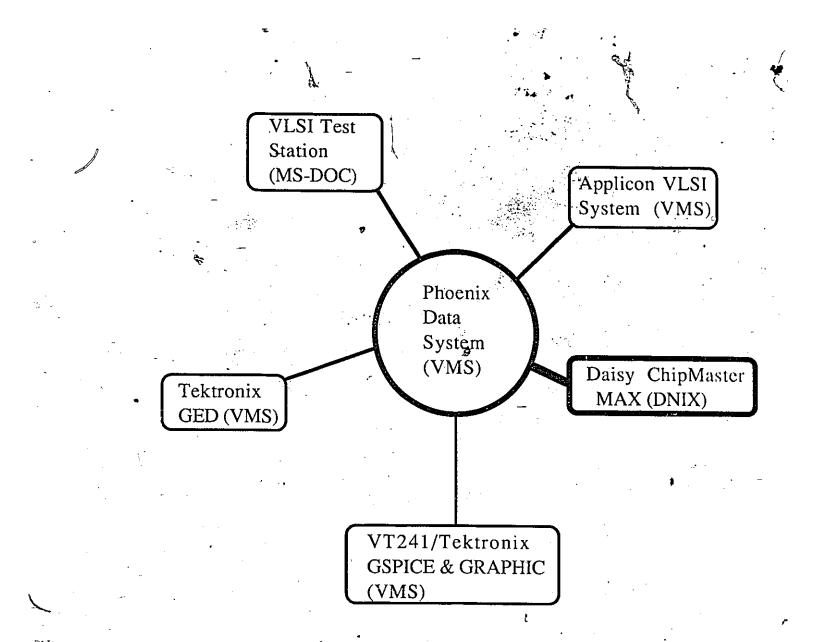

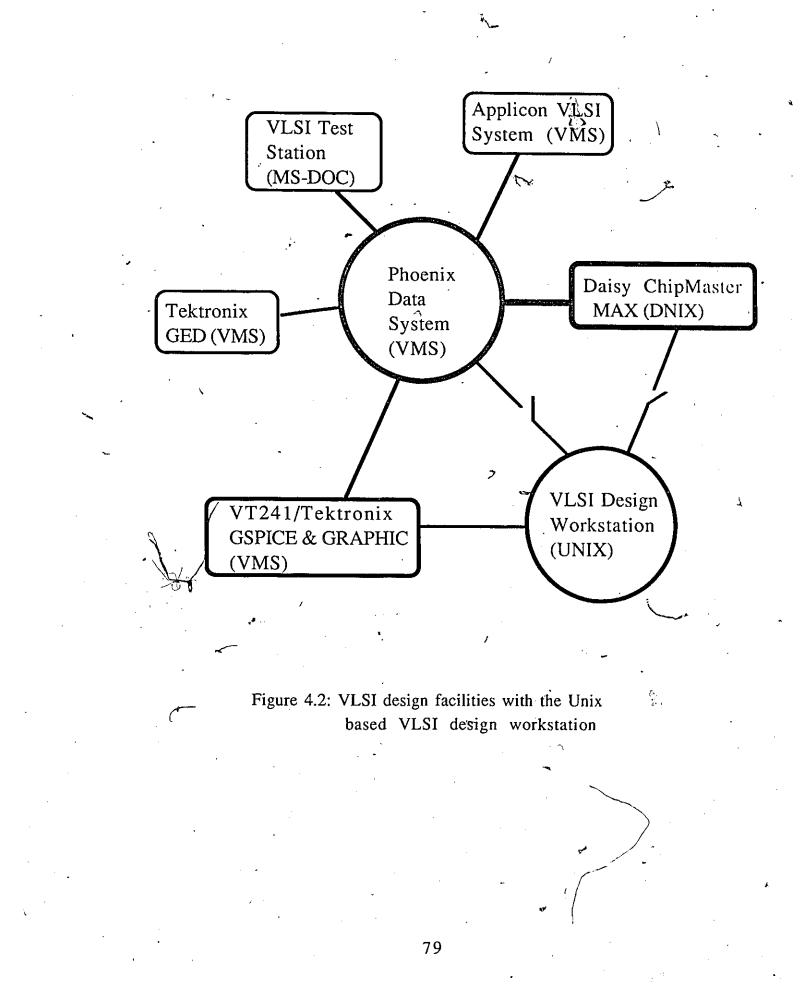

As shown in Figure 1.1 the present VLSI design facilities at the University of Windsor are centered around Phoenix Data System software running on a VAX-11/750, a standalone Daisy ChipMaster workstation and the Applicon VLSI design system operating on a VAX-11/785. Presently most of circuit mask layouts are done using the Daisy's MAX layout editor, and then the design verification is performed using the Phoenix Daia System software. Hence, a lot of time is typically spent on converting data formats and transferring files between the two machines. A completely integrated workstation with a layout system and a circuit verification capability is needed to improve the VLSI designer's productivity and use the computing resources more effectively.

2

Figure 1.1: VLSI design facilities in the VLSI Research Laboratory

It was also desired that the VLSI workstation have a special silicon compiler that allows one to synthesis Residue Number System (RNS) arithmetic operators directly from design specification. A large portion of the research efforts carried out by members in the Signal and System Group has been concentrated on high-speed DSP applications based on RNS structures. As part of this research a number of basic memory cells based on the RNS concepts have been designed and fabricated successfully. In order to expand this

research orientation it is very useful to carry out the design of RNS arithmetic operators with the aid of a silicon compiler and to integrate the silicon compiler with the VLSI design workstation software.

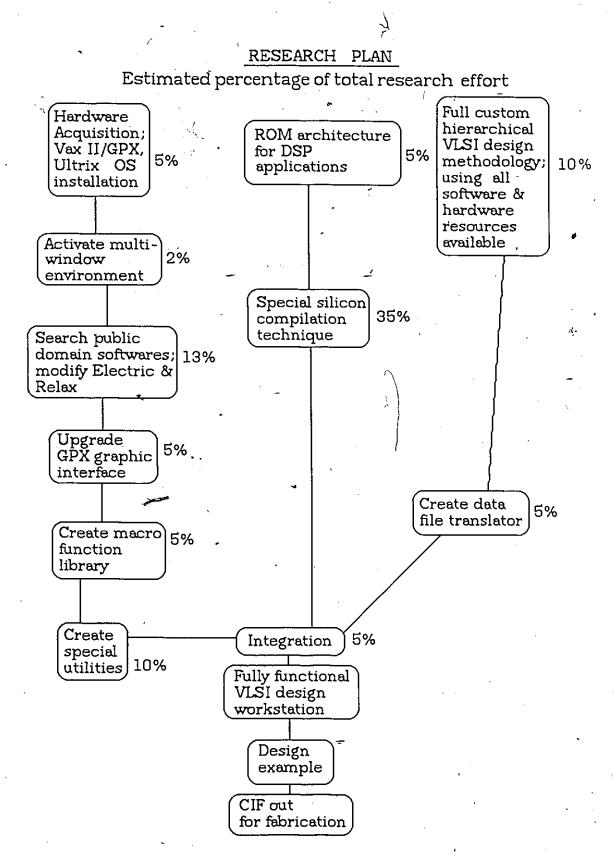

The research plan was divided into three paths, as shown in Figure 1.2. The percentage shown beside each box represents the relative amount of effort expended in that area. The first path is mainly concerned with the Ultrix operating system, the windowing facility, and public domain software programs. The second path concentrates on the creation of a silicon compiler for the RNS operators. The third path leads to the identification of a VLSI design methodology and to determination of which CAD tools are required at each design stage. We must know the problems or difficulties involving the interrelations between design procedures, and the availability of and need for CAD tools must be determined before we can provide a viable VLSI design workstation. In addition to the methodology and tools problem, a data format translator must be developed in order to allow the workstation to communicate with other VLSI design tools.

Now let us look at the hardware elements of VLSI design workstation first followed by software details. The design workstation is physically based on the DEC VAXstation II/GPX workstation which supports a wide range of applications. The GPX workstation gains its performance advantage from a powerful graphics coprocessor that offloads text and graphics computation from the CPU. It also offers a double-buffered video memory closely

-4

Figure 1.2: Research activities involved in the project.

coupled to the coprocessor, which translates into faster text and graphics drawing speeds. The coprocessor can independently access display list instructions to manipulate graphical objects, further freeing the CPU to run the application software. The resolution (or pixels) of the 19-inch colour monitor is 1024 \* 864. 256 colours selected out of a possible 16 million colours can be displayed simultaneously. The GPX workstation is currently equipped with 9 Mbytes of main memory, 216 Mbytes of disk storage and a 95-Mbyte tape drive.

A Unix based computing environment has been implemented on the GPX workstation. Ultrix, Digital's Unix operating system, is compatible with AT&T's system V while maintaining all Berkeley 4.2 BSD commands, system calls and library functions. Ultrix version2.0 has been successfully installed in the GPX workstation. Ultrix also features the X-Window system which is emerging as a windowing standard for the Unix workstation community. The X-Window system has also been loaded in the workstation. A startup command file has been written to initialize the windowing environment, and to define various combinations of keys on the keyboard and mouse buttons to invoke a number of window commands. The X-Window system allows one to resize, restack, move, and iconify windows. It also provides pop-up menus for creating new windows, changing window colours, or starting applications. It can be easily customized, giving users complete control over their own window environment. A more detail description on how to use the operating system and the X-Window facility is included in Appendix I. Besides the windowing environment, a communication system is also provided. The

workstation is linked to other main frame computers by an Ethernet realization of a local area networks. A mail facility and remote file manipulation across heterogeneous operating systems are setup properly for mail and file transfer. A manual has been written for users to use the facility effectively and is also included in Appendix I.

One of the research goals was to investigate the performance of public domain software and determine which software could be useful to the project. After a number of available software packages were evaluated and Electric, a complete electrical design system developed at the Fairchild Laboratory was chosen as having the potential to run on the GPX workstation effectively. Since Electric was primarily developed to run on a Sun workstation and an AED frame, buffer terminal operating under the Berkeley BSD 4.2 system, a lot of modifications had to be made. A discussion on how to modify and compile programs is presented in Appendix II. After a long process of development Electric design system has been successfully integrated as part of the application software running on the GPX workstation.

In summary, the software developed for the GPX workstation falls into three areas. The first and major software project is the realization of a silicon compiler for RNS oriented applications. The second major project is the modification of the public domain Electric package and its integration into the workstation environment. The third major project area was concerned with the development of a number of special utility programs, such as file conversion programs, plot routines, and graphic drivers for a number of output devices. All

these programs were implemented on the GPX workstation and then fine-tuned to provide a powerful productivity tool for VLSI design.

$\sigma$

8

h

### CHAPTER TWO

.

### Full-Custom Hierarchical VLSI Design Methodology

A typical VLSI design methodology described in the literature [WeEs85] consists of a behavioral description, a structural description and a physical description. Each of these descriptions is further subdivided into a number of design options that may be selected for a particular design. These three levels of description are adequate for a general integrated circuit design environment. However, in order to take full advantages of a given process technology and to simplify the steps associated with complex circuit design, a fullcustom hierarchical VLSI design methodology has to be adopted.

An effective design methodology alone is not enough for designing complex VLSI circuitry. A number of VLSI computer-aided design (CAD) tools is also required to reduce the complexity of the design process. A VLSI circuit is a complex maze of polygons and lines that form paths that in turn combine to effect an overall function. For successful circuit design CAD tools are needed to analyze these paths and to ensure that they are correct. In reality, a circuit design method is influenced by the CAD tools available to an IC designer. A full-custom VLSI design methodology will be presented in detail in this chapter. The functions of various CAD tools in different design phases are also explained. In addition, a silicon compiler, which ultimately generates the physical mask layout

description directly from behavioral description of a design, will also be described to show where it fits into the design methodology.

### A. Morphology of VLSI Design

j.

A VLSI design process can be largely simplified by employing the use of a hierarchical structure. The use of hierarchy involves dividing a circuit (module) into simpler subcircuits (submodules) and then repeating this operation on the submodules until the complexity of the submodules is at a comprehensible level of detail. This concept is similar to the one used in developing a complex software program where large programs are split into smaller and smaller sections until simple subroutine, with well-defined functions and interfaces, such as passing parameters, can be written. In other words, the major reason of using hierarchical description is to keep the amount of detailed information the designer must work at each stage in the VLSI design process at a minimum.

Once the submodules have been identified, modularity for the submodules can then be considered. If the modularity of submodules is well formed, the interaction with other submodules can be easily achieved. For instance, the physical interface of each submodule that indicates name, position, layer type, size and signal type of external interconnections must be well defined so that no extra connections are needed to connect the submodules when the cells are placed together.

The use of hierarchy and modularity simplifies the problem complexity and enhances the design strategy. The hierarchy and modularity are parts of the hierarchical VLSI design methodology which is identified in Figure 2.1.

The VLSI design is a continuous trade-off process to achieve

proper results through a number of iteration processes as shown in the Figure 2.1. Different VLSI design tools are used in each design phase to reduce the complexity of the design and assure the designer of a working product so that a diversity of VLSI design tools can be vital to the success of a VLSI circuit design project.

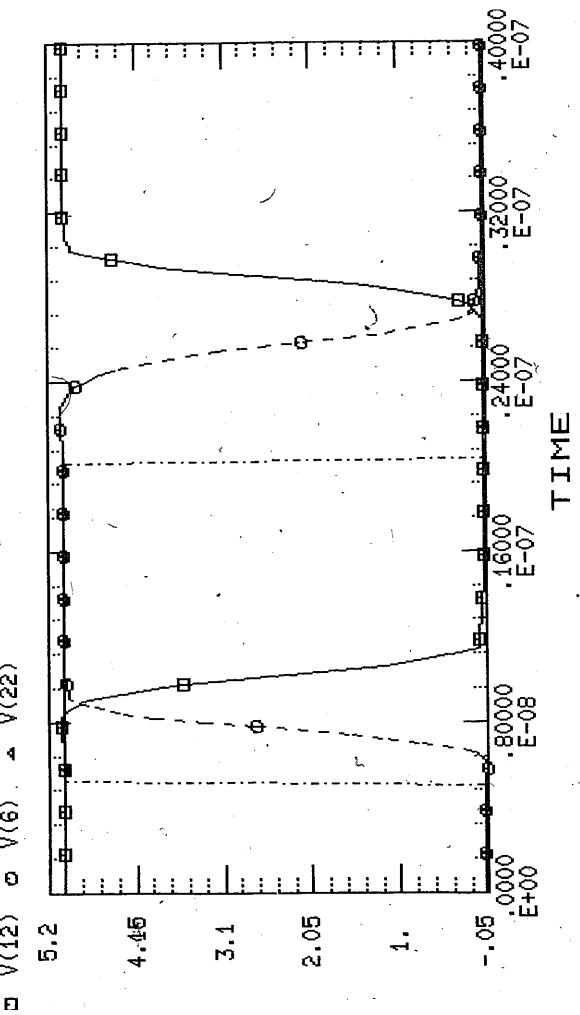

In order to explain the design methodology effectively, a simple 4-bit ripple carry adder circuit is used to illustrate the design procedures and the function of the various available on the VLSI design workstation.

In the first step of the design process, the problem specifications must be clearly stated and divided into smaller problems. This step is usually done by a designer. The hierarchy of VLSI design is employed in this step. For example, when designing a 4-bit combinational adder we have two 4-bit inputs, labeled A and B respectively, one 4-bit output labeled SUM, and 1-bit output labeled CARRY. The adder can represented as a black box with two inputs and two outputs, as shown in Figure 2.2. Now we have to simplify the black box so that the problem specifications can resolved into smaller problems. Since we are designing a 4-bit adder, we can divide the black box into four smaller black boxes as shown in Figure 2.3. Each of these subdivisions has three 1-bit inputs and two 1-bit outputs. The simplified design problem is now how to design a 1-bit adder.

Once the problem has been clearly identified, an initial logical or functional level simulator is built to simulate whether the initial design concept will meet design specifications. In logical level simulation, circuit elements are modeled as simple switches or gates connected by wires. The logical level simulator usually simulates the

Figure 2.3: The 4-bit adder at sub-block level

circuit at the device level or at the gate level. In most complex cases, the logical simulator is dependent upon the problem so that it is usually created by the designer. If the results of logical simulation are not satisfactory the designer may have to make some trade-off decisions with the problem specifications in order to achieve adequate results. For the simple example of the 4-bit adder, a logical level simulation is not necessary. A truth table or functional description of the adder can be easily obtained and is shown in Table 2.1.

| 0 |   | n  | OT THE | C ADDT |   |

|---|---|----|--------|--------|---|

| С | Α | В  | SUM    | CARRY  | ; |

| 0 | 0 | 0  | 0      | 0      |   |

| 0 | 0 | 1  | 1      | 0      |   |

| 0 | 1 | 0  | 1      | 0      |   |

| 0 | 1 | 1  | 0      | 1 .    |   |

| 1 | 0 | 0  | 1      | 0      |   |

| 1 | 0 | ۰1 | 0      | 1      |   |

| 1 | 1 | 0  | 0      | 1      | 1 |

| 1 | 1 | 1  | 1      | 1      | • |

|   |   |    |        |        |   |

### Table 2.1: Truth Table of a 1-bit Adder

In most cases, Boolean equations can be derived from the results of the logical level simulation. In the case of the adder example, the Boolean equations derived from the Table 2.1 are shown as follows:

SUM = ABC + A(BC)' + C(AB)' + B(AC)'CARRY = AB + C(A+B)

The next task to be performed by the designer is a custom CMOS realization of the logical equations. The CMOS realization is initially captured in a schematic form which is usually created using a schematic editor. The schematic form is used to store the major logical components or MOS transistors and their connectivity. The

process of creating a schematic is sometimes called schematic capture.

The designer may use the schematic information to ensure that the mask layout to be created correctly corresponds to the desired circuit in the later design phases. The designer may schematically capture the logical equations at the device or gate level and the MOS realization at the transistor level. In the case of the 4-bit adder, the gate level and transistor level schematic captures shown in Figure 2.4 are created by the schematic editor available on the VLSI design workstation. The schematic editor in the workstation is invoked by using the technology use logic command. This editor can draw all major logical devices, including gates, flip-flops, user-defined black box, all types of MOS transistor and various meters. The connectivity of the logical components is stored in a circuit netlist.

Once the netlist has been captured, switch level [Brya81] and initial circuit simulations can be performed to ensure the correct correspondence between the custom MOS realization and simulation results. These simulators mainly use a transistor as the primitive or switch element. In the VLSI design workstation, five switch level simulation interfaces for ESIM, RSIM, RNL, CADAT and MOSSIM simulators are supported. These simulators use only the (0, 1, X) states. For each set of input vectors, the circuit is simulated to determine a steady-state level at the output nodes.

On the other hand, the initial circuit level simulation [Nage75] determines the analog waveforms at particular nodes without considering any capacitance or resistance. The circuit elements are modelled as transistors with a number of parameters. The values of

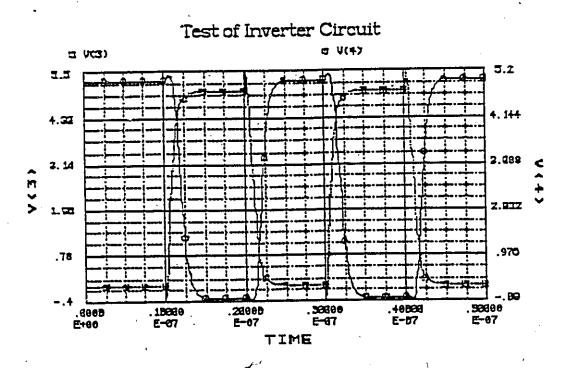

Figure 2.4: (a)Gate-level Schematic Capture of 1-bit Adder (b)Transistor-level Schematic Capture of 1-bit Adder the parameters are determined by the technology process and the geometrical properties of the transistors. The initial circuit level simulation combines the information from the netlist and the userdefined device model to provide more detail about the waveforms at the nodes. One of the most widely used circuit level simulators in VLSI design is SPICE and this package is also supported on the VLSI design workstation. The SPICE deck information for the circuit can be extracted from the circuit schematic which was created in the previous design phase. If the simulation results turn out to -be unsatisfactory, the designer may have to go back and modify the MOS realization. This process is repeated until satisfied results are obtained.

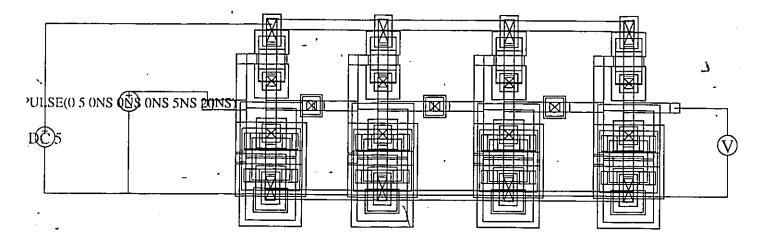

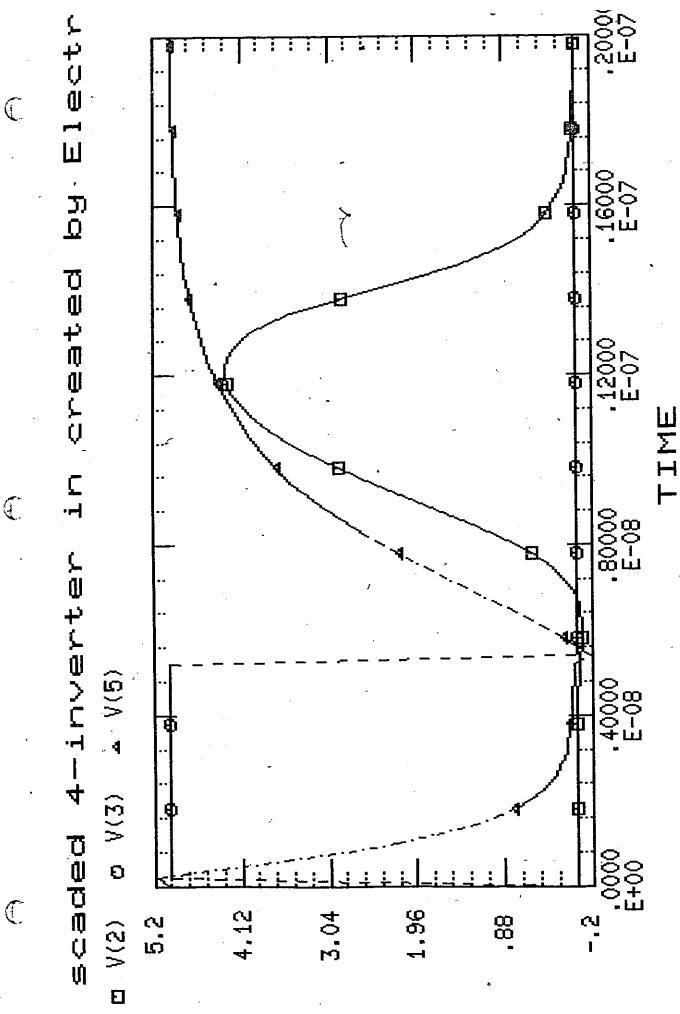

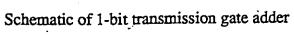

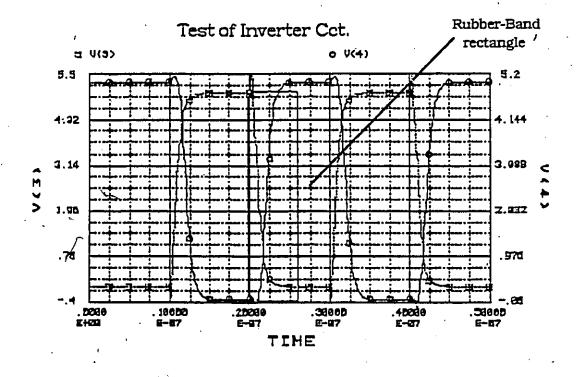

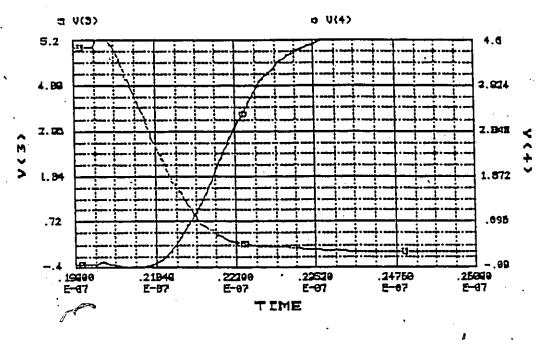

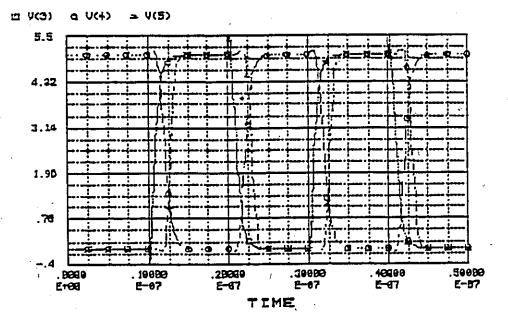

For the example of the adder, a SPICE input file is created by the SPICE Deck Extractor, and a circuit simulation has been performed and the simulation results are shown in Appendix III. The updated CMOS transistor model information is also automatically included in the input file. If a power source, ground node, input signals and output signals are completely specified in the schematic capture, a complete SPICE input file can be created directly without any human interaction. Two programs, GSPICE and GRAPHIC, have been written to enhance the SPICE graphic capabilities. These two programs can significantly speed up the whole simulation process. A detailed description on how to use the programs together with a program listing of GRAPHIC are included in Appendix IV.

Once the initial simulation results are within a satisfactory range the mask layout generation of each module cell can be undertaken. The modularity of the modules shall be considered here

in order to simplify the hierarchical system layout in a later design phase. For example, the power (VDD) line may be located at the top of the module cell and the ground (VSS) line at the bottom of the module. The inputs may come from the left side of the module and the outputs from the right side of the module. If the layout of the circuit mask is done in this fashion there is no need to create extra connection wires between modules when the module is replicated to form a chain.

Ŷ

٠٤,

There are two types of layout approaches in manually creating a mask layout, namely icon type and polygon type. For the icon type layout, the designer is concerned with the mask layout mostly at the transistor and transistor interconnection level since a MOS transistor is a primitive-element and has its own symbolic representation or icon. In contrast, for a polygon type layout system the designer has to create every single polygon. Hence, the use of icon oriented layout is a much faster approach in creating a mask layout. The connectivity of a mask layout created by an icon layout method is also easier to be established and maintained. However, one of the major advantages of using a polygon based layout method is that a VLSI circuit can be realized in a minimum area of silicon.

Both mask layout types are supported on the workstation. The native mask layout method on the workstation is the icon oriented one because connectivity information can be extracted quickly and this is important to the other CAD tools of the workstation. The polygon type layout capability is also enhanced with the aid of powerful macro functions that are described in Appendix V. For the

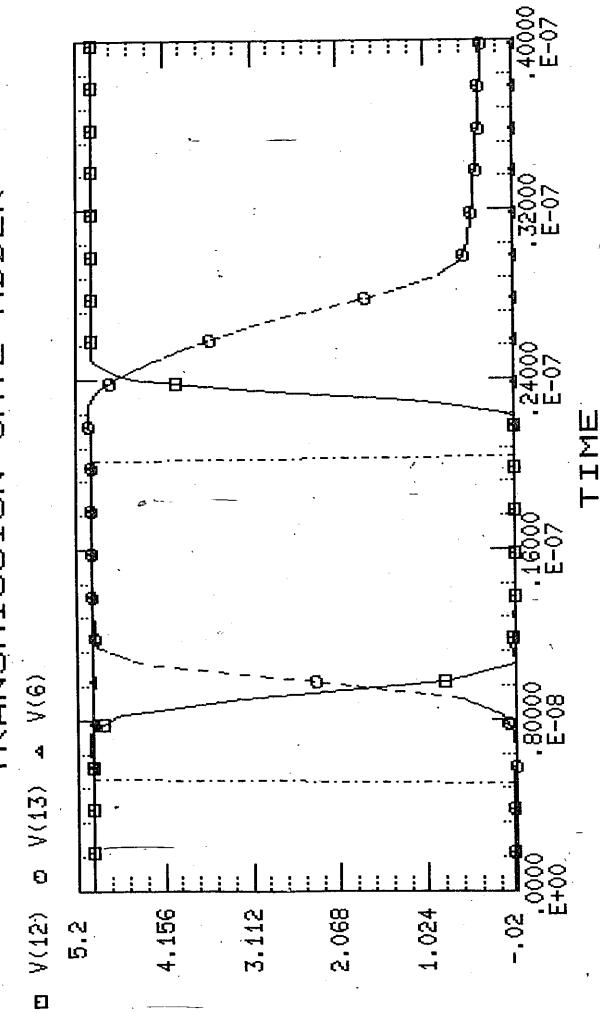

adder example a mask layout for a 1-bit adder is shown in Figure 2.5. The mask represents 28 transistors and their interconnections.

$\mathcal{F}$

Once the initial mask layout has been created, the designer may optimize the size of the mask by using a compactor. The function of a compactor is to remove unnecessary space from a design by moving every layer of the mask to its closest permissible distance. A two-dimensional compactor is available on the workstation used to compact a mask layout in both the horizontal and vertical directions.

The compacted mask layout of a design must then be checked thoroughly to guarantee that there are no design-rule violations. This process is usually called the Design Rule Check (DRC) and is generally concerned with the physical placement of the layout. The DRC works in accordance with a number of layout restrictions which are in turn dependent on the fabrication process. The layout restrictions ensure that the manufactured circuit will connect as desired with no shortcircuits or open paths. On the workstation, the DRC can be operated in an incremental and batch mode. If the DRC is operated incrementally, it checks each change as it is made to the circuit mask. If any designrule violations are found, the DRC will point out exactly where and what the violations are. All the design-rule errors must be corrected completely before going on to the next design step.

After all design rule violations have been corrected, a net list comparison can be performed to check the correctness of the interconnection of the mask layout. In contrast to the DRC that is usually concerned with the geometrical design rules the net list comparison examines the electrical connection rules set out by the

20

C

Ņ

designer. For the <u>purpose</u> of comparison, a circuit network must be derived from the compacted mask layout by a node extractor. In most cases, it is beneficial to know whether the circuit network is the desired network. Although simulation and other analysis can tell much about circuit correctness, only the designer knows the true topology, and hence would benefit from knowing whether the derived network is the same.

The mask layout is usually done in a way to correspond to the schematic description of the desired circuit. Since the mask layout is usually done manually an error in the interconnection of the mask circuit is unavoidable. It is much easier to understand and check the schematic network. Generally, the schematic network has known and correct topology while the network derived from the IC layout is less certain. The goal is, therefore, to compare these networks by associating the individual components and connections, If all of the parts associate the networks are the same, however, if there are unassociated parts this indicates how\_ the networks differ. The Electric network software monitors all database activities and updates the connectivity information automatically. This software also provides connectivity information to the design-rule checker and various circuit simulators. In addition to maintaining correct network information, this network tool is also able to compare the schematic network and the mask level network.

Although the designer can determine that the mask level network is the desired circuit with the aid of DRC and netlist comparisons the performance of the mask circuit, such as, speed and power dissipation is not known yet. Therefore, a full analog

simulation must be performed. The transistor connectivity with all parasitic capacitances and resistances are extracted from the mask layout by a circuit extractor that is similar to the one used in capturing a netlist from a schematic description. In the workstation, the SPICE Deck Extractor can extract all the transistors and their connectivity with associated parasitic components and convert the extracted information into a SPICE input format file which can be read into the GSPICE program.

A complete analog simulation of the module cell at the mask level is then performed to provide fine-grain detail about the waveforms at nodes. The SPICE program is the best simulator available to perform the detail simulation. Generally, an analog simulator such as SPICE is used to check the performance and the critical path of a design. In the workstation, another circuit simulator, Relax2 [LeRu82], is also provided. It does not generate the simulation results as accurate as SPICE does, but it takes much less time to compute. The -Relax2 package in the workstation serves as an alternative simulator for to the designer. The Relax2 simulator is based on the Waveform Relaxation method [LeRu82] and is an iterative method for analyzing nonlinear circuit systems in the time domain. The method, at each iteration, decomposes the system into several subsystems. Each of the subsystems is then analyzed for the entire given time interval. One of the limitations of Relax2 is that it cannot efficiently simulate a circuit with feedback. The simulation results generated by SPICE and Relax2 can be graphically displayed in the workstation by using a plotting program called PLOT. The PLOT program offers a number of options for users to select, such as,

multiple windows, window size and plotting range. A discussion on the operation of the program and the program listing are included in Appendix VI. Other programs for hardcopy devices are also discussed in this appendix.

If the simulated performance does not meet the design requirements, the designer may have to optimize the mask layout further. For example, the designer may modify the size of the transistors along the critical path to increase the throughput rate.

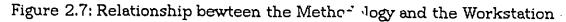

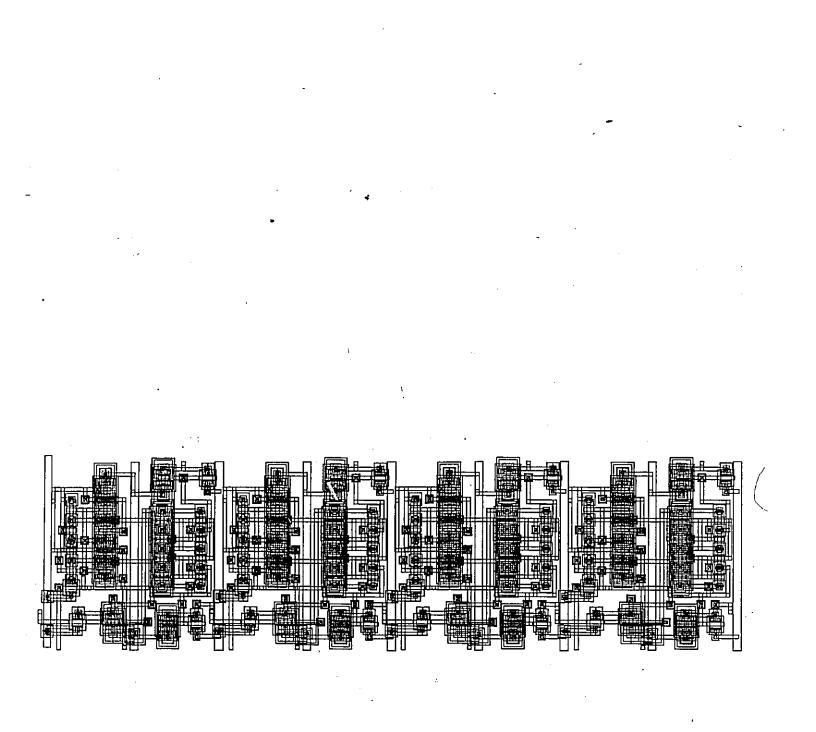

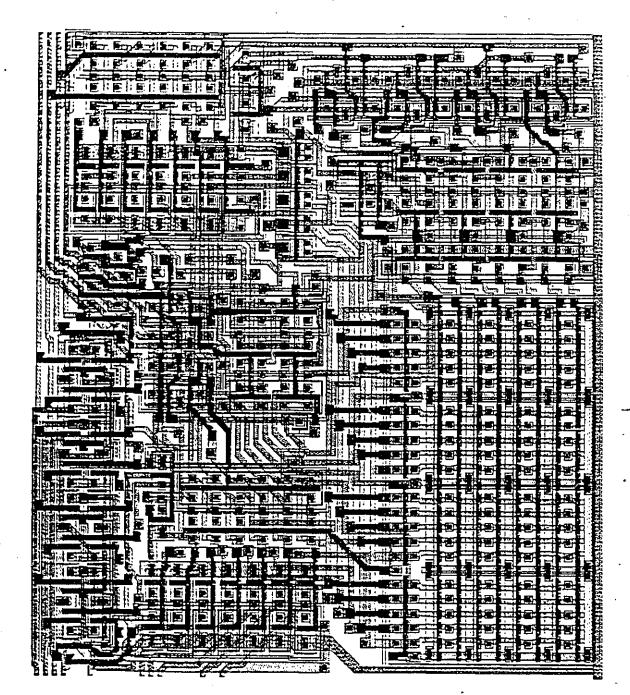

The design procedures, as mentioned above, are repeated for each submodule circuit. After all submodule cells have been correctly created and optimized the designer can use the mask editor to place the submodule cells together to form the complete circuit. In the workstation, the cell placement can be effectively handled because the connectivity between module cells is always maintained. The mask layout of the complete the 4-bit adder is shown in Figure 2.6. The modularity of the module cell can be examined. The CARRY input is coming from the left side and the CARRY output is leaving from the right side. Therefore, when the module cell is replicated to form an array of four, the CARRY output of one cell is overlaed with the CARRY input of next module cell so that no extra connections are needed.

A hierarchical verification for the complete mask circuit may be performed to ensure that no geometrical design rules or electrical design rules are violated. The next design step deals with input and output (I/O) considerations. For example, how many power pads and ground pads are needed. These I/O pads are usually stored in a standard cell library and the designer can take them from the library

Figure 2.6:Complete mask layout of ripple carry adder

after, the complete system layout has been completed. When all the mask modules and I/O pads are placed at their proper locations a final mask layout verification, usually a DRC check, can be performed.

The last design step is to convert the complete mask 's internal representation into a data format that is supported by the silicon foundry. For example, the Canadian Microelectronics Corporation (CMC) supports Caltech Intermediate Format (CIF) as a mask representation. In the workstation, a data file translator program is used to translate between the internal data format file and CIF file. The translator programs called ECIFIN/DCIFIN are explained in more detail in Appendix VII and the source codes are also included. Since CMC has some restrictions on the CIF file,' the internal data file has to be carefully converted into a proper CIF file. The translated CIF file can also be read directly and understood by other VLSI tools available in the VLSI Research Laboratory.

To summarize the hierarchical design methodology and the CAD tools available in the design workstation to assist the designer in various design phases, a diagram representing the relationship between the design steps and the VLSI design workstation is shown in Figure 2.7. As illustrated in this diagram, various CAD tools are provided to simplify the design tasks. For instance, a solid line linking the DRC design step and the workstation means that a design-rule checker (DRC) is available to check the geometric for design rule violation. As a whole, all the VLSI CAD tools implemented on the workstation form a fully interactive and functional VLSI design workstation tailored for the full-custom hierarchical design methodology.

25

P.C.

26

ſ

In order to illustrate the capability of the workstation in more detail two combinational circuit designs have been carried out. The circuit designs include a four-by-four shift register and a transmission gate adder. The mask layout of the shift register was completed in less than two days. Four days were spent for the transmission gate adder. These designs also follow the full-custom hierarchical design method. All circuits have been divided into smaller circuits.

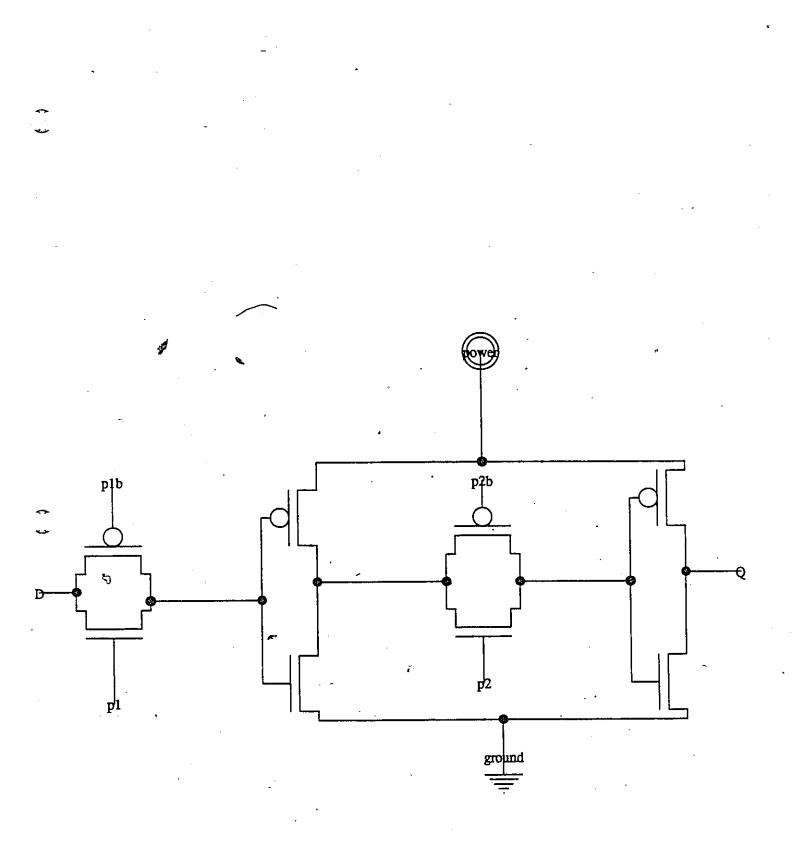

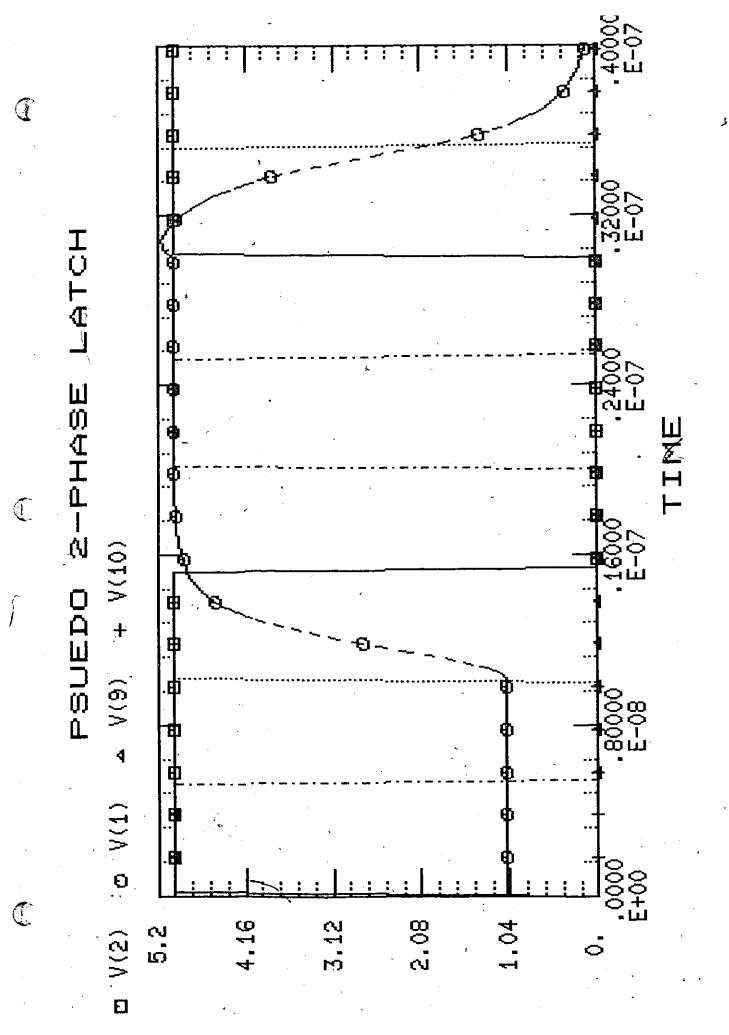

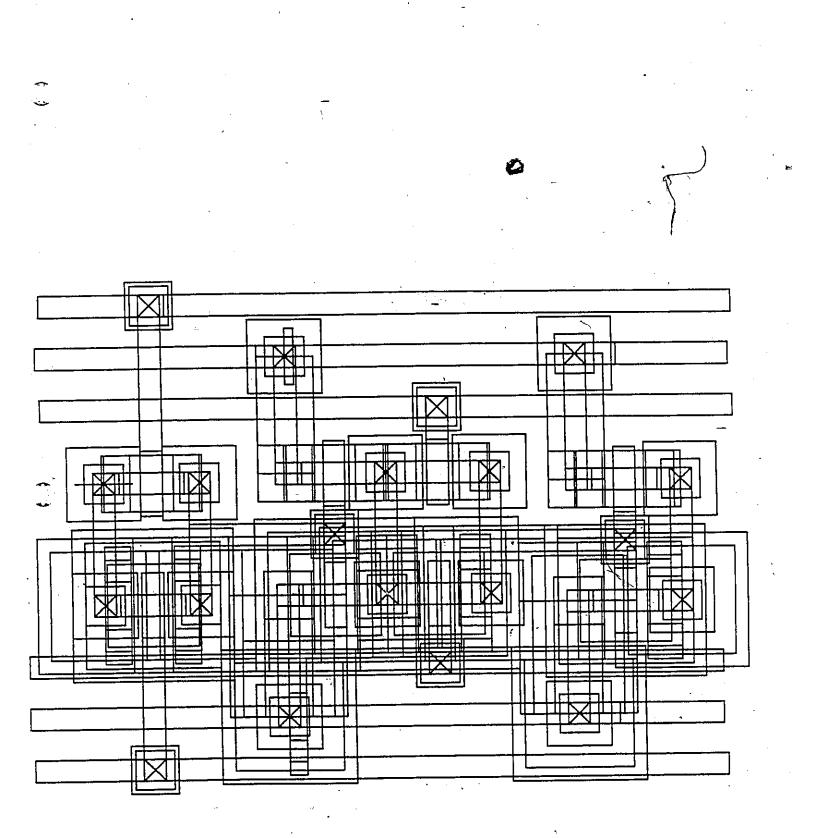

The shift register is based upon a simple latch or D flip-flop circuit. This latch requires two non-overlaing clock signals and their complements. The operation of the latch is relatively simple. Hence, it will not be discussed here but rather interested readers are referred to [WeEs85]. The four-by-four shift register is formed by replicating the latch two-dimensionally. The schematic diagram, simulation results, and mask layouts are shown in Appendix III. The sizes of the D flip-flop and the shift register are 99.6x70.8 micron<sup>2</sup> and 394.8x286.8 micron<sup>2</sup>, respectively. A 8-by-8 or 16-by-16 shift register can also be created in this way.

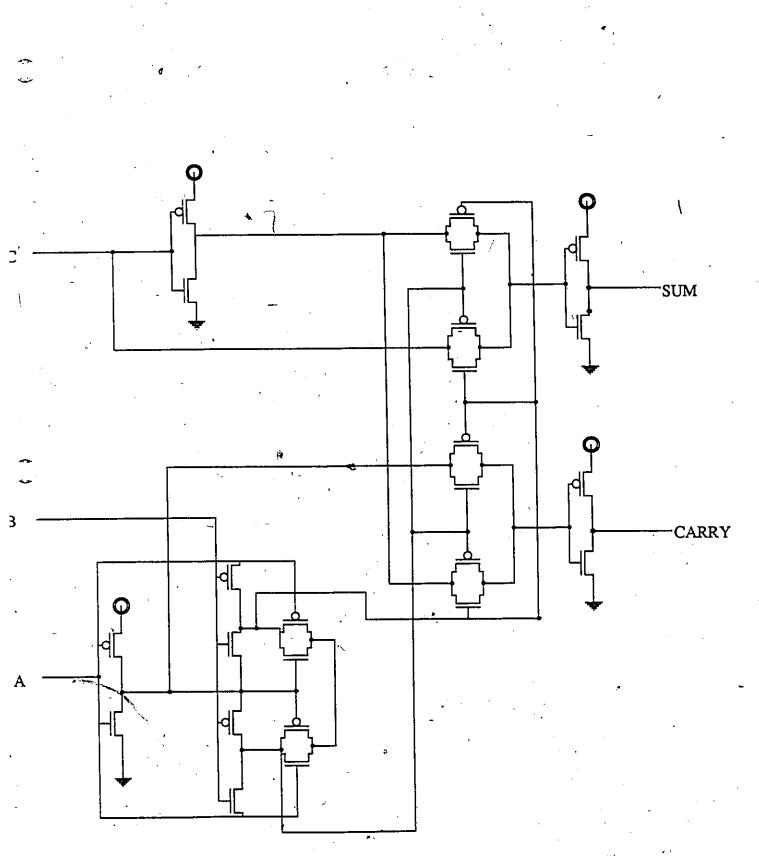

As described previously in this chapter, a 4-bit ripple carry adder was designed. Another adder based on a different approach is given as another design example. This new adder uses the exclusiveor (XOR) gate. The truth table of a XOR gate is tabulated in Table 2.2. The schematic for the XOR circuit is shown in Figure 2.8.

ß

Figure 2.8: Schematic diagram for transmisson gate XOR circuit

Table 2.2: Truth table of an XOR gate

)

The operation of this circuit is explained as follows:

1 When signal A is logically low, A' is high. The transmission gate is thus closed and transistor pair 1 and 2 is disabled. The output is therefore B.

2 When signal A is logically high, A' is low. Transistor pair 1 and 2 thus act as an inverter and the transmission gate is now open. The output is therefore B'.

With this configuration, a six-transistor XOR gate is formed. By using four transmission gates, four inverters, and two XOR gates, a 1bit transmission gate adder can be constructed as described in [WeEs85]. The resulting adder has 24 transistors, the hame as the ripple carry adder. The new adder offers the advantage of having equal SUM and CARRY delay times. In contrast to the ripple-carry adder where the SUM and CARRY' signals are not inverted. The complete schematic, simulation results, and mask layout of a 1-bit transmission gate adder are shown in Appendix III. The simulation results indicate that the performance of the transmission gate adder is better than the ripple carry adder. A 4-bit adder is again created by replicating the 1-bit adder to form a linear array of four. The mask layout of the 4-bit adder is also shown in Appendix III. The size of the 1-bit adder and the 4-bit adder are 159x153.6 micron<sup>2</sup> 581.85x153.6 micron<sup>2</sup>, respectively. This transmission gate and adder can also be used in constructing a parallel multiplier.

B. The Role of the Silicon Compiler

As illustrated in the previous section, the mask layout of all the circuit designs is created manually. Although the mask layout editor available in the workstation is easy to use, it still takes several days

or weeks to complete a mask layout. One of the most powerful CAD tools used to produce a desired mask layout representation directly from the behavioral description of a circuit is a silicon compiler. The meaning of the term "silicon compiler" has changed over the years as advances in CAD tools have been made. Initially it implied the concept of specifying some extra switches to a normal programming language compiler so ,for example, it would translate a FORTRAN program into the lowest level mask layout description, rather than into object code. Soon, however, this concept was limited to the use of regular methods for converting logic descriptions into a physical mask layout, such as, those discussed in the last section.

X.

Today's silicon compiler is generally defined as a highly intelligent CAD tool that translates a behavioral description of a circuit design directly into the lowest level description or physical mask layout. Modern silicon compilers still use many of the same steps as do traditional language compilers. Generally, a front-end parser reads the input description and converts it to a structural representation, such as, the IC floor-plan. The back-end then produces the mask layout in two phases. First, a set of pre-defined basic module cells is selected from a cell library. Second, an autorouter is invoked to make the necessary connections between the selected module cells in order to form the desired circuit.

Most contemporary silicon compilers, however, are specialized to produce one type of design. For example, the FIRST silicon compiler, [DeMu84], developed at the University of Ebinburgh, used only bit-serial architectures and was designed for signal processing alications. In highly specialized silicon compilers as in the case of the

one described in the next chapter, the input language can be a very high level one, allowing nonprogrammers to specify chips for their own particular needs. Therefore, a silicon compiler has the potential to replace all the design steps associated with the full-custom MOS realization of logical equations to industrial fabrication specifications.

7

Ľ

## CHAPTER THREE

As was stated in the Introduction, besides creating a fully functional VLSI design workstation, it was desirable to extend the capabilities of the workstation by developing a silicon compiler for a special class of high speed digital signal processing (DSP) applications.

There are several approaches to the design of a VLSI circuit. One may employ a full-custom design effort, such as the one described in the previous chapter, where no existing standard cell libraries are used. In this case the design effort is considerable, but there is an opportunity to create an optimum architecture. Another approach is to simplify a VLSI design by using standard cells and gate-arrays reduce the problem to one of cell selection and interconnection needs. Alternately, a silicon compiler can be used when the designer does not wish to consider the many process dependent steps associated with NLSI design but instead wishes to concentrate on a higher level description of the circuit. As mentioned in Chapter Two, most silicon compilers are designed for those types of applications that use a fixed floor plan and a set of hand-optimized standard cells, such as, adders, memory cells and multipliers. The major reason for developing the Memory Oriented Silicon Compiler (MOSC), described in this chapter, is to provide a tool that allows an IC designer to create RNS oriented realizations of DSP architectures in a rapid manner.

A. General Survey of Silicon Compilers

Since the Signals and Systems Group at the University of Windsor is interesting in digital signal processing applications, a survey of silicon compilers designed for DSP applications was carried out in order to determine state-of-the-art silicon compilation technology and to capture the techniques used in those compilers for constructing the MOSC compiler. Many silicon compilers have been proposed and built during the past decade. A general discussion will highlight three such CAD tools.

1. FIRST: developed at the University<sub>o</sub> of Edinburgh in 1982,

2. LAGER: developed at the University of California in 1986, and

3. BSSC: developed at the GÈ-Corporate R&D Centre in 1987. These CAD tools are chosen because of their focus on digital signal processing applications as opposed to general circuit design.

1. FIRST

10

FIRST (Fast Implementation of Real-Time Transforms [DeMR84]) is generally a bit-serial assembly tool [Deny82]. The input to this compiler is a structural description of a circuit, where each bit-serial operator and its interconnections must be specifically given. FIRST users have to take care to specify the exact connections between all basic cells. FIRST also requires users to determine the details of synchronization and timing throughout the complete circuits and to insert delay cells where necessary in the circuit. This task can be quite tedious and difficult to accomplish, especially when feedback mechanisms are involved.

This compiler first finds the corresponding cells, and then performs the placement of each cell and routes its signals. The floor

plan of circuits generated by this compiler is always fixed, so that the layout scheme may not work efficiently for large circuits, since cells are laid out in two horizontal rows only. The FIRST compiler also provides an interface to a functional simulator that can be used to generate test vectors. The first version of FIRST was built based on 5-micron nMOS technology. As described in [DeMR84], 2.5-micron CMOS technology is currently being investigated for the next version of the FIRST silicon compiler.

2. LAGER

LAGER [RaPB85] was developed at Berkeley and is essentially a datapath compiler with a pre-defined placement of the major components. In other words, circuits generated by LAGER are constructed in a fixed floor plan. The basic components of this datapath compiler are several registers, variable-width shift registers, a variable-width ALU, RAM, ROM and input/output pads. Each circuit generated by LAGER contains the same basic elements, but the specified wordlength will cause the width of the data buses and the number of bit-slices in the ALU and the shift registers to vary.

The input to this compiler is very much like an assembly language program. Data-code stored in the ROM cells to control the datapath is generated from an assembly language-like input file. Therefore, a LAGER user must write out detailed code for each nonprimitive operation, and the code must be specific to a given wordlength. The LAGER compiler is particularly not suitable in some applications involving the serial nature of communication between the major components.

3. BSSC

BSSC stands for Bit-Serial Silicon Compiler [YJHN87] and is again based upon bit-serial architecture [Deny82] as the FIRST compiler was. Basically, BSSC is a two-pass compiler. A "C" language type input file is first read into a behavioral-to-structural translator, and then a list of all the necessary cell instances and their interconnections are produced. In other words, a net-list which describes the interconnections of all necessary circuit components is generated. A gate level simulation can also be performed by a lowlevel simulator. A layout generation system is then invoked to place instantianted cells all the the chip and on route their interconnections.

The structure of all basic cells used in BSSC is well defined. In each cell, every input is 1-bit wide. The power bus and the clock signals are placed along the top of a cell. The ground bus and the complemented clock signals appear along the bottom of the cell. The port locations, for connection purpose, are standardized for all cells. All basic cells for arithmetic operators, relational operators and logical operators are laid out manually based on a 1.25-micron twolevel metal CMOS process. One interesting feature of BSSC is that interfaces are provided to various verification tools, such as, a design rule checker and a connectivity checker.

As mentioned above, all of these compilers generate circuits in a fixed floor plan, and use hand-crafted standard cells. The MOSC silicon compiler also follows this trend. However, the MOSC compiler is not a complete circuit mask layout generator but instead it allows

circuit designers to generate basic RNS arithmetic operators in a rapid and efficient manner.

B. Residue Number System and RNS Arithmetic Operations

The MOSC compiler has been developed based upon the concepts of Residue Number System (RNS) [Garn59] and capitalizes on the extensive research conducted by members of the Signals and Systems Group. Before delving into the details of this specialized silicon compiler, let us look at the residue number system. The mathematical advantages and disadvantages of RNS have been known for decades. This mathematically mature topic, however, has not enjoyed the popularity of the weighted magnitude numbering systems, such as, the binary number system. Therefore, a review of RNS will be presented.

Let  $(m_1, m_2,..., m_L)$  be a set of relatively prime integers (moduli), ie, no common factor, and let X be an integer in the range of [0,M-1] which is the dynamic range provided by the moduli.

where  $M = \Pi(m_i)$  (1)

Then by a simple operation, there exists integers  $k_i$ ,  $x_i$  such that

$X = k_i^* m_i + x_i$  for i =1, 2,...,L (2) The quantity  $x_i$  is called the i<sup>th</sup> residue of X, and is usually denoted as

$$x_i = X \mod m_i \tag{3}$$

For example, we have a number, X = 1462, and a set of moduli (32, 31, 29, 27) is selected. The dynamic range is hence equal to

$$M = 32*31*29*27 = 776736$$

$$M \neq 2^{19.57}$$

It requires almost 20 bits to represent the same number in the binary system. Then,

$x_1 = 1462 \mod 32 = 22$   $x_2 = 1462 \mod 31 = 5$   $x_3 = 1462 \mod 29 = 12$  $x_4 = 1462 \mod 27 = 4$

Hence, X = (22, 5, 12, 4)

Obviously X and (M + X) have the same residue representation. Only if X is within the dynamic range [0, M-1], can X then be uniquely determined by the L-tuple  $(x_1, x_2, ..., x_L)$ . In this case, denoted as

$X = (x_1, x_2, ..., x_L)$

Inversion of a residue L-tuple can be performed through the use of the so-called Chinese Remainder Theorem (CRT) [Garn59]. Consider the residue number system with moduli  $(m_1, m_2, ..., m_L)$  where the corresponding digits are labeled  $(x_1, x_2, ..., x_L)$ . The following equations define the conversion process.

$a_1A_1(M/m_1) + a_2A_2(M/m_2) + ... + a_LA_L(M/m_L) = X \mod M$  (4) where

$A_i(M/m_i) = 1 \mod m_i$

(5)

$\mathcal{O}$

For instance, a set of moduli (32, 31, 29, 27) is chosen, and the residue numbers are (22, 5, 12, 4).

Now,

$$m_1 = 32, m_2 = 31, m_3 = 29, m_4 = 27$$

$M = 32*31*29*27$

$M = 776736$

and  $24273 A_1 = 1 \mod 32$

$17 A_1 = 1 \mod 32 \Longrightarrow A_1 = 17$

25056

$$A_2 = 1 \mod 31$$

8  $A_2 = 1 \mod 31 ==> A_2 = 4$

26784  $A_3 = 1 \mod 29$

17  $A_3 = 1 \mod 29 ==> A_3 = 12$

28768  $A_4 = 1 \mod 27$

13  $A_4 = 1 \mod 27 ==> A_4 = 25$

$x_1 = 22, x_2 = 5, x_3 = 12, x_4 = 4$

and

Then,

$\langle X \rangle$

24273\*17\*22 + 25056\*4\*5 + 26784\*12\*12 + 28768\*25\*4=16312918and 16312918 = X mod 776736 \* Hence, X = 1462

is what was expected.

Let X, Y be within the dynamic range with respect to a set of moduli m<sub>i</sub>.

and

# $X = (x_1, x_2, ..., x_L)$ $Y = (y_1, y_2, ..., y_L)$

If

0 <= XY < M,

then

$Z = X \circ Y = (z_1, z_2, ..., z_I)$

(6)

where  $z_i = (x_i \circ y_i) \mod m_i$ , for i = 1, 2, ..., Land o denotes the operation of modular addition, subtraction or multiplication.

Let us now look at examples of RNS addition and multiplication by considering the numbers: (32, 31 29, 27) as a set of moduli. Suppose X = 800 and Y = 662then, for RNS addition,

Z = X + Y

|     | 800 = (0, 25, 17, 17)    |     |

|-----|--------------------------|-----|

|     | + 662 = (22, 11, 24, 14) |     |

|     | 1462 (22, 36, 41, 31)    | (a) |

| ınd | Z = (22, 5, 12, 4)       | (b) |

and

where the result in line (b) comes from the remainder of the result in line  $(\varepsilon)$  with respect to the corresponding moduli.

For RNS multiplication, such as,

| Z = X * Y           |     | •   |       |

|---------------------|-----|-----|-------|

| 800 = ( 0,          | 25, | 17, | 17)   |

| <u>* 662 = (22,</u> | 11, | 24, | 14)   |

| 529600 ( 0,         |     |     |       |

| Z = (0,             | 27, | 2,  | , 22) |

it is clear that the suboperation with each modulus is independent of the other. No carry information needs to be passed between the moduli. The absence of any carry requirements means that the concept of the-most and least significant digits is not valid. Thus, parallel architectures can be designed to process all modular partial sums and products concurrently. This parallelism can provide the basis for a speed-up of arithmetic operations, as illustrated in [JeLe77].

RNS arithmetic is exact and therefore free of roundoff error. However, it is this exactness that is often considered as a RNS limitation. The disadvantage of the RNS system is that division, sign detection, and magnitude comparison are inherently difficult operations. Even with these limitations, the usefulness of RNS in digital signal processing applications cannot be denied. For instance, in finite impulse response (FIR) digital filter design, the parallel

realization of RNS addition and multiplication operations results in high speed FIR filters.

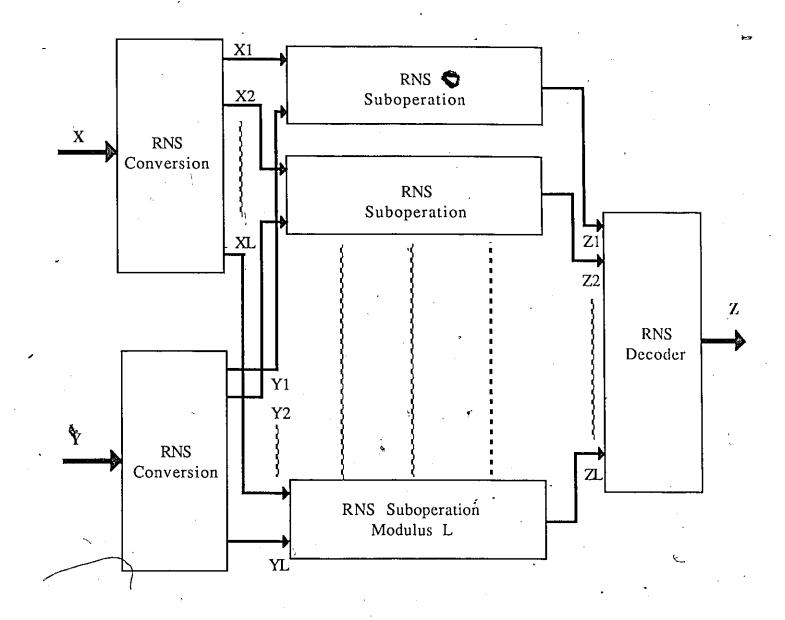

As described above, the RNS operations are divided into three major steps: RNS conversion, RNS operations and RNS decoding as illustrated in Figure 3.1.

When interfacing with the binary number system the required RNS conversion can be carried out by a binary-to-residue conversion cell, and the required RNS decoding by a residue-to-binary conversion cell. A number of conversion algorithms [TaRa81] have been developed to perform the conversion process efficiently. Here we shall concentrate on an effective hardware implementation of RNS arithmetic operators. These arithmetic operators may be required in a CRT-based decoder [RaTa86].

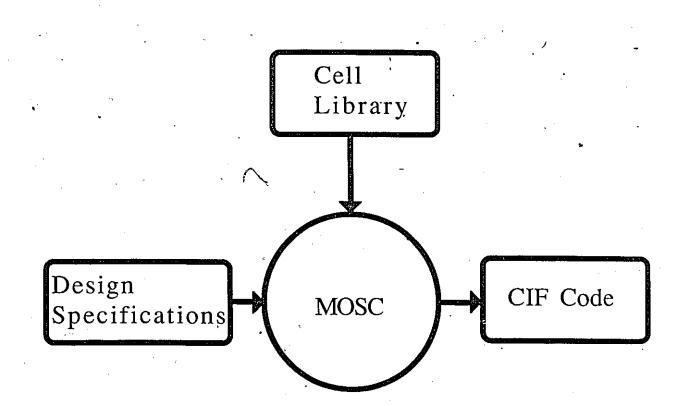

C. Memory Oriented Structure for RNS Operations

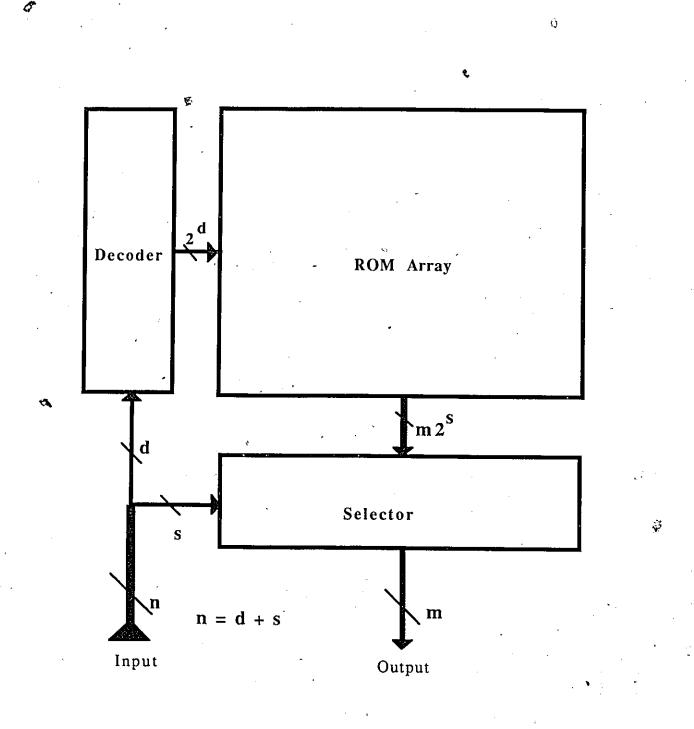

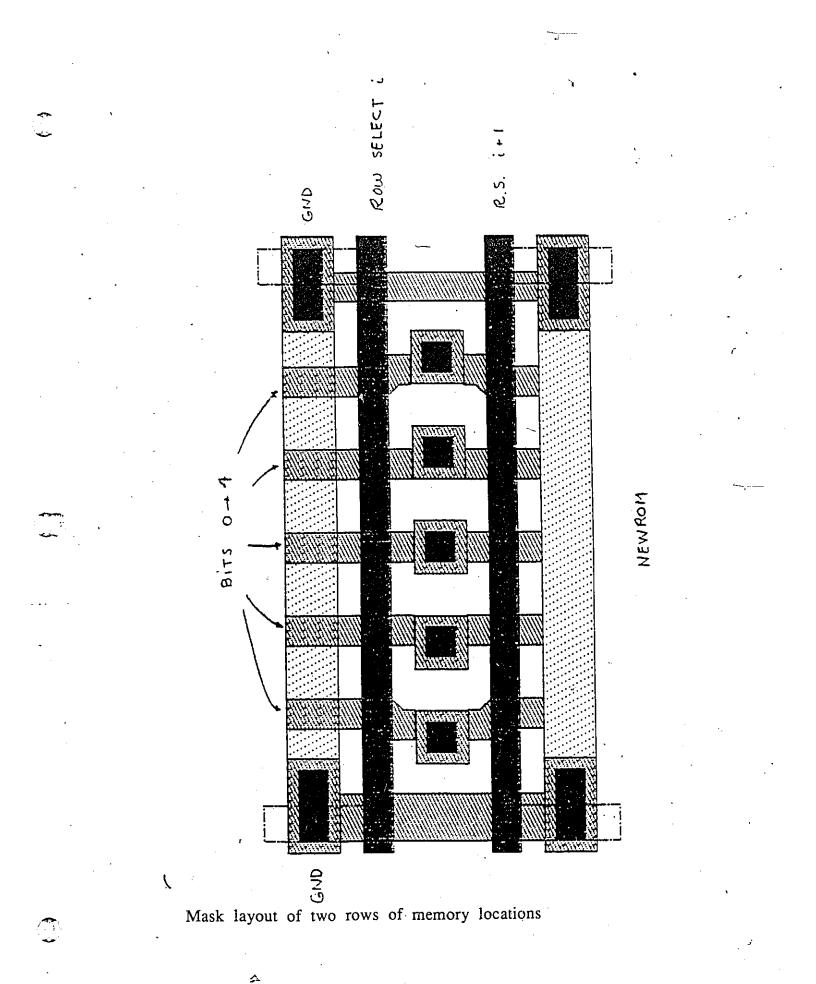

A common implementation approach used in constructing RNS modular arithmetic operators is based on the table look-up method, [BaJM87], [RaTa86], [BaCo82] and [Tayl82]. High-speed RNS arithmetic operations can be achieved not only because of the parallel nature of RNS, but also since a high-speed residue memory structure is used intensively to store information for the RNS functions. The residue structure is basically a Read-Only-Memory (ROM) cell. A ROM cell can be constructed out of a decoder, a ROM table, and a selector as shown in Figure 3.2. The ROM cell in Figure 3.2 has a n-bit input and a m-bit output.

For example, a residue multiplier for modulo-27 requires two 5-bit inputs (multiplicand and multiplier) and produces a 5-bit output. In this case, n=10 and m=5. The complete multiplication table

Figure 3.1: Major Components in Closed RNS

٩

2.

42

-

can be stored in a single (1024 or  $2^{10}$  X 5)-bit ROM. Since only 729 of the possible 1024 input combinations are valid, the rest of memory cells are not used. On the other hand, the modular multiplier can be implemented in several smaller ROM cells. As described in the previous section, the RNS is a special integer system. Since the multiplication and addition of integers does not require carry information, the operations in each RNS modulus can be performed independently. A curious feature of the RNS is that instead of using a single long wordlength, which provides a large dynamic range, several short wordlength residue structures are parallelled to obtain a sufficient dynamic range while maintaining a fast throughput data flow. Hence, most RNS operations can be formed by dividing the whole operation into a number of suboperations. Each suboperation is realized by cascading a number of the memory oriented cells together to form an array. Each of memory cells has pre-defined memory content. A major advantage in using memory cell arrays to realize the RNS operators is the ease of pipelining for high-speed throughput rate [BaJM87].

Ø.

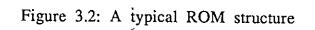

A memory oriented architecture which, is highly pipelined has been proposed by [TaJM87]. This architecture basically consists of a ROM cell, latches and switching circuitry as shown in Figure 3.3. As illustrated in [TaJM87], this memory oriented structure is/ appropriated for RNS operations stated in equation (6). As shown in Figure 3.3, if  $A_i$  is equal to 1, the output would be equal to the content of a memory cell which is uniquely determined by the input **B**. On the other hand, if  $A_{i_i}$  is equal to 0, the output is the same as the input **B** because the selection variable  $A_i$  forces the input to bypass

the ROM cell. Pipelining is achieved by including a number of latches in the structure and switching the signal lines of input A. Obviously, this structure can only communicate with its closest neighbour. Based on its highly pipelined structure and memory content selection mechanism, this memory oriented structure is chosen as the most fundamental building block used in the MOSC silicon compiler for constructing various RNS operators. If several building blocks are connected, a linear systolic array or ROM array is formed.

ふ

(7)

#### D. Hardware Realization of RNS Operators

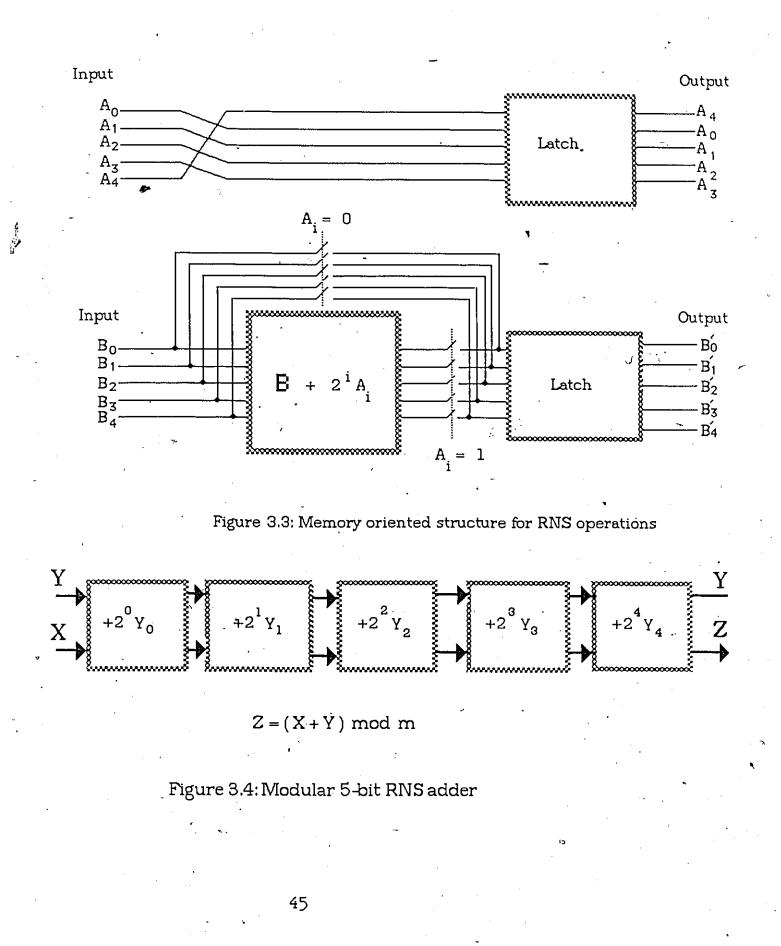

Once a memory oriented structure has been identified to be the building block for RNS operations, we then wish to examine the structure of modular adder in detail. For example, if we wish to use modulo-m to add two 5-bit numbers, X and Y, we use equation (6).

$Z = X \circ Y$

f

$$Z = (X + Y) \mod m$$

$$Z = (2^{4}Y_{4} + 2^{3}Y_{3} + 2^{2}Y_{2} + 2^{1}Y_{1} + 2^{0}Y_{0} + X) \mod m$$

Now equation (7) can be further divided into five simpler steps:  $sum_0 = (2^0Y_0 + X) \mod m$   $sum_1 = (2^1Y_1 + sum_0) \mod m$  $sum_2 = (2^2Y_2 + sum_1) \mod m$

$sum_3 = (2^3Y_3 + sum_2) \mod m$

$Z = (2^4Y_4 + sum_3) \mod m$

The output of each suboperation also has a 5-bit width and is the input of next suboperation, except for the last step. Obviously, five basic cells are required to construct a 5-bit modular adder and they are cascaded to form a linear array, as shown in Figure 3.4. Each cell stores pre-defined memory content.

The memory content of each cell is equal to the input  $(X, sum_0 to sum_3)$  plus the appropriate power of two and the input Y acts like a memory content selector. For a modulo-31 adder, the memory content of the five cells is shown in Table 3.1. If we wish to add two numbers: 11 and 25, we have

٠

| I/P      | cell0 -            | cell1             | cell2              | cell3      | cell4 .         | O/P      |

|----------|--------------------|-------------------|--------------------|------------|-----------------|----------|

|          | 0> 1               | 0> 2              | 0> 4               | 0> 8       | 0>16            |          |

|          | 1> 2               | 1> 3              | 1> 5               | 1> 9       | 1>17            |          |

| •        | 2> 3               | 2> 4 <sup>·</sup> | 2> 6               | 2>10       | 2>18            |          |

|          | 3> 4 、             | 3> 5              | 3> 7               | 3>11       | 3>19 ·          |          |

| ,        | 4> 5               | 4> 6              | 4> 8               | 4>12       | 4>20            |          |

|          | 5> 6               | 5> 7              | 5> 9               | 5>13       | 5>21            |          |

|          | 6> 7               | 6> 8              | 6>10               | 6>14       | 6>22            |          |

| •        | 7> 8               | 7> 9              | 7>11               | 7>15       | 7>23            |          |

|          | 8> 9               |                   | 8>12               |            | 8>24            |          |

|          | 9>10               | 9>11              | 9>13               | 9>17       | 9 <u>-</u> ->25 |          |

|          |                    |                   | 10>14              |            |                 |          |

| 1->      | 11>12              | 11>13             | 11>15              | 11>19      | 11>27           | 1        |

|          |                    |                   | 12>16 2-           | >12>20     | 12>28           | 1        |

| •        |                    | 13>15             |                    | 13>21      |                 |          |

|          |                    |                   | 14>18              |            |                 |          |

|          | 15>16              | 15>17             | 15>19              | 15>23      | 15> 0           |          |

| •        | 16>17              |                   |                    | 16>24      | 16> 1           |          |

| •.       |                    | 17>19             |                    |            | 17> 2           |          |

|          |                    |                   | 18>22              |            |                 |          |

| <u>م</u> |                    |                   | 19>23              |            | 19> 4           |          |

|          | 20>21              | 20>22             | 20>24              | 20>28 3->2 | 20> 5 >>>>      | >>5*     |

| -        | 21>22              | 21>23             | 21>25              | 21>29      | *21> 6          | ,        |

|          | 22>23              | 22>24             | 22>26              | 22>30      | 22> 7           |          |

|          | 23>24              | 23>25             | 23>27              | 23> 0      | 23> 8           |          |

| · · ·    | . 24>25            | 24>26             |                    | 24> 1      |                 | -        |

| , -      | 25>26 <sub>2</sub> | 25>27             | 25>29              | 25> .2     | 25>10           |          |

| · ·      | 26>27              | 26>28             | 26>30              | 26> 3      | 26>11           |          |

|          |                    | 27>29             |                    | 27> 4      | 27>12           |          |

|          |                    | 28>30             | 28> i              | 28> 5      | 28>13           | <b>、</b> |

|          |                    | 29> 0             | 29> 2 <sup>-</sup> | 29> 6      | 29>14           |          |

|          | 30>_0              | 30> 1             | 30> 3              | 30> 7      | 30>15           | -        |

|          | 31> 1              | 31> 2             | 31> 4              | 31> 8      | 31:->16 .       |          |

|          |                    |                   |                    |            |                 |          |

Table 3.1: Memory content for 5-bit modular addition

Kardin Streemen

$Z = (X + Y) \mod m$

$$= (11 + 25) \mod 31$$

and the number 25 can be represented in a 5-bit binary form as 11001. Since the number Y = 25 is the memory content selector, *cell0, cell3* and *cell4* are selected. As illustrated in the Table 3.1, in the first step, the number 11 acts as an address to the first memory cell. The output of 12 is then used in the second step as an address to *cell3*. The output is 20. Again, the number 20 is the input to *cell4*. The corresponding output is 5 so that the final result is 5. Now, if we double check the result, we have

$Z = (42 + 25) \mod 31$ = (36) mod 31 = 5

As was obtained from the five cascaded memory cells.

Once the concept of the modular addition using the five cascaded memory cells is understood, the same memory cells, with different memory content, can be used to construct a modular subtractor. RNS subtraction is accomplished using the additive inverse of the positive residue representation [Garn59]. The additive inverse of a residue number, n, is defined by the following equation,

$$\mathbf{n} + \mathbf{n'} = \mathbf{0} \tag{8}$$

For example, if we wish to subtract 25 from 11, we have

$Z = (X - Y) \mod m$

$= (11 - 25) \mod 31$

$= (-14) \mod 31$  (because  $(17 + 14) \mod 31 = 0$ ) = 17

(9)

The memory contents of the five cells used for subtraction are tabulated in Table 3.2. Using the same procedures as in the modular addition, one would get 17 as is indicated in step 3 shown in Table 3.2. The result is also equal to the one in (9).

| I/P | cell0 | cell1  | cell2    | cell3   | cell4     | O/P  |

|-----|-------|--------|----------|---------|-----------|------|

|     | 0>30  | 0>29   | 0>27     | 0>23    | 0>15      |      |

|     | 1> 0  | 1>30   | 1>28     | 1>24    | 1>16      |      |

|     | 2> 1  | 2> 0   | 2>29     |         | 2>17 >>>> | >17* |

|     | 3> 2  | 3> 1   | 3>30     | 3>26    | 3>18      |      |

|     | 4> 3  | 4> 2 . | 4> 0     | 4>27    | 4>19      |      |

|     | 5> 4  | 5> 3   | 5> 1     | 5>28    | 5>20      |      |

|     | 6> 5  | 6> 4   | 6> 2     | 6>29    | 6>21      |      |

|     | 7> 6  | 7> 5   | 7> 3     | 7>30    | 7>22      |      |

|     | 8> 7  | 8> 6   | 8> 4     | 8> 0    | 8>23      |      |

|     | 9> 8  | 9> 7   | 9> 5     | 9> 1    | 9>24      |      |

|     | 10> 9 | 10> 8  | 10> 6 2- | ->10> 2 | 10>25     |      |

| 1-> | 11>10 | 11> 9  | 11> 7    | 11> 3   | 11>26     |      |

|     | 12>11 | 12>10  | 12> 8    | 12> 4   | 12>27     |      |

|     | 13>12 | 13>11  | 13> 9    | 13> 5   | 13>28     |      |

|     | 14>13 | 14>12  | 14>10    | 14> 6   | 14>29     |      |

|     | 15>14 | 15>13  | 15>11    | 15> 7   | 15>30     | 2    |

|     | 16>15 | 16>14  | 16>12    | 16> 8   | 16> 0     | .*   |

| ,   | 17>16 | 17>15  | 17>13    | 17> 9   | 17> 1     |      |

|     | 18>17 | 18>16  | 18>14    | 18>10   | 18> 2     |      |

| /   | 19>18 | 19>17  | 19>15    | 19>11   | 19> 3     | •    |

|     | 20>19 | 20>18  | 20>16    | 20>12   | 20> 4     |      |

|     | 21>20 | 21>19  | 21>17    | 21>13   | 21> 5     |      |

|     | 22>21 | 22>20  | 22>18    | 22>14   | 22> 6     | ·    |

|     | 23>22 | 23>21  | 23>19    | 23>15   | 23> 7     |      |

|     | 24>23 | 24>22  | 24>20    | 24>16   | 24> 8     |      |

|     | 25>24 | 25>23  | 25>21    | 25>17   | 25> 9     | £    |

|     | 26>25 | 26>24  | 26>22    | 26>18   | 26>10     | •    |

|     | 27>26 | 27>25  | 27>23    | 27>19   | 27>11     |      |

| -   | 28>27 | 28>26  | 28>24    | 28>20   | 28>12     |      |

|     | 29>28 | 29>27  | 29>25    | 29>21   | 29>13     |      |

| ,   | 30>29 | 30>28  | 30>26    | 30>22   | 30>14     |      |

|     | 31>30 | 31>29  | 31>27    | 31>23   | 31>15     |      |

| .*  |       |        |          |         |           |      |

Table 3.2: Memory content for 5-bit modular subtraction

48

ø

With a pre-defined memory content in the cascaded memory cells, the savings in the number of memory locations is extremely attractive. If a single regular ROM cell is used to store all possible outputs of 5-bit modular addition or subtraction, it would take  $2^{10}$  or 1024 memory locations. However, only 160 memory locations are needed to perform the same operation in this linear memory array.

Based upon the RNS addition and subtraction operations, we can construct a modular multiplier. A modulo-m multiplier can be realized using the Quarter Square Multiplication method [BaJM87a]:

$\mathbf{Z} = (\mathbf{X} * \mathbf{Y}) \mod \mathbf{m}$

كسك

i.

ľ

= (  $((X+Y)^2/4$  ) mod m -  $((X-Y)^2/4$  ) mod m ) mod m (10) where the quantity ((  $(*)^2/4$  ) mod m ) is also stored in a lookup -table. According to the equation (10), one addition, two subtractions and two quarter square operations are required. A conceptual block diagram of the modular multiplier is shown in Figure 3.5. The memory content, C, of a quarter square operator is determined by the following equation:

$C = (|address^2/4|) \mod m$  (11) The content C for modulo-31 is shown in Table 3.3. For instance, if we wish to use modulo-31 to multiply two residue number; 11 and 25, we have

$Z = (X * Y) \mod m$   $Z = (11 * 25) \mod 31$   $Z = (275) \mod 31$ Z = 27

Now let us use the quarter square multiplication method.

$Z = (11 * 25) \mod 31$

50

C

Then,  $Z = ((11+25)^2/4 - (11-25)^2/4) \mod 31$

From the previous addition and subtraction examples, we have

$(11 + 25) \mod 31 = 5$

and  $(11 - 25) \mod 31 = 17$

| 0> 0  | 11> 30   | 22> 28 |    |

|-------|----------|--------|----|

| 1> 0  | 12> 5    | 23> 8  |    |

| 2> 1  | 13> 11   | 24> 20 |    |

| 3> 2  | 14> 18   | 25> 1  |    |

| 4> 4  | - 15> 25 | 26> 14 | Q. |

| 5> 6* | 16> 2    | 27> 27 |    |

| 6> .9 | 17> 10*  | 28> 10 |    |

| 7>12  | 18> 19   | 29> 24 |    |

| 8>16  | 19> 28   | 30> 8  |    |

| 9>20  | 20> 7    | 31> 23 |    |

| 10>25 | 21> 17   |        |    |

|       |          |        |    |