# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1996

# Artificial neural network models for digital implementation.

Chuan Zhang. Tang University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Tang, Chuan Zhang., "Artificial neural network models for digital implementation." (1996). *Electronic Theses and Dissertations*. 1213.

https://scholar.uwindsor.ca/etd/1213

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

# **UMI**

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

### **ARTIFICIAL NEURAL NETWORK MODELS FOR**

### DIGITAL IMPLEMENTATION

by

**Chuan Zhang TANG**

A Dissertation Submitted to the Faculty of Graduate Studies and Research Through the Department of Electrical Engineering in Partial Fulfilment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario, Canada

Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada services hibliographiqu

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérance

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-30298-9

# Canadä

(c) 1996 Chuan Zhang Tang

### ARTIFICIAL NEURAL NETWORK MODELS FOR DIGITAL IMPLEMENTATION

by

Chuan Zhang Tang

Doctor of Philosophy in Electrical Engineering, 1996 University of Windsor, Windsor, Ontario, Canada N9B 3P4 Supervisor: Dr. Hon Keung Kwan

The last decade has witnessed the revival and a new surge in the field of artificial neural network research. This is a thoroughly interdisciplinary area, covering neurosciences, physics, mathematics, economics, and electronics. Although artificial neural networks have found diverse applications in pattern recognition, signal processing, communications, control systems, optimization, among others, this is still a research field with many open problems in the areas of theory, applications, and implementations. Compared with the development in neural network theories, hardware implementation has lagged behind. In order to take full advantages of neural networks, dedicated hardware implementations are definitely needed. Today, harnessing VLSI technology to produce efficient implementations of neural networks may be the key to the future growth and ultimate success of neural network techniques.

This dissertation deals with the development of neural network models

iv

implementation technologies are basically a digital implementation medium, which offers many advantages over its analog counterpart, artificial neural networks must be adapted to an all-digital model in order to benefit from those advanced technologies. In this dissertation, new models of multilayer feedforward neural networks with single term powers-of-two weights, quantized neurons, and simplified activation functions are proposed to facilitate the hardware implementation in digital approach. Dedicated training algorithms and design procedures for these models are also developed. To demonstrate the feasibility of the presented models, performance analysis and simulation results are provided, and VHDL and FPGA designs are implemented. It has been shown that these proposed models can achieve almost the same performance as the original multilayer feedforward networks while obtaining significant improvement in digital hardware implementation in terms of silicon area and operation speed. By using the models developed in this dissertation, a digital implementation approach of multilayer feedforward neural networks becomes verv attractive.

To my wife, Barbara Zhou, my son, Joshua Tang,

,

and

my parents, Shi-xian Tang and Kun-shu Ma

vi

First of all, I would like to acknowledge my dissertation supervisor, Dr. H. K. Kwan, for helpful advice and useful suggestions throughout the progress of my dissertation. Dr. Kwan has introduced me into this exciting field of artificial neural networks (ANNs) and recommended the multiplierless digital implementation of ANNs as my research direction. I would also like to thank Dr. Kwan for providing me research assistantship through his NSERC research grant, and the Department of Electrical Engineering for providing me teaching assistantship. I would like to acknowledge the University of Windsor for granting me the University of Windsor Postgraduate Scholarship (1991-1993) and the Ontario Graduate Scholarship program for awarding me the Ontario Graduate Scholarship (1993-1995).

I am grateful to my external examiner, Dr. M. I. Elmasry of the University of Waterloo, who examined and provided useful comments on the dissertation. Special thanks go to my outside department reader, Dr. R. Du, for his constructive comments on this research. I want to express my sincere thanks to my department reader, Dr. G. A. Jullien, for comments that improved the presentation of this research. I also like to thank Dr. W. C. Miller for serving as my department reader and for his helpful comments. My thanks also go to Ms. S. Ouellette, Mr. J. Novosad, and Mr. A. Johns for their assistance during the progress of this research.

Finally, I wish to express my sincere appreciation to my wife for her constant encouragement and understanding, and to my parents for their care and affection.

vii

# TABLE OF CONTENTS

| ABSTRACT              | iv  |

|-----------------------|-----|

| DEDICATION            | vi  |

| ACKNOWLEDGEMENTS      | vii |

| LIST OF TABLES        | xii |

| LIST OF ILLUSTRATIONS | xv  |

### CHAPTER

| 1. | INTR | ODUCTION                                | 1  |

|----|------|-----------------------------------------|----|

|    | 1.1  | History of Artificial Neural Networks   | 2  |

|    | 1.2  | ANN Features                            | 6  |

|    | 1.3  | Motivations and Impact of this Research | 10 |

|    | 1.4  | Literature Survey                       | 14 |

|    | 1.5  | Organization of this Dissertation       | 18 |

| 2. | MUL  | TILAYER FEEDFORWARD NEURAL NETWORKS     | 20 |

|    | 2.1  | MFNN Architecture                       | 20 |

|    | 2.2  | The Backpropagation Algorithm           | 26 |

|    | 2.3  | Improvements to the BP Algorithm        | 30 |

|    |      | 2.3.1 Adjustable Learning Rate          | 30 |

|    |      | 2.3.2 Momentum Term                     | 31 |

|    |      |                                         |    |

viii

|    | 2.4  | Hardware Implementations of MFNNs                  | 34 |

|----|------|----------------------------------------------------|----|

| 3. | MUL  | TILAYER FEEDFORWARD NEURAL NETWORKS WITH           |    |

|    | SING | LE TERM POWERS-OF-TWO WEIGHTS                      | 36 |

|    | 3.1  | Adaptation of Activation Functions in MFNNs        | 38 |

|    | 3.2  | Design Procedures for MFNNs with STPT Weights      | 41 |

|    |      | 3.2.1 Basic Ideas                                  | 41 |

|    |      | 3.2.2 Design Algorithm                             | 45 |

|    | 3.3  | Simulation Results                                 | 49 |

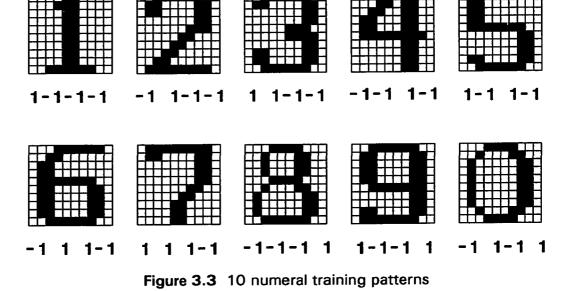

|    |      | 3.3.1 A Benchmark Problem                          | 49 |

|    |      | 3.3.2 More Simulations                             | 52 |

|    | 3.4  | Comparison with Existing Models                    | 56 |

|    | 3.5  | Advantages for Hardware Implementation             | 59 |

|    | 3.6  | Concluding Remarks                                 | 65 |

| 4. | MUL. | TILAYER FEEDFORWARD NEURAL NETWORKS WITH           |    |

|    | QUA  | NTIZED NEURONS                                     | 67 |

|    | 4.1  | Introduction                                       | 67 |

|    | 4.2  | Quantized Neurons                                  | 69 |

|    | 4.3  | Design Procedures for MFNNs with Quantized Neurons | 74 |

|    | 4.4  | Mapping Abilities of MFNNs with Quantized Neurons  | 77 |

|    | 4.5  | Simulation Results                                 | 78 |

|    |      | 4.5.1 Benchmark Problems                           | 78 |

|    |      | 4.5.2 More Simulations                             | 83 |

|    | 4.6  | Advantages for Hardware Implementation             | 90 |

|    | 4.7  | Concluding Remarks                                 | 96 |

ix

|                | DIGI | TAL IMPLEMENTATION                              | 98  |

|----------------|------|-------------------------------------------------|-----|

|                | 5.1  | A Simplified Sigmoid Activation Function (SSAF) | 98  |

|                |      | 5.1.1 Second-Order Approximation                | 99  |

|                |      | 5.1.2 Considerations in Training and            |     |

|                |      | Implementation                                  | 102 |

|                |      | 5.1.3 Simulation Results                        | 107 |

|                | 5.2  | MFNNs with SSAFs and STPT Weights               | 109 |

|                |      | 5.2.1 Design Algorithm                          | 109 |

|                |      | 5.2.2 Simulation Results                        | 112 |

|                | 5.3  | Multiplierless MFNNs for Continuous             |     |

|                |      | Input-Output Mapping                            | 115 |

|                |      | 5.3.1 Design Algorithm                          | 116 |

|                |      | 5.3.2 Simulation Results                        | 117 |

|                | 5.4  | Multiplierless MFNNs for Discrete               |     |

|                |      | Input-Output Mapping                            | 120 |

|                |      | 5.4.1 Design Algorithm                          | 121 |

|                |      | 5.4.2 Simulation Results                        | 123 |

|                | 5.5  | Concluding Remarks                              | 125 |

| 6.             | CON  | ICLUSIONS AND SUGGESTIONS                       | 127 |

|                | 6.1  | Conclusions                                     | 127 |

|                | 6.2  | Suggestions for Future Research                 | 130 |

| APPENDIX       | ,    |                                                 |     |

| AFFENDIA<br>A. | -    | IVATION OF THE BP ALGORITHM                     | 131 |

| А.             | DEN  |                                                 |     |

|                |      |                                                 |     |

## B. DERIVATION OF THE ALGORITHM FOR ADAPTATION

х

| C.        | AN F | PGA IMPLEMENTATION OF MFNNS WITH                      |     |

|-----------|------|-------------------------------------------------------|-----|

|           | QUAN | ITIZED NEURONS                                        | 138 |

|           | C.1  | Design Overview                                       | 138 |

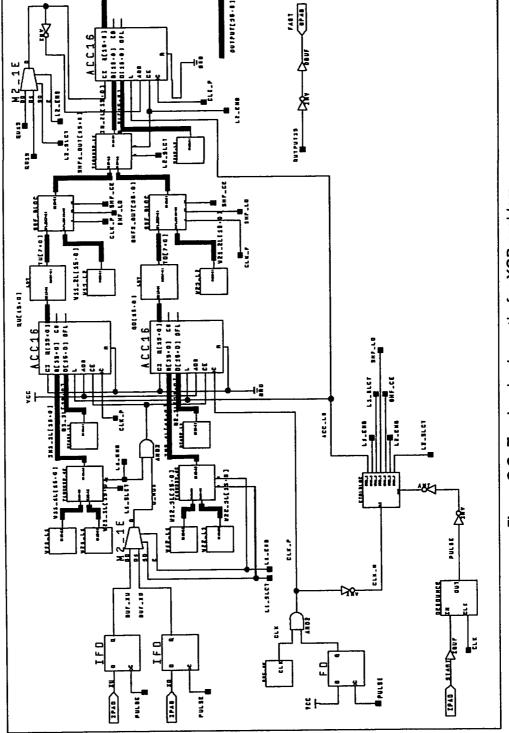

|           | C.2  | Top Level Schematic                                   | 143 |

|           | C.3  | Sub-Circuit Blocks                                    | 146 |

|           |      | C.3.1 Accumulator - ACC16                             | 146 |

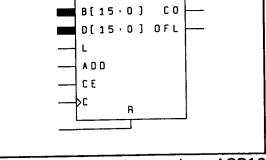

|           |      | C.3.2 LUT - Implementation of the Activation Function | 147 |

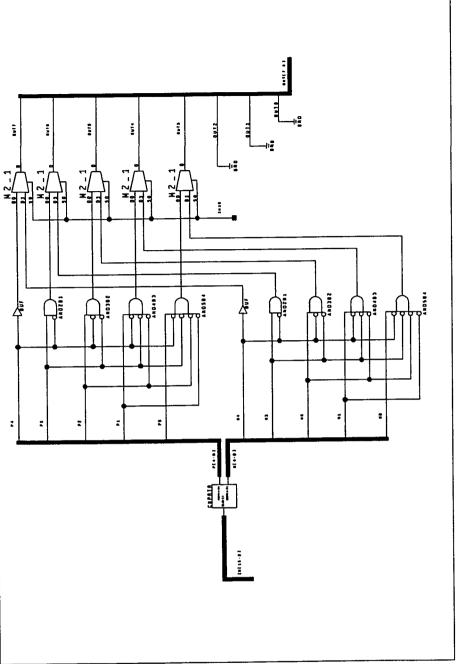

|           |      | C.3.3 SHF_BLOC - Implementation of Shift Operation    | 151 |

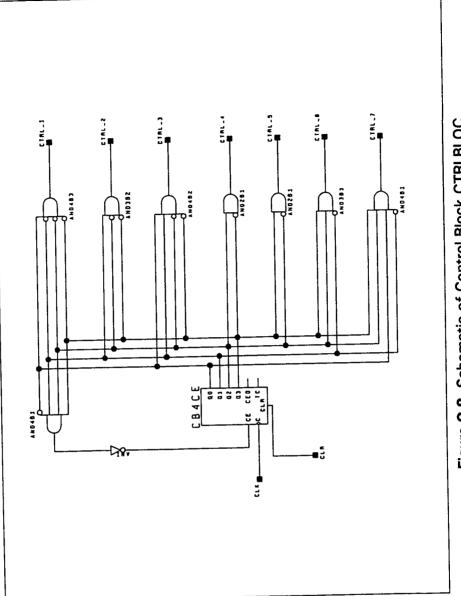

|           |      | C.3.4 CTRLBLOC - Implementation of the Control Block  | 153 |

|           |      | C.3.5 Weights and Biases                              | 154 |

|           | C.4  | Design Simulations                                    | 156 |

|           |      | C.4.1 Functional Simulation Results                   | 157 |

|           |      | C.4.2 Timing Simulation Results                       | 163 |

|           |      |                                                       |     |

| D.        | VHDL | CODES FOR HARDWARE IMPLEMENTATION SCHEMES             | 168 |

|           |      |                                                       |     |

| RENCES 17 |      |                                                       | 174 |

REFERENCES

**VITA AUCTORIS**

xi

| Table 3.1                           | Parameters for XOR Simulation                                                                                                                                                                                                                                    | 51                   |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Table 3.2                           | Convergence Speed (In Number of Epochs) for CMFNN and                                                                                                                                                                                                            |                      |

|                                     | STPT MFNN (100 Inputs, 4 Outputs, and 1 Hidden Layer)                                                                                                                                                                                                            | 54                   |

| Table 3.3                           | Generalization Capabilities (In Percentage of Correct                                                                                                                                                                                                            |                      |

|                                     | Recalls) for CMFNN and STPT MFNN (100 Inputs,                                                                                                                                                                                                                    |                      |

|                                     | 4 Outputs, and 1 Hidden Layer)                                                                                                                                                                                                                                   | 54                   |

| Table 3.4                           | Convergence Speed for Networks with Different Number                                                                                                                                                                                                             |                      |

|                                     | of Hidden Layers When $M = 4$ (100 Inputs and 4 Outputs)                                                                                                                                                                                                         | 55                   |

| Table 3.5                           | Generalization Capabilities for Networks with Different                                                                                                                                                                                                          |                      |

|                                     | Number of Hidden Layers When $M = 4$ (100 Inputs and                                                                                                                                                                                                             |                      |

|                                     |                                                                                                                                                                                                                                                                  |                      |

|                                     | 4 Outputs)                                                                                                                                                                                                                                                       | 55                   |

| Table 3.6                           | 4 Outputs)<br>Description of the Operation of the Shifter                                                                                                                                                                                                        | 55<br>61             |

| Table 3.6<br>Table 3.7              | •                                                                                                                                                                                                                                                                |                      |

|                                     | Description of the Operation of the Shifter                                                                                                                                                                                                                      | 61                   |

| Table 3.7                           | Description of the Operation of the Shifter<br>Hardware Advantage of MFNN with STPT Weights                                                                                                                                                                      | 61<br>63             |

| Table 3.7<br>Table 4.1              | Description of the Operation of the Shifter<br>Hardware Advantage of MFNN with STPT Weights<br>Description of Parity Problem                                                                                                                                     | 61<br>63             |

| Table 3.7<br>Table 4.1              | Description of the Operation of the Shifter<br>Hardware Advantage of MFNN with STPT Weights<br>Description of Parity Problem<br>Convergence Performance in Number of Training                                                                                    | 61<br>63<br>82       |

| Table 3.7<br>Table 4.1<br>Table 4.2 | Description of the Operation of the Shifter<br>Hardware Advantage of MFNN with STPT Weights<br>Description of Parity Problem<br>Convergence Performance in Number of Training<br>Epochs (One Hidden Layer)                                                       | 61<br>63<br>82       |

| Table 3.7<br>Table 4.1<br>Table 4.2 | Description of the Operation of the Shifter<br>Hardware Advantage of MFNN with STPT Weights<br>Description of Parity Problem<br>Convergence Performance in Number of Training<br>Epochs (One Hidden Layer)<br>Generalization Capability in Percentage of Correct | 61<br>63<br>82<br>85 |

xii

|           | Recalls (Two Hidden Layers, 5% Noise Level)              | 87  |

|-----------|----------------------------------------------------------|-----|

| Table 4.6 | Hardware Advantage of MFNN with Quantized Neurons        | 91  |

| Table 4.7 | Description of the Decoder for STPT Multistep Activation |     |

|           | Function                                                 | 92  |

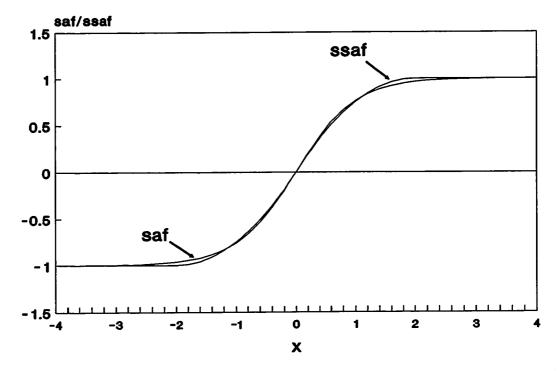

| Table 5.1 | Performance of SSAF and SAF for Two- and Three-Layer     |     |

|           | MFNNs                                                    | 108 |

| Table 5.2 | Convergence Speed and Generalization Capabilities of     |     |

|           | MFNNs with One Hidden Layer                              | 114 |

| Table 5.3 | Convergence Speed and Generalization Capabilities of     |     |

|           | MFNNs with Two Hidden Layers                             | 114 |

| Table 5.4 | Summary of Simulation Results                            | 119 |

| Table 5.5 | Convergence Speed (In Number of Epochs) of CMFNNs        |     |

|           | and MMFNNs                                               | 124 |

| Table 5.6 | Recall Performance (In Percentage of Correctness) of     |     |

|           | CMFNNs and MMFNNs                                        | 125 |

| Table C.1 | List of Symbols Used in the Design                       | 145 |

| Table C.2 | Combinatorial Logic in LUT Block                         | 148 |

| Table C.3 | Thresholds of Activation Functions                       | 153 |

| Table C.3 | Summary of Control Signals                               | 154 |

| Table C.4 | Representations of Weights and Biases                    | 156 |

| Table D.1 | VHDL Code for Shift Operation                            | 168 |

xiii

|           | Used in MFNN with Quantized Neurons                   | 170 |

|-----------|-------------------------------------------------------|-----|

| Table D.3 | VHDL Description of the Simplified Sigmoid Activation |     |

|           | Function                                              | 172 |

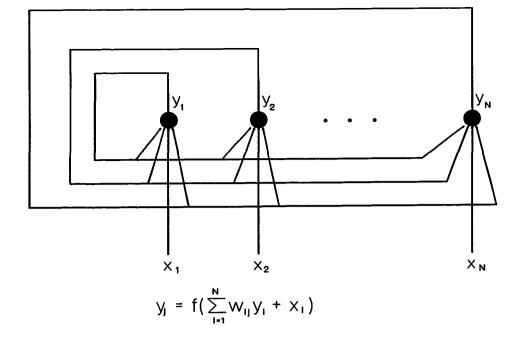

| Figure 1.1  | A Hopfield Neural Network                               | 8  |

|-------------|---------------------------------------------------------|----|

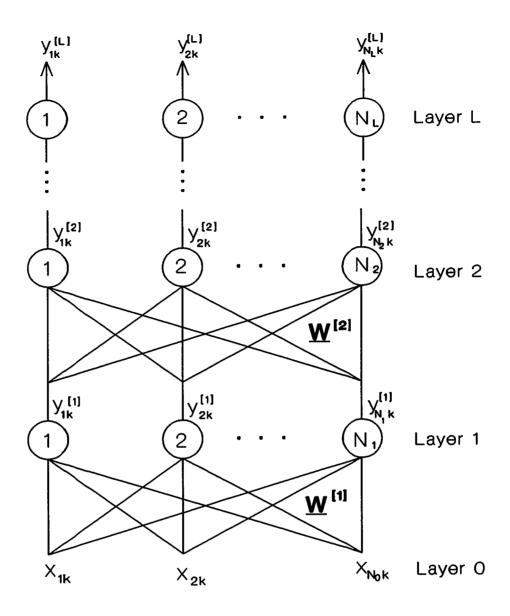

| Figure 2.1  | A Multilayer Feedforward Neural Network                 | 21 |

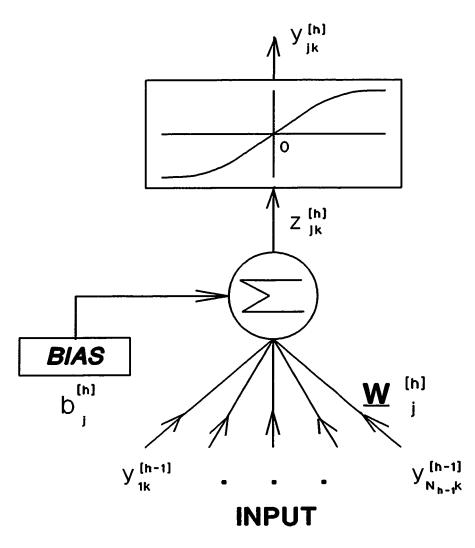

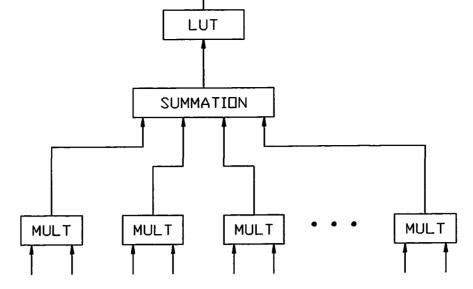

| Figure 2.2  | A Typical Neuron in MFNNs                               | 23 |

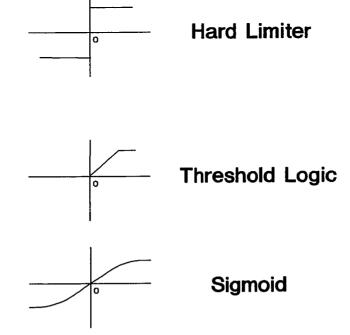

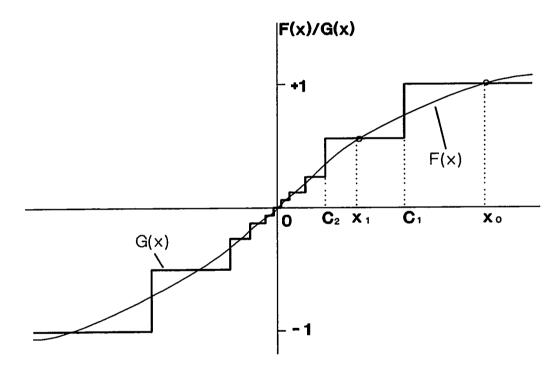

| Figure 2.3  | Commonly Used Nonlinear Activation Functions            | 24 |

| Figure 2.4  | Block Diagram of Direct Implementation of a             |    |

|             | Neuron in MFNNs                                         | 35 |

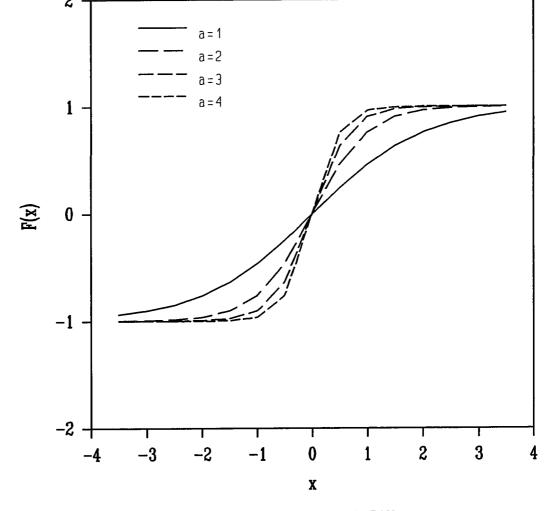

| Figure 3.1  | Sigmoid Functions with Different $a$                    | 40 |

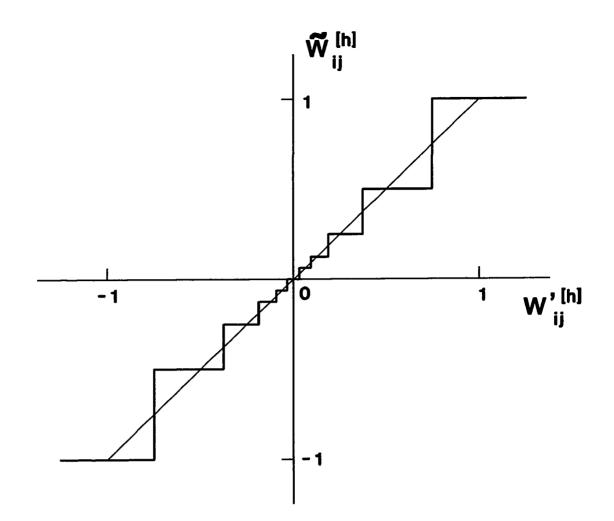

| Figure 3.2  | Weight Quantization Curve When $M = 4$                  | 45 |

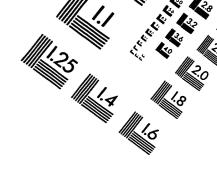

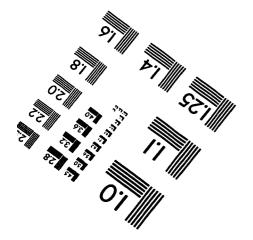

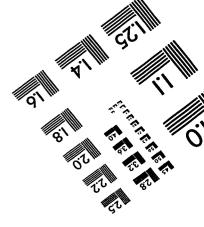

| Figure 3.3  | 10 Numeral Training Patterns                            | 53 |

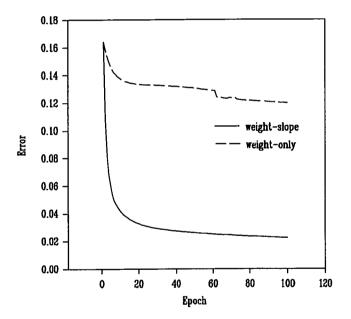

| Figure 3.4  | Error Curve When N <sub>h</sub> = 10                    | 57 |

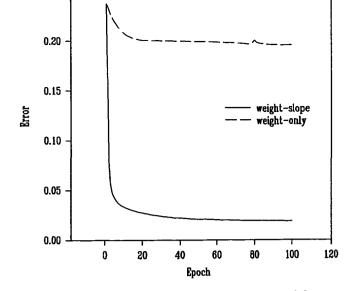

| Figure 3.5  | Error Curve When N <sub>h</sub> =20                     | 58 |

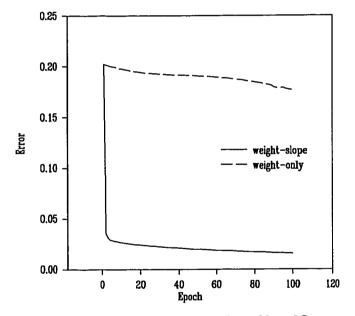

| Figure 3.6  | Error Curve When N <sub>h</sub> =40                     | 58 |

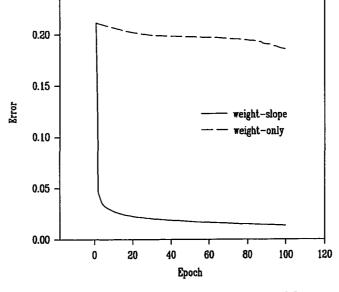

| Figure 3.7  | Error Curve When N <sub>h</sub> =60                     | 59 |

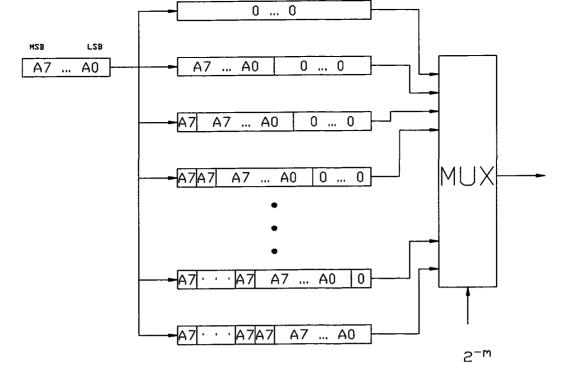

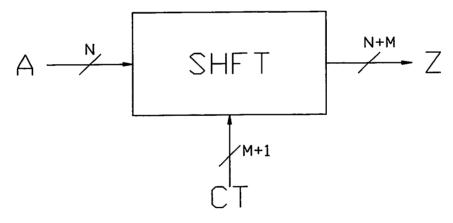

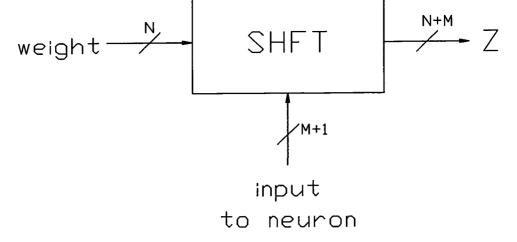

| Figure 3.8  | Illustration of the Shift Operation                     | 62 |

| Figure 3.9  | A Shifter                                               | 62 |

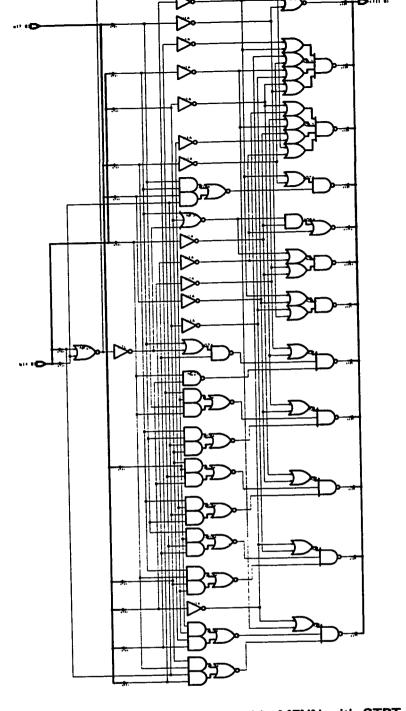

| Figure 3.10 | Schematic of the Shifter Used in MFNN with STPT Weights | 64 |

| Figure 4.1  | A Quantized Neuron                                      | 71 |

| Figure 4.2  | Original and Quantized Activation Functions             | 72 |

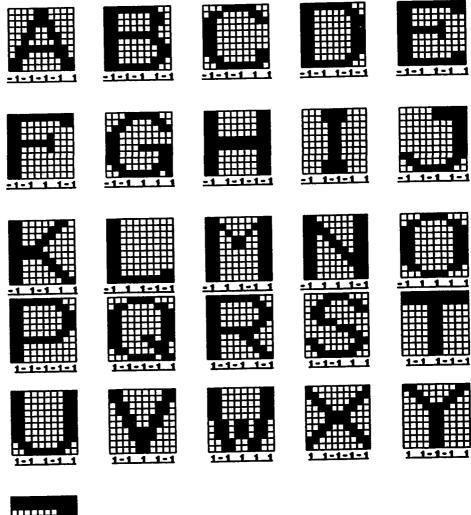

| Figure 4.3  | Training Patterns of the 26 Letters of the Alphabet     | 84 |

|             |                                                         |    |

xv

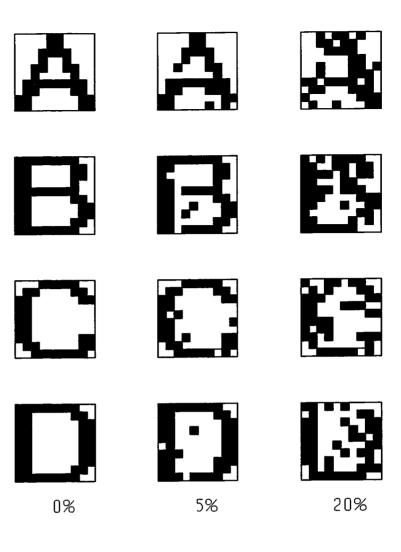

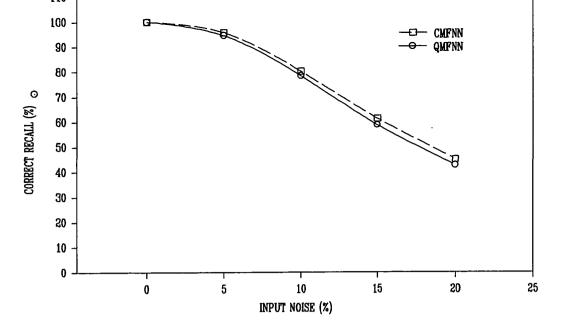

| Figure 4.5  | Recall Accuracy as a Function of Input Noise                 |     |

|-------------|--------------------------------------------------------------|-----|

|             | (20 Hidden Neurons)                                          | 89  |

| Figure 4.6  | A Shifter Used in MFNN with Quantized Neurons                | 91  |

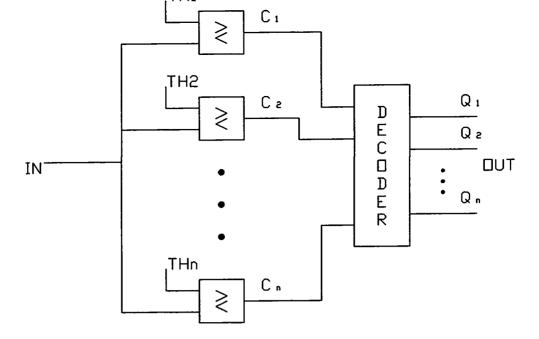

| Figure 4.7  | Block Diagram of the STPT Multistep Activation Function      | 93  |

| Figure 4.8  | Multistep Activation Function Circuitry                      | 94  |

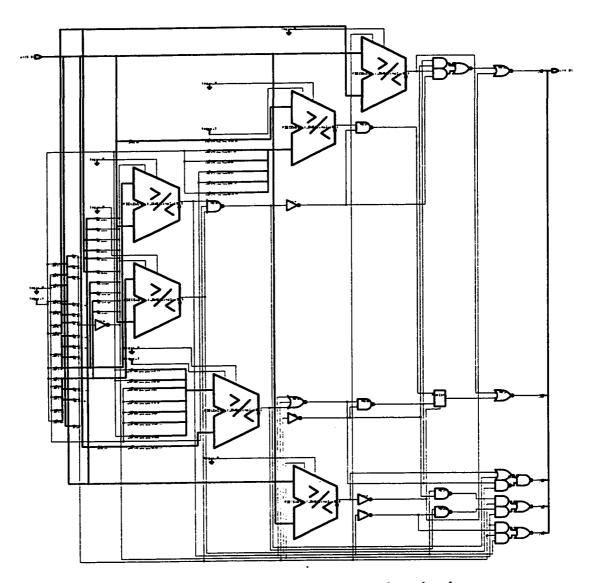

| Figure 4.9  | Schematic of the Multistep Activation Function               | 95  |

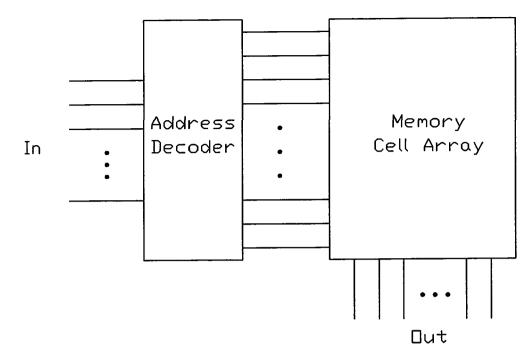

| Figure 4.10 | Structure of a Look-Up-Table                                 | 96  |

| Figure 5.1  | Sigmoid Activation Function (SAF) and Simplified             |     |

|             | Sigmoid Activation Function (SSAF)                           | 101 |

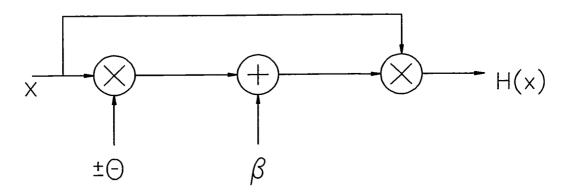

| Figure 5.2  | Block Diagram for Implementation of H(x)                     | 104 |

| Figure 5.3  | H(x) with STPT L                                             | 104 |

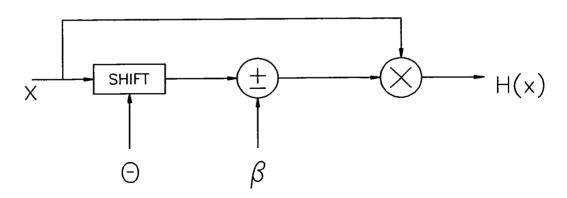

| Figure 5.4  | Implementation of the Simplified Sigmoid Activation Function | 105 |

| Figure 5.5  | Schematic of the Simplified Sigmoid Activation Function      | 106 |

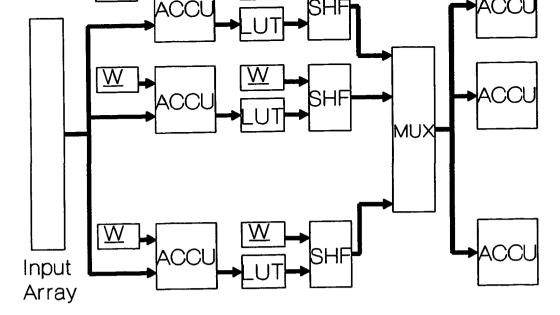

| Figure C.1  | Block Diagram of Digital Implementation Structure            |     |

|             | of an MFNN with Quantized Neurons                            | 139 |

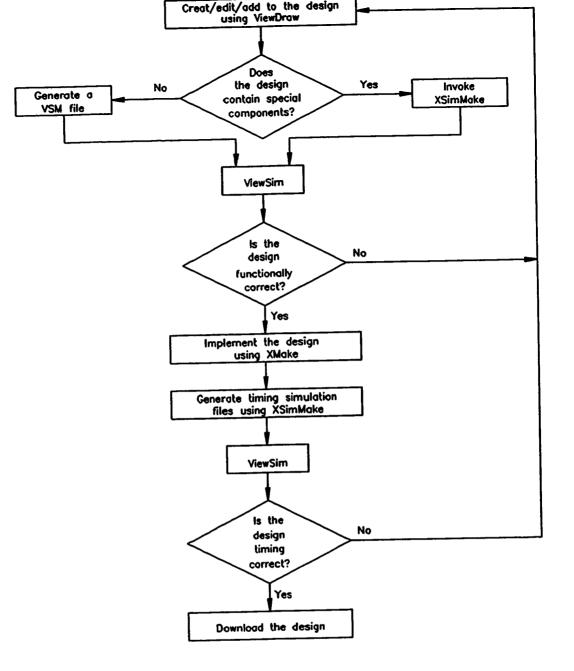

| Figure C.2  | Viewlogic Design Methodology for FPGAs                       | 142 |

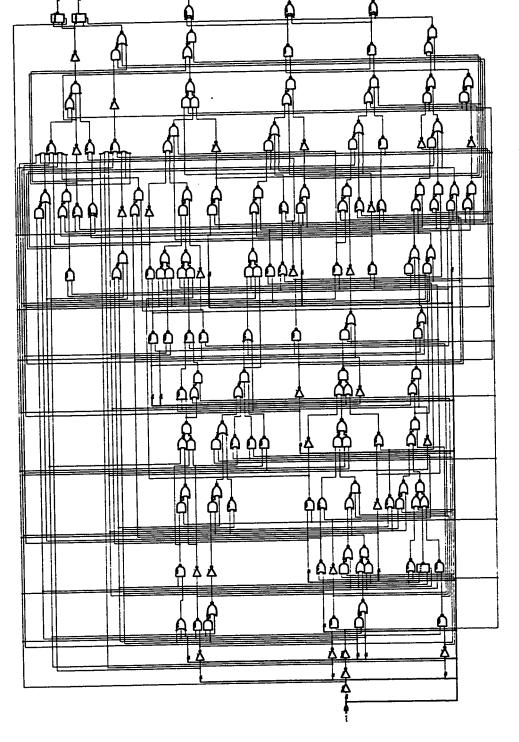

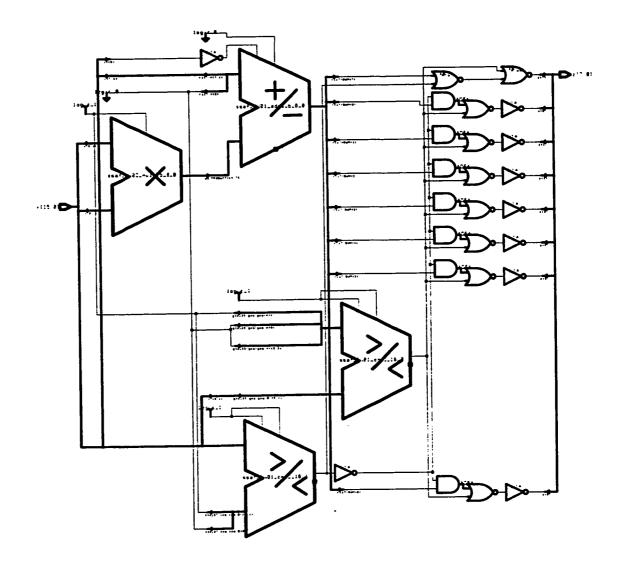

| Figure C.3  | Top Level Schematic for XOR Problem                          | 144 |

| Figure C.4  | 16-Bit Accumulator ACC16                                     | 147 |

| Figure C.5  | Activation Function Block LUT                                | 149 |

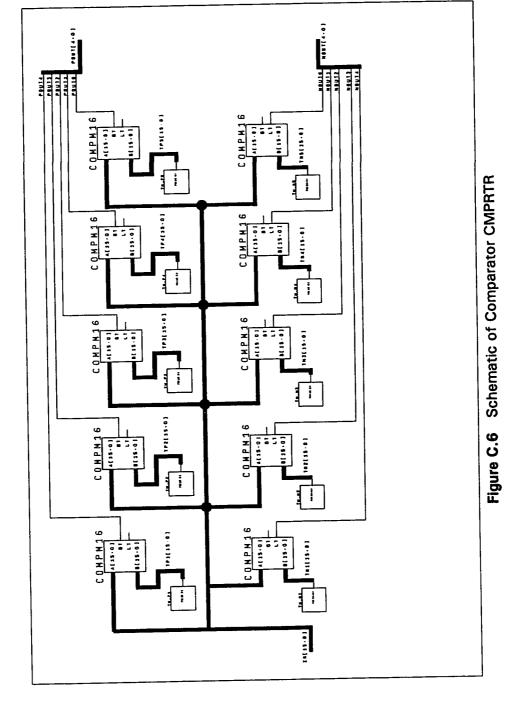

| Figure C.6  | Schematic of Comparator CMPRTR                               | 150 |

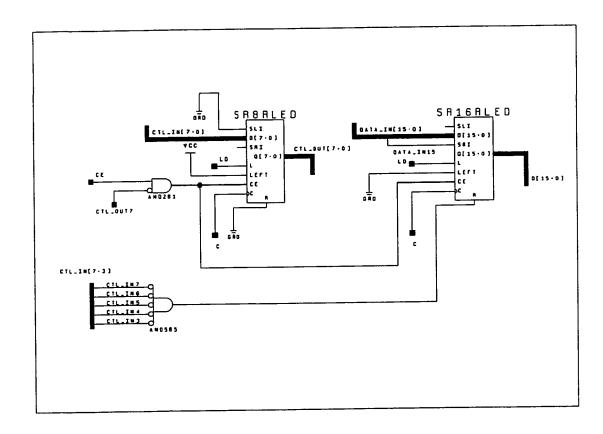

| Figure C.7  | Implementation of Shift Operation                            | 152 |

xvi

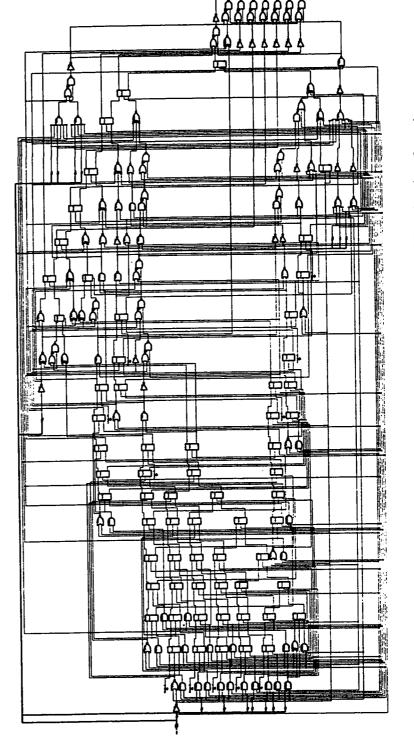

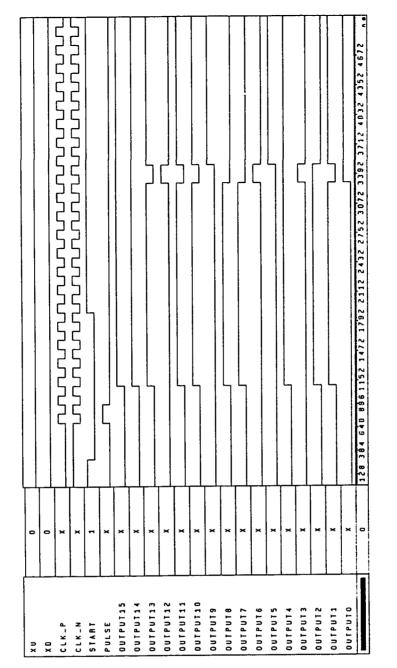

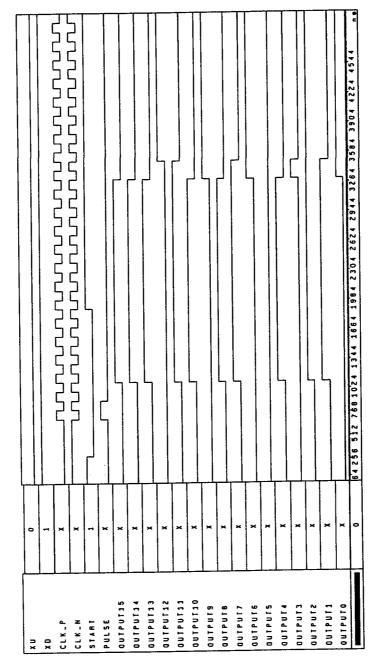

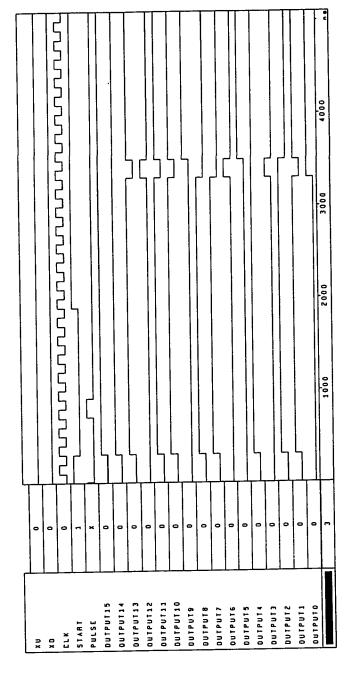

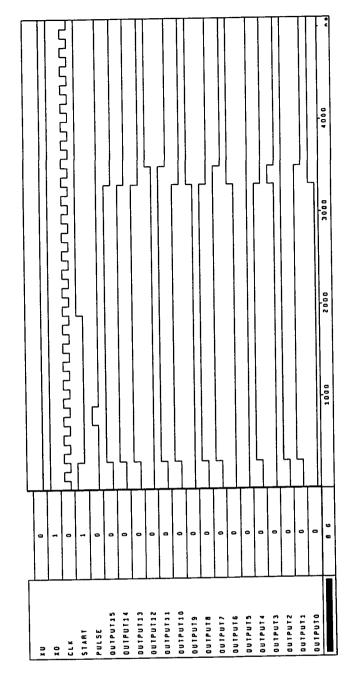

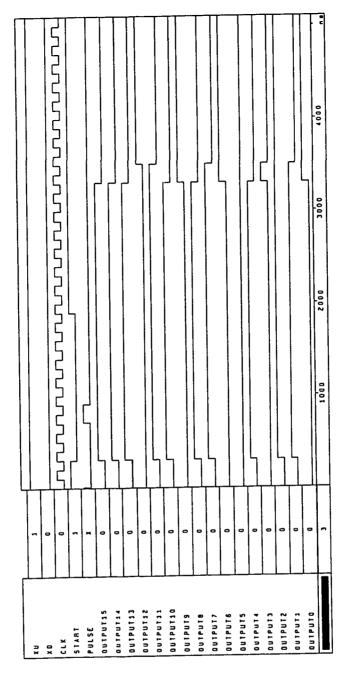

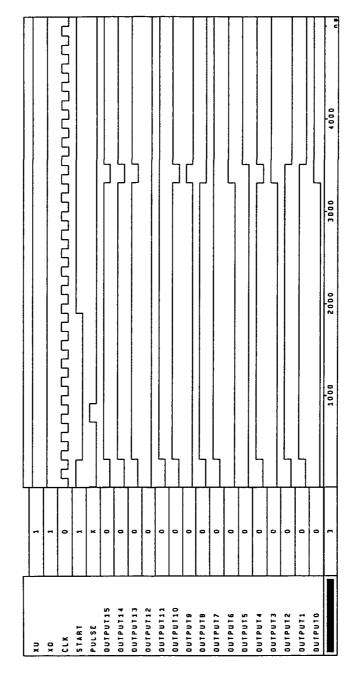

| Figure C.9  | Functional Simulation Result When $XU = 0$ and $XD = 0$ | 159 |

|-------------|---------------------------------------------------------|-----|

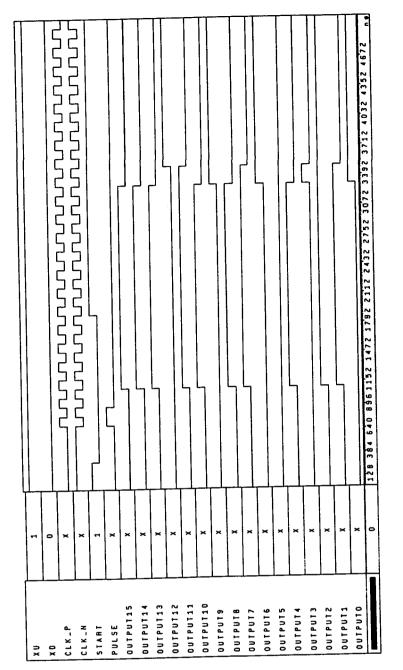

| Figure C.10 | Functional Simulation Result When $XU = 0$ and $XD = 1$ | 160 |

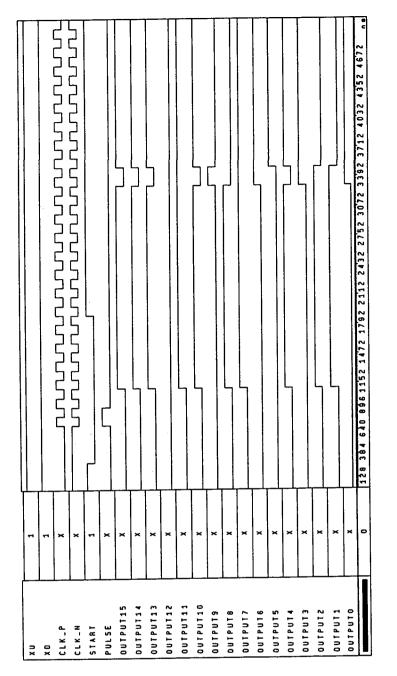

| Figure C.11 | Functional Simulation Result When $XU = 1$ and $XD = 0$ | 161 |

| Figure C.12 | Functional Simulation Result When $XU = 1$ and $XD = 1$ | 162 |

| Figure C.13 | Timing Simulation Result When $XU = 0$ and $XD = 0$     | 164 |

| Figure C.14 | Timing Simulation Result When $XU = 0$ and $XD = 1$     | 165 |

| Figure C.15 | Timing Simulation Result When $XU = 1$ and $XD = 0$     | 166 |

| Figure C.16 | Timing Simulation Result When $XU = 1$ and $XD = 1$     | 167 |

xvii

# Chapter 1

# INTRODUCTION

The last decade has witnessed the revival and a new surge in the field of artificial neural network research. The term neural network originally referred to a network of interconnected neurons which are basic building blocks of the nervous system. Today, this term, or more properly artificial neural networks, has come to mean any computing architecture that consists of a massively parallel interconnection of simple neuron-like processors. These architectures have been inspired by our current understanding of the brain, but do not necessarily conform strictly to that understanding.

The fact that an one-year-old baby is much better and faster at recognizing objects, faces, and so on than even the most advanced artificial intelligence system running on the fastest supercomputer may imply that there are numerous problems in the real world that are difficult with today's computing technology but are easily solved by human beings or even animals. In view of this fact, the research on artificial neural networks has been

thoroughly interdisciplinary area, covering neurosciences, physics, mathematics, economics, computer sciences, and electronics. There are thousands of new comers entering this exciting research field every year.

### 1.1 History of Artificial Neural Networks

The initial effort in Artificial Neural Network (ANN) research may be traced back to early 1940s when McCulloch and Pitts [McCulloch and Pitts, 1943] modeled a neuron as a simple threshold binary device to perform logic functions. In this model, each neuron can be in only one of two possible states and has a fixed threshold. It can receive inputs from excitatory synapses, all of which have identical weights. It can also receive inputs from inhibitory synapses, whose action is absolute; that is, if the inhibitory synapse is active, the neuron cannot turn on.

Later in 1949, Hebb [Hebb, 1949] published his book *The Organization* of *Behaviour* and for the first time proposed a neural learning rule for synaptic modification that has been known as the Hebb rule. Hebb stated that if one neuron repeatedly fires another, some change will take place in the connecting synapse to increase the efficiency of such firing. This correlational synapse modification rule has become the basis for many neural network models

1987 and 1988] and Hopfield Network [Hopfield, 1982].

The most significant work at the early stage of neural network research was the Perceptron model which was developed by Rosenblatt [Rosenblatt, 1959 and 1962] in late 1950s and early 1960s. It was the first precisely specified, computationally oriented neural network. The basic classification element in the Perceptron is the R-unit, which forms a weighted sum of the active elements times the connection strengths. The unit has a threshold. If the sum is greater than the threshold, the R-unit takes the value 1; if less than the threshold, the unit takes the value -1. This simple network generated much interest when initially developed because of its ability to learn to recognize simple patterns.

However, the Perceptron model has its own limitations. It is capable of realizing only those linearly separable functions. This weakness was seized by Minsky and Papert [Minsky and Papert, 1969] in 1969 when they proved mathematically that the Perceptron cannot be used for complex logic functions. The publication of their famous book, *Perceptron*, caused a sharp decline in research on neural networks.

The present impetus in neural network research is due in part to the

these papers, he presented a recurrent model of neural computation that is based on the interaction of neurons. He also pointed out that there are emergent computational capabilities at the network level that are nonexistent at the single neuron level. Such neural networks are now known as Hopfield networks.

During the 1970s when no one else was working on neural networks, Steven Grossberg and Teuvo Kohonen were making significant contributions. In 1980s, Grossberg and Carpenter [Carpenter and Grossberg, 1983, 1987, and 1990] developed their Adaptive Resonance Theory (ART) neural network architectures, based on the idea that the brain spontaneously organized itself into recognition codes. These are self-organizing neural implementations of pattern clustering algorithms, that is, they form clusters and are trained without supervision.

At the same time, Kohonen [Kohonen, 1982 and 1984] proposed his idea of a self-organizing map, based on the fact that the brain is organized, in many places, so that aspects of the sensory environment are represented in the form of two-dimensional maps; the placement of neurons is orderly and often reflects some physical characteristic of the external stimulus being sensed. It is a sheetlike artificial neural network, the cells of which become specifically tuned to

learning process.

In the mid 1980s, David Rumelhart and his colleagues rediscovered the backpropagation algorithm [Rumelhart et al., 1986], which was originally discovered by Paul Werbos [Werbos, 1974] when he applied the LMS algorithm to multiple layers of Perceptrons in the study of social sciences. The publication of their landmark book on parallel distributed processing [Rumelhart and McClelland, 1986] established the backpropagation algorithm and multilayer feedforward neural networks (MFNNs) as the major paradigm of the field of neural network research. This work and earlier works have finally galvanized a large number of scientists into thinking in terms of collective neural computation rather than single neurons.

From the late 1980s through the 1990s, with some neural network paradigms having reached a considerable degree of maturity, more and more efforts have been directed towards the area of neural network implementation as well as applications. The pioneering work by Mead [1989] marked the beginning of a new era in hardware implementation of neural networks. Since then, with the technological advances of VLSI circuits and systems, the field of VLSI artificial neural networks experienced an exponential growth and a new engineering discipline was born. Various work on analog, digital, pulse-

and Elmasry, 1992, Oh and Salam, 1993 and 1994, Kim and Shanblatt, 1992, Zaghloul et al., 1994, Sheu and Choi, 1995].

By far, Hopfield networks, ART networks, self-organizing maps, and multilayer feedforward networks are the most popular artificial neural network models that have ever been proposed. Other important ANN models may include Neocognitron[Fukushima, 1975 and 1980], Boltzman machines[Hinton and Sejnowski, 1986][Ackley et al., 1988], bidirectional associative memories (BAM's)[Kosko, 1987 and 1988], and fuzzy ARTMAP[Carpentaer et al, 1992 and 1993].

### **1.2 ANN Features**

Generally speaking, an artificial neural network model is specified by three factors:

- a set of basic processing elements, called neurons (or nodes)

- a specific topology of weighted interconnections between neurons

- a training or learning rule which specifies an initial set of weights and indicates how weights should be adapted during use to improve performance

sums a number of weighted inputs and passes the result through a nonlinear activation function. More complex neurons may include temporal integration or other types of time dependencies and more complex mathematical operations than summation. The topologies of ANNs fit broadly into two classes: recursive and feedforward. A recursive ANN is a network with feedback. In such a network, each neuron receives as input a weighted output from every other neuron in the network, possibly including itself. A typical example of recursive neural networks is the Hopfield network shown in Figure 1.1. A feedforward network does not contain any closed synaptic loops or feedback. The most famous feedforward network is the Multilaver Feedforward Neural Network which will be discussed thoroughly in Chapter 2. Training algorithms for ANNs can be described either as supervised training or unsupervised training. The distinction between supervised and unsupervised algorithms depends on information they use. Supervised training, also called learning with a teacher, assumes that the desired output of the network is known. This is then used to form an error signal which is used to update the weights. On the other hand, in unsupervised training the desired output is not known, but instead training is based simply on input/output values. Such training algorithms usually act to extract features from sets of input data.

Figure 1.1 A Hopfield Network

The potential benefits of neural networks extend beyond the high computation rates provided by massive parallelism. Some of these benefits are outlined below.

- Neural networks typically provide a greater degree of robustness or fault tolerance than von Neumann sequential computers because there are many more processing elements, each with primarily local connections.

- Neural networks have the ability to adapt to changes in the data and

- 8

areas such as speech and image recognition. Adaptation also provides a degree of robustness by compensating for minor variabilities in characteristics of processing elements.

- Neural networks can perform functional approximation and signal filtering operations which are beyond optimal linear techniques because of their nonlinear nature.

- Neural network classifiers are non-parametric and make weaker assumptions concerning the shapes of underlying distributions than traditional statistical classifiers.

- Neural networks are model-free classifiers because they approximate functions with raw sample data.

Because the motivation of ANN research comes mainly from the fact that humans are much better at pattern recognition than digital computers, there is no surprise that ANNs have found many applications in vision processing and speech processing[Sejnowski et al., 1987][Lang et al., 1990][Taylor, 1990][Levin, 1993][Kung and Taur, 1995][Zhang and Fulcher, 1996]. Besides, ANNs have also been applied to the areas of optimization[Tank and Hopfield,

and Winarske, 1988][Choi et al, 1993][Kechriotis, et al., 1994][Ansari, et al., 1995], control systems[Nguyen and Widrow, 1990][Narendra and Parthasarathy, 1990][Sebald and Schlenzig, 1994][Sanger, 1994][Lewis, et al., 1996], and medical applications[Nikoonahad and Liu, 1990][Nekovei and Sun, 1995][Choong, et al., 1996], to mention a few.

### 1.3 Motivations and impact of this research

Although artificial neural networks have found diverse applications in control, signal processing, and pattern recognition, among others, this is still a research field with many open problems in the areas of theory, applications, and implementations. Compared with the development in neural network theories, hardware implementation has lagged behind. In order to take the full advantages of neural networks, there has to be dedicated hardware implementations. Research in hardware implementations belongs to the main areas of activity in the field of neural networks and plays a unique role in the progress of the entire field. The surge of interest in neural networks, which started in mid eighties, was to a large extent caused by advances in VLSI technology. Today, harnessing VLSI technology to produce efficient implementations of neural networks may be the key to the future growth and ultimate success of neural network techniques.

success in their own application domains. Each technique has its own pros and cons. The selection between digital and analog circuits depends on many factors, for example, speed, precision, adaptiveness, programmability, and transfer/storage of signals. This dissertation deals with the topic in digital VLSI implementations of artificial neural networks. An all-digital artificial neural network VLSI implementation offers several advantages over its analog counterpart[White and Elmasry, 1992][Kung, 1993].

- Digital design has an overall advantage in terms of system-level performance. Dynamic range and precision are critical for many complex neural network models. Digital implementation offers much greater flexibility of precision than its analog counterpart.

- In most real-world applications, neural networks are embedded in existing digital systems. An all-digital ANN implementation provides compatibility.

- 3) Real-world applications usually require large scale neural networks, in some cases, of tens of thousands neurons and synapses. Digital VLSI is more appropriate at this level of complexity, whereas analog VLSI suffers from noise and difficulties in fabricating high-precision resistors and

- 4) Larger ANN's may require multichip implementations, and an analog implementation makes it more difficult to transfer signals from chip to chip, and also to match board-level capacitive loads and time constants. An all digital technique makes it easier to transfer signals form chip to chip.

- 5) At any given time, digital VLSI technology is always more mature than its analog counterpart in terms of fabrication technology and simulation and design automation tools. It also offers a wide range of fabrication technologies, including such technologies as ASIC for application oriented design and FPGA for rapid prototyping.

- 6) Real-world neural network applications may suffer from I/O bottlenecks, which are best addressed by digital techniques such as input buffers, shift registers, and pipelining. Moreover, power dissipation reduction techniques, such as dynamic logic and complementary operation, can be used.

- 7) Digital implementation offers a homogeneous implementation environment between the processing elements and the on-chip or

Because the state-of-the-art VLSI implementation technologies are basically a digital implementation medium, artificial neural networks must be adapted to an all-digital model in order to benefit from these technologies.

Meanwhile, there are also certain shortcomings of digital VLSI implementation that must be resolved in order to implement ANN's efficiently. Most ANN neuron calculations involve a weighted sum of the neuron inputs, and the multiplier required for this multiply-accumulate operation is slow and consumes large silicon area in a digital VLSI implementation.

The solution of this problem may be approached from 1) advances in VLSI technologies; and 2) adapting existed models to today's available technologies. This dissertation deals with the latter issue and will develop new models of MFNN's which are suitable for digital hardware implementations.

In silicon design, the cost of a chip is primarily determined by its twodimensional area. Smaller chips are cheaper chips. Within a chip, the cost of an operation is roughly determined by the silicon area needed to implement it. As pointed out previously, in digital neural network systems, multiplications are area-consuming and slow operations and there are massive such operations

inputs to neurons and their corresponding weights can be reduced, a reduced silicon area and higher speed will be resulted. Consequently, a lower cost will be achieved. The basic ideas behind the models proposed in this thesis are powers-of-two coefficients and functions, which will result in the replacement of multiplications by shift operations, which are much faster and have much smaller area, as well as the simplification of the realization of nonlinear activation functions. By using these proposed models, certain computational burdens in digital implementations will be alleviated without jeopardizing the performance of the ANN system, and a digital implementation scheme becomes very attractive.

### **1.4 Literature Survey**

The idea of powers-of-two factors was first proposed for digital filter implementations and has been successfully applied to many designs[Kwan and Chan, 1989 and 1990][Lim and Parker, 1983a and 1983b][Lim et al. 1982][Lim and Constantinides, 1979][Xue and Liu, 1986][Zhao and Tadokoro, 1988], in which multiplications were either replaced by shift only operations or reduced to shift operations plus very few additions, depending on how many terms of powers-of-two were used. Single term powers-of-two factors are most desired because they require the least operations in hardware implementation.

artificial neural networks require very high density of computations including large number of multiplications. In such cases, powers-of-two factors or at least quantized weights are needed to reduce the amount of computation and hardware requirements.

A digi-neocognitron model for VLSI implementation was proposed by White and Elmasry[White and Elmasry, 1992]. The original neocognitron (NC) model[Fukushima 1980] was adapted to an efficient all-digital implementation for VLSI. The new model, the digi-neocognitron (DNC), has the same pattern recognition performance as the NC. The DNC model was derived from the NC model by a combination of preprocessing approximations and the definition of new model function, e.g., multiplication and division are eliminated by conversion of factors to powers of 2, requiring only shift operations. The DNC model has substantial advantages over the NC model for VLSI implementation with a two to three orders of magnitude improvement in the area-delay product.

A one-dimensional Kohonen network with quantized weights and inputs was studied by Thiran and Hasler [Thiran and Hasler, 1994]. The implementation of a Kohonen network on a digital circuit realization yields the quantization of all the input signals and weight values. It is crucial to see whether this modification perturbs the self-organizing feature. In [Thiran and

organization property of the original Kohonen network for the one-dimensional case is conserved when the weights are quantized provided that its parameters are well chosen.

The application of discrete weights and the powers-of-two technique in multilayer feedforward neural networks has been studied by several authors [Marchesi et al. 1990][Nakayama et al. 1990][Piazza et al. 1993] and most recently by Marchesi et al. [Marchesi et al. 1993]. In [Marchesi et al. 1993], a fast neural network model was proposed for digital VLSI implementation along with a dedicated learning procedure. In their model, weight values were restricted to powers-of-two or sum of powers-of-two and adaptive biases and automatic learning rate control were employed to compensate the quantization error.

It was pointed out that one of the major problems of digital architectures implementing neural networks, affecting both performance and chip area, is the presence of multipliers. The multiplications between inputs and weights, which are slow compared to other operations and require a lot of chip area if a direct VLSI implementation is planned, can be the bottle-neck of the system. By introducing the idea of powers-of-two weights, it is possible to substitute multiplications with simple shifts or much fewer shift-and-add operations,

However, the learning algorithm developed in [Marchesi et al. 1993] was not very effective. Its convergence performance was not satisfactory due to lack of sufficient adjustable parameters. For a given problem, the starting point of their proposed learning algorithm is the solution of the same mapping problem with a conventional MFNN having continuous weights, applying the BP learning algorithm. The obtained weights are then quantized to powers-of-two values and the BP will be applied again to adjust the discretized weights in hope to converge to the final solution. It is obvious that there is little room to improve the network by adjusting the quantized weights. These quantized weights are distributed in some discrete points and the gaps among these points are usually much larger than the weight updating amount required by the BP algorithm, so they are not suitable for fine tuning the neural network, especially when single term powers-of-two format is used. Moreover, the quantization scheme they adopted appears to be fairly complicated. Actually, the minimization of the sum of squared weight quantization error as adopted in [Marchesi et al. 1993] does not necessarily reduce the sum of squared output error of the network due to the non-linear nature of the neural network systems. It will be much simpler to adopt direct quantization of weights to their nearest powers-of-two values as proposed in this dissertation.

digital VLSI implementation, no investigation on real hardware issues had been presented in the published work and that was a major weakness of their paper.

In view of this situation, a new algorithm for design of MFNNs with single term powers-of-two (STPT) weights will be presented in Chapter 3 of this dissertation, which has more degrees of freedom to adapt to a given problem. In Chapter 4, an all new model of MFNNs with quantized neurons will be proposed for digital hardware implementation, in which multiplications can still be avoided and the implementation of nonlinear activation functions will also be simplified.

# 1.5 Organization of this Dissertation

The remaining of this dissertation is organized as follows.

Chapter 2 begins with the multilayer feedforward neural network model. The structure of the network and the backpropagation (BP) learning algorithm are discussed. Some modifications to the BP algorithm are also presented. At the end of this chapter, the issue of hardware implementation of MFNNs is addressed, which introduces the necessity of the models to be developed in Chapters 3 and 4.

with single term powers-of-two (STPT) weights. The design procedures are provided along with simulation results.

Another MFNN model - MFNNs with quantized neurons will be proposed in Chapter 4. The concept of quantized neuron is introduced and followed by the corresponding training algorithm. The design methodology of such networks is developed and the mapping capability of the new model is examined.

Chapter 5 presents more MFNN models suitable for digital implementations, starting with a simplified sigmoid activation function which is easy for direct hardware realization, and followed by some MFNN models designed to accommodate continuous and discrete input patterns.

Chapter 6 concludes the dissertation and suggests possible future research directions.

# Chapter 2

# MULTILAYER FEEDFORWARD NEURAL NETWORKS

As mentioned in Chapter 1, multilayer feedforward neural networks (MFNNs) are one of the most important and widely used ANN models. In this Chapter, a review of the structure, properties, and training algorithms of MFNNs will be presented as a preparation for the new models proposed in the following chapters.

## 2.1 MFNN Architecture

A Multilayer Feedforward Neural Network is a unidirectional network in which adjacent layers are fully connected. The general structure of such a network can be illustrated by Fig.2.1. For an L-layer MFNN, there is an input layer (denoted as layer 0) with  $N_0$  input nodes, an output layer (denoted as layer L) with  $N_L$  output neurons, and one or more hidden layers with  $N_h$  (h = 1, 2, ..., L-1) neurons at layer h.

Figure 2.1 A Multilayer Feedforward Neural Network

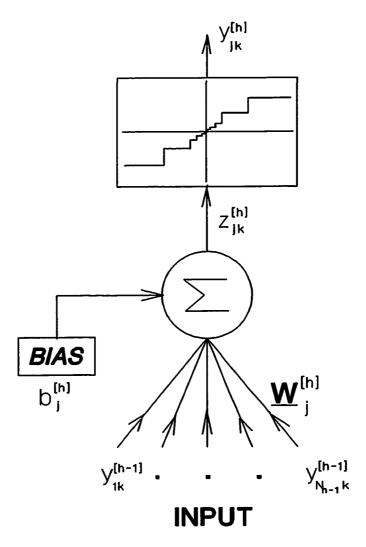

summations, and calculation of nonlinear functions. A typical neuron of MFNNs is illustrated in Fig.2.2, where  $x_i$ 's are inputs to the neuron,  $w_i$ 's are corresponding connection weights, z is the net input to the neuron before activation, and y is the output of the neuron. The input-output relationship of the neuron can be described as

$$z = \sum_{i=1}^{N} w_i x_i + b$$

(2.1)

and

$$y = F(z) \tag{2.2}$$

where  $F(\cdot)$  is a nonlinear activation function. Some commonly used forms of  $F(\cdot)$  include the hardlimit function, threshold logic function, and sigmoid function, which are shown in Fig.2.3.

Usually, the collective features of neural networks are of more interest than those of single neuron. When the entire network is concerned, the inputoutput relationship of a multilayer feedforward neural network can be described by the following set of equations

# OUTPUT

Figure 2.2 A Typical Neuron in MFNNs

Figure 2.3 Commonly Used Nonlinear Activation Functions

$$y_{jk}^{[h]} = F\left(\sum_{i=1}^{N_{h-1}} w_{ij}^{[h]} y_{ik}^{[h-1]} + b_{j}^{[h]}\right)$$

(2.3)

with

$$y_i^{[0]} = x_{ik}$$

for  $i = 1, 2, ..., N_0$  (2.4)

where  $y_{ik}^{[h-1]}$  is the output of neuron *i* at layer *h*-1;  $w_{ij}^{[h]}$  is the connection weight between neuron *i* at layer *h*-1 and neuron *j* at layer *h*;  $b_j^{[h]}$  is the bias of neuron *j* at layer *h*;  $x_{ik}$  is element *i* of the input pattern when pattern *k* is presented to

of the network.

Due to the use of nonlinearities within neurons, multilayer feedforward neural networks overcome many of the limitations of single layer perceptrons[Rosenblatt, 1958 and 1962], which can only be applied to linearly separable problems. Now, it is possible to use MFNNs to distinguish between arbitrarily complex decision regions. Actually, it has been shown that MFNNs with a single hidden layer and arbitrarily bounded and nonconstant activation functions are universal approximators provided that sufficiently many hidden neurons are available [Hornik et al., 1989]. Although one hidden layer is usually sufficient, sometimes a problem is easier to solve with more than one hidden layer. In this case, easier means that the network learns faster.

For a given problem, the parameters of a MFNN, such as the number of layers, the number of hidden neurons, the formula of activation functions, and the values of weights, need to be determined before the neural network can be applied to solve the problem. Among them, how to obtain the appropriate values of weights is the major concern, i.e., how to train the network to adapt to each particular problem. Learning algorithms for MFNNs has been a research topic since 1960s. So far, the backpropagation (BP) algorithm[Rumelhart et al. 1986] has been the most popular one in spite of the existence of some

1992], simulated annealing [Kirkpatrick et al., 1988][Szu, 1986], Choice of Internal Representations (CHIR) [Grossman et al., 1989], and layer by layer optimization [Ergezinger and Thomsen, 1995][Wang and Chen, 1996]. In the next section, the BP algorithm will be reviewed and some of possible modifications will be discussed.

# 2.2 The Backpropagation Algorithm

Consider the multilayer feedforward neural network as shown in Fig.2.1. Adopting the same definition as in Section 2.1, the input-output relationship of the network can be described as follows:

$$y_{jk}^{[h]} = F\left(\sum_{i=1}^{N_{h-1}} w_{ij}^{[h]} y_{ik}^{[h-1]} + b_{j}^{[h]}\right)$$

(2.5)

with

$$y_i^{[0]} = x_{ik}$$

for  $i = 1, 2, ..., N_0$  (2.6)

. . .

Usually, the output of the network is not exactly the same as the desired output during the learning process, there is an error associated with each pattern. The error can be measured as the sum of the squared difference

a pattern k is presented to the network, the error at neuron j of the output layer is calculated as

$$\boldsymbol{\theta}_{jk} = (t_{jk} - y_{jk}^{[L]})^2 \tag{2.7}$$

Here  $t_{jk}$  represents element *j* of the target pattern *k* and *L* refers to the output layer of an MFNN with *L* layers. Then the sum of squared error (SSE) related to a particular pattern *k* can be defined as

$$\boldsymbol{\Theta}_{k} = \sum_{j=1}^{N_{L}} \left( \boldsymbol{t}_{jk} - \boldsymbol{y}_{jk}^{[L]} \right)^{2}$$

(2.8)

And, the total squared error (TSE) over all patterns in the training set is defined as

$$TSE = \sum_{k=1}^{K} \boldsymbol{\theta}_{k}$$

(2.9)

Where K is the number of patterns contained in the training set. A learning process, or training algorithm, is attempting to reduce the output error by adjusting the weights and, in some situations, other parameters of the network.

First proposed by Werbos [Werbos, 1974] and rediscovered by Rumelhart

method which allows updating of the weights of a feedforward neural network. The idea of the gradient descent algorithm is to make the change in a weight proportional to the negative derivative of a cost function, such as TSE, with respect to that weight. Hence, by following this rule, the change in weight  $w_{ij}^{[h]}$  (due to pattern k) can be calculated as

$$\Delta_{k} w_{ij}^{[h]} = -\varepsilon \frac{\partial \Theta_{k}}{\partial w_{ij}^{[h]}} \qquad \text{for } 1 \le h \le L \qquad (2.10)$$

where  $\epsilon$  is a learning rate parameter of weights, which controls the pace of each weight adjustment.

By applying the chain rule (see Appendix A), the following formulas can be obtained for weight updates in the BP learning algorithm

$$\Delta_k \boldsymbol{w}_{ij}^{[h]} = \varepsilon \,\delta_{jk}^{[h]} \boldsymbol{y}_{ik}^{[h-1]} \tag{2.11}$$

where

$$\delta_{jk}^{[h]} = F'(z_{jk}^{[h]}) \sum_{l=1}^{N_{h+1}} \delta_{lk}^{[h+1]} w_{jl}^{[h+1]} \qquad \text{for } h < L \qquad (2.12)$$

and

####

Here F'() is the derivative of the activation function F(). It can be seen that the update of weights starts from the output layer down to the input layer. In this process, the derivative of the activation function plays a very important role. If the derivative is zero, no learning will occur even though there is a large amount of error. A very flat activation function, i.e., an activation function with very small values of derivative, may result in a very long learning process.

In summary, the BP algorithm may be carried out as follows:

- Step 1: Initialization of weights with small random numbers

- Step 2: Presentation of input patterns and desired output patterns

- Step 3: Calculation of actual output and squared output error

- Step 4: Check TSE <  $E_0$  ? If yes, then stop; otherwise proceed to Step 5

- Step 5: Update of weights

- Step 6: Go back to Step 2

Although the BP algorithm remains as the most popular and effective way to train MFNNs, there are some drawbacks accompanying it. The convergence speed of the BP algorithm is usually slow, and, in some situations,

In view of these problems, modifications to the original BP algorithm have been proposed by some researchers [Vogl et al., 1988][Jacobs, 1988][Minai and Williams, 1990][Schreibman and Norris, 1990][Kruschke and Movellan, 1991][Lee et al., 1991].

# 2.3 Improvements to the BP Algorithm

Since backpropagation suffers from low convergence speed, modifications to the original algorithm have been proposed to improve the learning speed. Some of these modifications are discussed in this section.

#### 2.3.1 Adjustable Learning Rate

Choosing an appropriate learning rate parameter  $\epsilon$  is a key factor in controling the learning speed of the backpropagation. At different stages of a learning process, the best value of  $\epsilon$  may be different. Instead of using a constant learning rate for the entire learning process, a good idea is to adjust it automatically as learning progresses [Jacobs, 1988][Vogl et al., 1988]. The usual approach is to check whether a particular weights update did actually decrease the output error. If it didn't, then the process overshot, and  $\epsilon$  should be reduced. On the other hand, if several steps in a row have decreased the error, then perhaps the learning process is being too conservative, and  $\epsilon$  could

$\Delta \varepsilon = \begin{cases} +a & \text{if } \Delta E < 0 \text{ consistently} \\ -b\varepsilon & \text{if } \Delta E > 0 \\ 0 & \text{otherwise} \end{cases}$ (2.14)

Where  $\Delta E$  is the difference between the network output errors at two consecutive times t+1 and t, and a and b are positive constants.

#### 2.3.2 Momentum Term

As stated above, it is difficult to choose an appropriate learning rate parameter  $\epsilon$  for a particular problem. The learning can be very slow if the learning rate  $\epsilon$  is too small, and can oscillate widely if  $\epsilon$  is too large. A momentum term can be introduced to deal with this problem [Phansalkar, 1994]. This scheme is implemented by giving a contribution from the previous weight update to each of the current weight change:

$$\Delta w(t+1) = -\varepsilon \frac{\partial E}{\partial w} + \mu \Delta w(t) \qquad (2.15)$$

where  $\Delta w(t+1) = w(t+1) \cdot w(t)$ ,  $\Delta w(t) = w(t) \cdot w(t-1)$ , and  $\mu$  is the momentum parameter which is a positive number between 0 and 1.

If the learning process is marching through a plateau region of the error surface, then  $(\partial E/\partial w)$  will be about the same at each time-step and the above

$$\Delta w = -\frac{\varepsilon}{1-\mu} \frac{\partial E}{\partial w}$$

(2.16)

with an effective learning rate of  $\epsilon/1-\mu$ . On the other hand, in an oscillatory situation,  $\Delta w$  responds only with coefficient  $\epsilon$  to instantaneous fluctuations of  $(\partial E/\partial w)$ . The overall effect is to accelerate the long term trend by a factor of  $1/(1-\mu)$ , without magnifying the oscillations.

#### 2.3.3 Adjustable Biases and Activation Functions

Since biases can be considered as the weights which are connected to constant input 1, it is also possible to adjust biases using the gradient descent method as in weight adaptations. To be specific, the following formula can be employed.

$$\Delta_{k} b_{j}^{[h]} = -\varepsilon_{b} \frac{\partial \boldsymbol{e}_{k}}{\partial b_{j}^{[h]}}$$

(2.17)

Where  $\epsilon_{b}$  is the step size for bias adjustment and  $b_{j}^{(h)}$  is the bias of neuron j at layer h. Similar to weight updates, the following equations may be obtained by using the chain rule

where

$$\delta_{jk}^{[h]} = F'(z_{jk}^{[h]}) \sum_{i=1}^{N_{h+1}} \delta_{ik}^{[h+1]} w_{ji}^{[h+1]}$$

(2.19)

for h < H, and

$$\delta_{jk}^{[H]} = 2(t_{jk} - y_{jk}^{[H]}) F'(z_{jk}^{[H]})$$

(2.20)

Here F'() is the derivative of the activation function F(), and  $t_{jk}$ ,  $y_{jk}^{[h]}$ , and  $z_{jk}^{[h]}$  have the same definition as in Section 2.2.

It is well known that the nonlinear activation functions play a very important role in the performance of MFNNs. Also, it can be seen from (2.11)-(2.13) that the derivative of the activation function F'(x) is a key factor in the weight adaptation process. This indicates that the learning process can be improved by controlling the shape of the activation functions. For the most widely used sigmoid activation function

$$F(x) = \frac{1 - e^{-\alpha x}}{1 + e^{-\alpha x}}$$

(2.21)

the shape of the function can be controlled by the slope, which, in turn, can be

the idea of the gradient descent method, i.e.,

$$\Delta_{k} \alpha_{j}^{[h]} = -\varepsilon_{\alpha} \frac{\partial \Theta_{k}}{\partial \alpha_{j}^{[h]}}$$

(2.22)

Some results [Kruschke and Movellan, 1991][Tang and Kwan, 1993] have shown that this method can speed up the learning process significantly. The detailed derivation of adaptation equations and discussion will be presented in Chapter 3.

## 2.4 Hardware Implementations of MFNNs

As pointed out in Chapter 1, digital implementation of neural networks is very attractive, especially with the currently available ASIC and FPGA technologies. However, when applied to MFNNs, a direct implementation scheme may not be appropriate due to the large number of multiplications involved.

If we look at a typical neuron in an MFNN, a direct implementation will generate a cell as shown in Fig.2.4. Among the functional blocks involved, multipliers are not favoured by digital VLSI technologies since they consume large chip areas and have slow speed. Implementing nonlinear activation

Figure 2.4 Block diagram of direct implementation of a neuron in MFNNs

functions using look-up-table method will also require large silicon area. Large silicon area means high cost. Reducing the cost always has high priority in any real applications.

In chapter 3, an MFNN model using single term powers-of-two weights will be proposed and consequently multipliers will be replaced by shifters. And, in Chapter 4, an MFNN model with quantized neurons will be developed which can eliminate multipliers as well as simplify the digital implementation of nonlinear activation functions. The proposed models will result in a significant improvement in both area and speed of digital implementation of multilayer feedforward neural networks.

# **Chapter 3**

# MULTILAYER FEEDFORWARD NEURAL NETWORKS WITH SINGLE TERM POWERS-OF-TWO WEIGHTS

As discussed in previous chapters, in order to alleviate the burden of multiplications in digital hardware implementation of MFNNs, powers-of-two valued connection weights can be used in place of the original continuously valued weights such that the multiplications can be replaced by shift operations. It is no doubt that the format of single term powers-of-two (STPT) would be of the most interest. To be specific, when the STPT format is used, all weights in an MFNN would only be able to take values from the following set  $W_{stot}$

$$W_{ettyt} = \{ \pm 1, \pm 2^{-1}, \dots, \pm 2^{-M}, 0 \}$$

(3.1)

Where M is the maximum number of bits that may be shifted. It is noted that the above definition constrains the absolute value of weights to be less than or

It is also possible to extend admissible weight values to be sum of two or more terms of powers-of-two, which has been proposed for both digital filters and neural networks [Marchesi et al., 1993]. Although such expansion would make the learning process easier due to the increased number of available weight values, it will substantially weaken the advantages of the powers-of-two technique because of the increased complexity of weight management and the higher number of operations. Thus, in the following, the discussion will concentrate on single term powers-of-two (STPT) format.

Since they are not involved in multiplications, biases of neurons are not necessarily limited to powers-of-two format, they can still be real numbers. As pointed out in Chapter 1, after adding single term powers-of-two constraint to weights, their ability to adapt to various problems is dramatically reduced due to limited choices. Therefore, it may not be adequate to adjust only weights in an MFNN with powers-of-two weights as in [Marchesi et al., 1993], new adjustable parameters must be introduced to provide more degrees of freedom in learning. One of the key factors which have significant impact on the performance of an MFNN is, as mentioned previously, the nonlinear activation function. In this Chapter, the adaptive slope of activation functions will be introduced to enhance the learning capability of the post-quantization MFNNs.

MFNNs with STPT weights consists of three stages. First, the conventional backpropagation algorithm is applied to find the continuous solution (a set of continuous weights) for a given problem; then, quantization is adopted to convert the obtained weights into appropriate STPT values. Finally, adaptation of the slope of the activation function will, in addition to adjustment of weights and biases, be employed to fine-tune the post-quantization network to the predetermined error level based on the method presented below.

# 3.1 Adaptation of activation functions in MFNNs

Consider a multilayer feedforward neural network with the following form of sigmoid activation function

$$F(x) = \frac{1 - e^{-\alpha x}}{1 + e^{-\alpha x}}$$

(3.2)

This nonlinear activation function is a key factor in determining the performance of a neural network. It can also be seen from Eq.(2.11)-(2.13) that the activation function and its derivative play a very important role in the process of weight updates and, as a result, any change in the activation function will affect the learning process. Therefore, a proper choice of the shape of activation function can result in a better adjustment of weights and also affect the input-output relationship of the network. Shown in Fig. 3.1 are sigmoid

activation function may be controlled by the slope of the function and the slope of the activation function is controlled by the parameter a. This property was used in [Kruschke and Movellan, 1991] to speed up the BP learning process and improve generalization capability.

The idea of gradient descent method can be extended to adaptation of parameter a, i.e., the change in a will be in the opposite direction of the partial derivative of the squared output error of the network with respect to a. Hence, the change in  $a_j^{[h]}$ , the parameter a of neuron j at layer h, due to the presentation of pattern k can be expressed as

$$\Delta_{k} \alpha \int^{[h]} = -\epsilon_{\alpha} \frac{\partial \Theta_{k}}{\partial \alpha \int^{[h]}}$$

(3.3)

where  $\epsilon_a$  is a step size for *a* update and  $e_k$  has the same definition as in section 2.2. By applying the chain rule (see Appendix B), the following relationship are obtained

$$\Delta_{k} \alpha_{j}^{[h]} = \epsilon_{\alpha} F_{\alpha}(z_{jk}^{[h]}, \alpha_{j}^{[h]}) \sum_{i=1}^{N_{h+1}} \delta_{ik}^{[h+1]} W_{jj}^{[h+1]} \qquad \text{for } h < L$$

(3.4)

and

Figure 3.1 Sigmoid Functions with Different  $\alpha$

$$\Delta_{k} \alpha_{j}^{[L]} = 2\epsilon_{\alpha} (t_{ik} - y_{ik}^{[L]}) F_{\alpha} (z_{ik}^{[L]}, \alpha_{j}^{[L]})$$

(3.5)

where  $F'_{a}(z,a)$  is the partial derivative of the activation function F() with respect to a, i.e.,

$$= \frac{\partial \alpha}{\partial \alpha}$$

and  $\delta_{ik}^{(h+1)}$ , L, N<sub>h+1</sub>,  $z_{jk}^{(h)}$ ,  $t_{jk}$ , and  $y_{jk}^{(L)}$  are all defined in the same way as in Chapter 2.

It is also possible and usually helpful to include a momentum term to the update equation of  $\alpha$ . When taking all training patterns into account, the  $\alpha_j^{(h)}$  will be updated as

$$\alpha_{j}^{[h]}(t+1) = \alpha_{j}^{[h]}(t) + \sum_{k=1}^{K} \Delta_{k} \alpha_{j}^{[h]} + \mu_{\alpha} \{\alpha_{j}^{[h]}(t) - \alpha_{j}^{[h]}(t-1)\}$$

(3.7)

This scheme has been proved to be very effective in improving the learning speed of MFNNs. In this Chapter, the adaptive slope of the activation function will be used in the design procedure of MFNNs with STPT weights for the purpose of post-quantization network fine-tuning, i.e., adjust the network to compensate the error resulted from weight quantization.

## 3.2 Design Procedures for MFNNs with STPT Weights

#### 3.2.1 Basic Ideas

Consider a multilayer feedforward neural network as illustrated in Fig.2.1 where the nonlinear activation function applied at the output of each neuron is

network with STPT weights from the set  $\{\pm 1, \pm 2^{-1}, \pm 2^{-2}, \dots, \pm 2^{-M}, 0\}$ , where M determines the number of quantization levels of weights. For a given M, there are 2M+3 distinguished values of weight to choose from.

Given a mapping problem between the input and output spaces of the MFNN and a set of training pattern pairs  $\{X_k, T_k\}$ , the starting point of the design procedure is the solution for the same mapping problem from a conventional MFNN with continuous weights, using BP as the learning algorithm. Then, at the next stage, continuous weights will be transformed into single term powers-of-two weights and activation functions are scaled accordingly to accommodate such quantization. Finally, the slopes of activation functions will be adjusted based on the algorithm described in the previous section to compensate any increase in the output error of the network caused by quantization. Since the bias of each neuron,  $b_i^{(h)}$ , is not involved in multiplications, it can remain continuous.

Before the quantization of weights, it is necessary to introduce a normalization process such that all weights will be in the interval of [-1, +1] because the set of quantization levels is defined by (3.1). Consider a particular neuron *j* at layer *h*, where all connections going into the neuron are denoted by weights  $w_{ii}^{[h]}$ ,  $i = 1, ..., N_{h-1}$ . Define

$$m_{j-\max} = m_{ij} (m_{jj} + j + m_{ij} - j, \dots, m_{j-1})$$

(0.0)

Then, the normalization will be carried out by dividing weights  $w_{ij}^{[h]}$  by  $w_{j-max}^{[h]}$  as follows

$$w'_{ij}^{[h]} = \frac{w_{ij}^{[h]}}{w_{j-\max}^{[h]}}$$

(3.9)

$w'_{ij}^{(h)}$  now belongs to the interval [-1, +1]. However, it can be seen that the input-output mapping relationship of the network will be changed if normalized weights are used in the network without any other appropriate adjustment of the network. By examining (2.3), (2.4) and (3.2), it is found that it is possible to compensate the normalization of weights by scaling up the parameter of *a* accordingly. That means if the weights are normalized by their maximum value  $w_{j-max}$ , then adjusting the parameter *a* of the sigmoid activation function as follows will keep the network mapping relationship unchanged.

$$\alpha_{j}^{[h]} = \alpha_{j}^{[h]} W_{j-\max}^{[h]}$$

(3.10)

Now, we can quantize the normalized weights to STPT format. The criterion used here is to round a weight to its nearest STPT value selected from the set  $W_{stpt}$ . This scheme can be described as follows

$$Q(w) = sgn(w) \left\{ 2^{-m} \quad C_m < |w| < C_{m-1} \right\}$$

where sgn(w) denotes the sign of w and

$$C_m = (\frac{3}{4}) 2^{-m}$$

for  $m = 0, 1, ..., M$  (3.12)

A quantization curve based on the above definition when M = 4 is shown in Fig.3.2.

Usually, there will be an increase in the output error of the network due to weight quantization. Therefore, more adjustment to the network is necessary in order to bring this error down to a predetermined level. In this proposed model, the method of adapting the slope of the activation functions, as described in Section 3.2, will be used for this purpose. At this point, since weights have already been quantized to discrete values and are not able to make arbitrary changes (required by BP algorithm), there will be an update in weights only when such an update can result in a reduced output error. At the same time, the bias of each neuron can still be adjusted by using BP algorithm because they are not involved in any multiplication and may remain to be continuous.

Figure 3.2 Weight Quantization Curve When M = 4

3.2.2 Design Algorithm

Based on the idea presented in Section 3.2.1, a procedure for design of

developed and is illustrated in the following.

- Step 1: Set  $a_j^{[h]} = a_0$  (j = 1, 2, ..., N<sub>h</sub>; and h = 1, 2, ..., L), where  $a_j^{[h]}$  is related to the sigmoid activation function applied to neuron j at layer h of an L-layer MFNN.

- Step 2: Starting with a set of weights and biases with small random values, train the network using the conventional backpropagation algorithm to obtain a continuous solution for the given problem, i.e., to obtain a set of continuous weights and biases which can achieve

$$\sum_{k=1}^{K} \boldsymbol{\theta}_k < \boldsymbol{E}_0 \tag{3.13}$$

where  $e_k$  is as defined in (2.8), K is the number of pattern pairs in the training set, and  $E_0$  is a predetermined error level.

Step 3: Find the maximum absolute value,  $w_{j-max}^{[h]}$ , among weights  $w_{ij}^{[h]}$ (i = 1, 2, ..., N<sub>h-1</sub>)

$$w_{j-\max}^{[h]} = \max\{|w_{ij}^{[h]}| / i=1, ..., N_{h-1}\}$$

(3.14)

for

$$j = 1, ..., N_h$$

and  $h = 1, ..., L$ .

the interval of [-1, +1]

$$w'_{ij}^{[h]} = \frac{w_{ij}^{[h]}}{w_{j-\max}^{[h]}}$$

(3.15)

for  $i = 1, ..., N_{h-1}, j = 1, ..., N_h$  and h = 1, ..., L.

Also scale biases  $\Theta_{j}^{\,(h)}$  by the same factor  $w_{j\text{-max}}^{\quad (h)}$

$$\theta_j^{[\hbar]} = \frac{\theta_j^{[\hbar]}}{w_{l-\max}^{[\hbar]}}$$

(3.16)

for  $j = 1, ..., N_h$  and h = 1, ..., L.

Step 5: Adjust parameter  $a_j^{(h)}$  accordingly as follows

$$\alpha_{j}^{[h]} = W_{j-\max}^{[h]} \alpha_{j}^{[h]}$$

(3.17)

for  $j = 1, ..., N_h$  and h = 1, ..., L.

Step 6: Quantize normalized weights  $w'_{ij}^{[h]}$  to single term powers-of-two weights  $w'_{ij}^{[h]}$

$$w_{ij}^{*[h]} = Q(w_{ij}^{/[h]})$$

(3.18)

for  $i = 1, ..., N_{h-1}, j = 1, ..., N_h$  and h = 1, ..., L. Where the function

Step 7: Substitute current STPT weights  $w_{ij}^{[h]}$  and new values of  $a_j^{[h]}$  into the network. Calculate the squared output error over all training pattern pairs as

$$TSE = \sum_{k=1}^{K} \Theta_k \tag{3.19}$$

If TSE  $< E_0$ , stop; otherwise, proceed to Step 8.

- Step 8: Calculate  $\Delta w^{i} j^{[h]}$ ,  $\Delta b_{j}^{[h]}$ , and  $\Delta a_{j}^{[h]}$ , which are changes in  $w^{i}_{ij}^{[h]}$ ,  $b_{j}^{[h]}$ , and  $a_{j}^{[h]}$  respectively, using the relationships developed in Sections 2.2, 2.3, and 3.1.

- Step 9: Update weights w<sup>i</sup><sub>ij</sub><sup>[h]</sup> with changes Δw obtained in Step 8 and then quantize them to STPT values as in Step 6. If this update results in a reduced TSE, accept the new weights; otherwise, discard the changes and keep previous weights.

- Step 10: Update parameters  $b_j^{(h)}$  and  $a_j^{(h)}$  with changes  $\Delta b_j^{(h)}$  and  $\Delta a_j^{(h)}$ obtained in Step 8.

- Step 11: Go to Step 7.