#### University of Windsor

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1995

# BiCMOS implementation of the hierarchy for pattern extraction artificial neural network.

Kai Yiu. Hung University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Hung, Kai Yiu., "BiCMOS implementation of the hierarchy for pattern extraction artificial neural network." (1995). *Electronic Theses and Dissertations*. 1294.

https://scholar.uwindsor.ca/etd/1294

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Appendient Lover and owner

Walter State of free of

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# BiCMOS Implementation of the Hierarchy for Pattern Extraction Artificial Neural Network

by

#### Hung, Kai Yiu

#### A Thesis

Submitted to the Faculty of Graduate Studies through the

Department of Electrical Engineering in Partial Fulfillment

of the Requirements for the Degree of

Master of Applied Science

at the

University of Windsor

Windsor, Ontario, Canada May, 1995

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Application Applications of

Charles Note whiteoch

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence et non exclusive irrévocable permettant à la Bibliothèque du Canada de nationale reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition thèse la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-10937-2

| Name HUNG KAL YIL |

|-------------------|

|-------------------|

Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

ELICINUMICI. MAD ELECTRICAL.

#### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| COMMINICATIONS AND TH       | C ADTC      | 0                        | 0525   | PHILOSOPHY, RELIGION AND |       | Ancient 0579                     |

|-----------------------------|-------------|--------------------------|--------|--------------------------|-------|----------------------------------|

| COMMUNICATIONS AND TH       |             | Psychology               | 0535   |                          |       | Medieval 0581                    |

| Architecture                | 0729        | Reading                  | 0527   | THEOLOGY                 |       | Modern 0582                      |

| Art History .               | 0377        | Religious                |        | Philosophy               | 0422  | Black 0328                       |

| Cinema .                    | 0900        | Sciences                 | 0714   | Religion                 |       | African 0331                     |

| Dance                       | 037B        | Secondary                | 0533   | General                  | 0318  |                                  |

| Fine Arts                   | 0357        | Social Sciences          | 0534   | Biblical Studies         | 0321  | Asia, Australia and Oceania 0332 |

| Information Science         | 0723        | Sociology of             | 0340   | Clergy                   | 0319  | Canadian 0334                    |

| Journalism                  | 0391        | Special                  | 0529   | History of               | 0320  | European 0335                    |

| Library Science             | 0399        | Teacher Training         | 0530   | Philosophy of            | 0322  | Latin American 0336              |

| Mass Communications         | 0708        | Technology               | 0710   | Theology                 | 0469  | Middle Eastern . 0333            |

| Music                       | 0413        | Tests and Measurements   | 0288   | inediagy                 | 0407  | United States 0337               |

| Speech Communication        | 0459        | Vocational               | 0747   | SOCIAL SCIENCES          |       | History of Science 0585          |

| Theoret                     | 0465        | Tocanona.                | ,      |                          | 0303  | law 0398                         |

| Inecial                     | 0403        | LANGUAGE, LITERATURE AND |        | American Studies         | 0323  | Political Science                |

| FRUCATION                   |             |                          |        | Anthropology             |       | General 0615                     |

| EDUCATION                   | 0516        | LINGUISTICS              |        | Archaeology              | 0324  | International Law and            |

| General .                   | 0515        | Language                 |        | Cultural                 | 0326  | Relations 0616                   |

| Administration              | 0514        | General .                | 0679   | Physical                 | .0327 | Public Administration 0617       |

| Adult and Continuing        | 0516        | Ancient                  | 0289   | Business Administration  |       | Recreation 0814                  |

| Agricultural                | 0517        | Linguistics              | 0290   | General                  | 0310  |                                  |

| Aii                         | 0273        | Modern                   | 0291   | Accounting               | 0272  |                                  |

| Bilingual and Multicultural | <b>7202</b> | Literature               |        | Banking                  | 0770  | Socialogy                        |

| Business                    | 9696        | General                  | 0401   | Management               | 0454  | General                          |

| Community College           | 0275        | Classical                | 000.   | Marketing                | 0338  | Criminalogy and Penalogy 0627    |

| Curriculum and Instruction  | 0727        |                          | 0295   | Canadian Studies         | 0385  | Demography 0938                  |

| Early Childhood             | 0518        |                          | 0297   | Economics                | 0000  | Ethnic and Racial Studies 0631   |

| Elementary                  | 0524        | Medieval                 | 0298   | General                  | 0501  | Individual and Family            |

| Finance                     | 0277        | Modern                   | 0316   | Agricultural             | 0503  | Studies                          |

| Guidance and Counseling     | 0519        | African                  |        |                          | 0505  | Industrial and Labor             |

| Health                      | 0880        | American                 | 0591   | Commerce Business .      | 0508  | Relations                        |

|                             | 0745        | Asian                    | 0305   | Finance                  |       | Public and Social Welfare 0630   |

| Higher                      | 0520        | Conadian (English)       | 0352   | History                  | 0509  | Social Structure and             |

| History of                  | 0278        | Canadian (French)        | 0355   | Labor                    | 0510  | Development 0700                 |

| Home Economics              | 0521        | English                  | 0593   | Theory                   | .0511 | Theory and Methods 0344          |

| Industrial                  |             | Germanic .               | 0311   | Falklore                 | 0358  | Transportation                   |

| Language and Literature     | 0279        | Latin American           | . 0312 | Geography                | 0366  | Urban and Regional Planning 0999 |

| Mathematics                 | 0280        | Middle Eastern           | 0315   | Gerantology              | 0351  |                                  |

| Music                       | 0522        | Romance                  | 0313   | History                  |       | Women's Studies                  |

| Philosophy of               | 0998        | Slavic and East European | 0314   | General .                | 0578  |                                  |

| Physical                    | 0523        | anne and east coropean   |        | <del>-</del>             |       |                                  |

#### THE SCIENCES AND ENGINEERING

| BIOLOGICAL SCIENCES<br>Agriculture                        |        | Geodesy 0370<br>Geology 0372<br>Geophysics 0373 |

|-----------------------------------------------------------|--------|-------------------------------------------------|

| General                                                   | 0473   | Geophysics 0373                                 |

|                                                           | . 0285 | Hydrology 0388                                  |

| Agronomy<br>Animal Culture and                            | . 0203 | Hydrology 0388<br>Mineralogy 0411               |

|                                                           | 0475   | Paleobotany 0345                                |

| Nutrition                                                 |        | Paleopoiany 0343                                |

| Animal Pathology                                          | 0476   | Paleoecology 0426                               |

| Food Science and                                          |        | Paleantology                                    |

| Technology                                                | 0359   | Paleozoalogy                                    |

| Forestry and Wildlife                                     | 0478   | Palynology 0427 Physical Geography 0368         |

| Plant Culture                                             | 0479   | Physical Geography                              |

| Forestry and Wildlife<br>Plant Culture<br>Plant Pathology | 0480   | Physical Oceanography 0415                      |

| Plant Physiology                                          | 0817   |                                                 |

| Range Management                                          | 0777   | HEALTH AND ENVIRONMENTAL                        |

| Plant Physiology<br>Range Management<br>Wood Technology   | 0746   | SCIENCES                                        |

| D I                                                       |        | Environmental Sciences 0768                     |

| General Anatomy Biostatistics Botony Cell                 | 0306   |                                                 |

| Angtomy                                                   | 0287   | Health Sciences                                 |

| Bookstalica                                               | กากล   | General                                         |

| Diosidiisiids                                             | 0300   | Audiology                                       |

| botony                                                    | 0307   | Chemotherapy 0992                               |

| Cell                                                      |        | Dentistry 0567                                  |

| Ecology                                                   | 0329   | Education 0350                                  |

| Ecology<br>Entomology<br>Genetics                         | 0353   | Haspital Management 0769                        |

| Genetics                                                  | 0369   | Human Development 0758                          |

| Limnology                                                 | 0793   | Immunology 0982                                 |

| Microbiology                                              | 0410   | Immunology                                      |

| Molecular                                                 | 0307   | Mental Health                                   |

| Neuroscience                                              | 0317   |                                                 |

| Oceanography                                              | 0416   | Nursing                                         |

| Physiology                                                | 0433   | Nutrition                                       |

| Oceanography Physiology Radiation                         | 0821   | Obstetrics and Gynecology 0380                  |

| Vatariana, Carana                                         | 0779   | Occupational Health and                         |

| Zealance                                                  | . 0//0 | Occupational Health and Therapy                 |

| Radiation<br>Veterinary Science<br>Zoology                |        | Ophthalmology UJ81                              |

| Biophysics<br>General                                     | 0704   | Pathology                                       |

| General                                                   | . 0786 | Pharmacology0419                                |

| Medical                                                   | 0760   | Pharmacy 0572                                   |

| ** *** ****                                               |        | Physical Therapy                                |

| EARTH SCIENCES                                            |        | Public Health 0573                              |

| Biogeochemistry                                           | 0425   | Radiology 0574                                  |

| Biogeochemistry Geochemistry                              | 0996   | Recreation 0575                                 |

| · · · · · · · · · · · · · · · · · · ·                     |        | Recredition                                     |

| Speech Pathology<br>Toxicalogy<br>Home Economics    | 0460<br>0383<br>0386 |

|-----------------------------------------------------|----------------------|

| PHYSICAL SCIENCES                                   |                      |

| Pure Sciences                                       |                      |

| Chemistry                                           | 0.00                 |

| General                                             | 0485                 |

| Agricultural                                        | 0749                 |

| Analytical                                          | .0486                |

|                                                     | . 0487               |

| Inorganic                                           | 0488                 |

| Nuclear                                             | 0738                 |

| Organic                                             | 0490                 |

| Organic<br>Pharmaceutical                           | .0491                |

| Physical                                            |                      |

| Polymer                                             |                      |

| Radiation                                           | 0754                 |

| Mathematics                                         | .0405                |

| Physics                                             |                      |

| General                                             | 0605                 |

| Acoustics                                           | .0986                |

| Astronomy and                                       |                      |

| Astrophysics<br>Atmospheric Science                 | 0606                 |

| Atmospheric Science                                 | 0608                 |

| Atomic                                              | ., 0748              |

| Electronics and Electricity                         | 0607                 |

| Flomentory Porticles and                            |                      |

| High Energy<br>Fluid and Plasma                     | 0798                 |

| Fluid and Plasma                                    | 0759                 |

| Molecular                                           | 0609                 |

| Nuclear                                             | 0610                 |

| Ontics                                              | 07.52                |

| Radiation                                           | 0756                 |

| Solid State                                         | 0611                 |

| Statistics                                          | 0463                 |

| Applied Sciences                                    |                      |

| Applied Sciences                                    | 0244                 |

| Applied Sciences Applied Mechanics Computer Science | 0004                 |

| Computer science                                    | 0704                 |

|                                                     |                      |

| Engineering General Aerospace Agricultural Autamotive Biomedical Chemical Civil Electronics and Electrical Heat and Thermodynamics Hydraulic Industrial Marine Materials Science Mechanical Metallurgy Mining Nuclear Packaging | 0539<br>0540<br>0541<br>0542<br>0543<br>0544<br>0544<br>0546<br>0547<br>0794<br>0548<br>0743<br>0551<br>0552 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Petroleum Sanitary and Municipal System Science                                                                                                                                                                                 | 0554                                                                                                         |

| System Science                                                                                                                                                                                                                  | 0790                                                                                                         |

| Geolechnology                                                                                                                                                                                                                   | 0428                                                                                                         |

| Plastics Technology                                                                                                                                                                                                             | 0795                                                                                                         |

| Geotechnology Operations Research Plastics Technology Textile Technology                                                                                                                                                        | 0994                                                                                                         |

| PSYCHOLOGY                                                                                                                                                                                                                      |                                                                                                              |

| PSTCHULUGT<br>General<br>Behavioral                                                                                                                                                                                             | 0621                                                                                                         |

| Clinical                                                                                                                                                                                                                        | . 0622                                                                                                       |

| Developmental                                                                                                                                                                                                                   | .0620                                                                                                        |

| Experimental                                                                                                                                                                                                                    | 0623                                                                                                         |

| Personality                                                                                                                                                                                                                     | 0625                                                                                                         |

| Personality<br>Physiological<br>Psychobiology<br>Psychometrics                                                                                                                                                                  | 0989                                                                                                         |

| Psychobiology                                                                                                                                                                                                                   | 0349                                                                                                         |

| Social                                                                                                                                                                                                                          | 0451                                                                                                         |

|                                                                                                                                                                                                                                 |                                                                                                              |

#### © 1995 Hung, Kai Yiu

All Rights Reserved. No part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author.

Dedicated with love to my parents,

#### Abstract

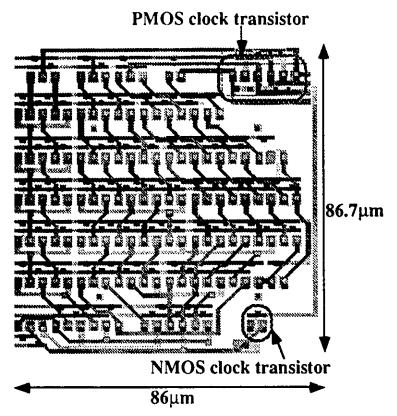

This thesis presents the architecture and the algorithm of the Hierarchy for Pattern Extraction (HyPE) artificial neural network. The training algorithm and the recalling algorithm of the HyPE artificial neural network are rewritten into C based on a Smalltalk prototype. A switching tree minimization program is introduced that provides logic minimization capable of handling a higher transistor tree height and merges several transistor trees. The Northern Telecom 0.8µ Bipolar Complementary Metal Oxide Semiconductor (BATMOS) technology is used to implement the designs in this thesis. There are two final dynamic neuron designs that have been verified and fabricated. One neuron uses the True Single Phase Clocking (TSPC) Latch and the other neuron uses the Ultra Fast Dynamic Current Steering (UCDCS) latch at the output of the dynamic functional block. The verification of the functional blocks for both neuron designs is done using SPICE simulation. The highest clocking speed applied to the TSPC neuron and the UCDCS neuron are 50MHz and 66MHz, respectively. Additionally, by isolating one of the transistor trees from the functional block, the clocking speed up to 333MHz can be achieved. Finally, a test chip including these two final dynamic neuron designs has been fabricated.

## Acknowledgements

I would like to express my sincere thanks and appreciation to my supervisor, Dr. G. A. Jullien, and my co-supervisor, Dr. W. C. Miller for their tremendous support and guidance throughout the progress of this thesis. I would also like to thank to Bruce Erickson and Alagu Annaamalai for guiding me on the research at the beginning. I would also need to thank Subramanian Kumar for working out the algorithm and programming. I need to thank Marjan Shahkarami, John and Dimitris Phoukas for helping me from the layout design problem to writing the thesis. Finally I have to express my deepest gratitude to my parents for their patience, support and encouragement on every aspect of my life.

# **Table of Contents**

| Abstract                                |                                                         | v  |

|-----------------------------------------|---------------------------------------------------------|----|

| Acknowledge                             | ements                                                  | vi |

|                                         | itents                                                  |    |

|                                         | es                                                      |    |

|                                         | S                                                       |    |

|                                         | ols                                                     |    |

| Chapter 1                               | Introduction                                            |    |

| Chapter 1                               | Motivation of the thesis                                |    |

| • • • • • • • • • • • • • • • • • • • • |                                                         |    |

| 1.2                                     | Background                                              |    |

| 1.3                                     | Thesis objective                                        |    |

| 1.4                                     | Thesis Organization                                     |    |

| Chapter 2                               | Hierarchy for Pattern Extraction                        |    |

| 2.1                                     | Introduction                                            |    |

| 2.2                                     | Background of ANN                                       |    |

| 2.3                                     | Architecture of HyPE                                    |    |

|                                         | 2.3.1 Neuron Model                                      |    |

| 2.4                                     | The HyPE Algorithm                                      | 12 |

|                                         | 2.4.1 Training Pattern                                  | 13 |

|                                         | 2.4.2 Overall Training Algorithm                        | 15 |

|                                         | 2.4.3 Initialization Algorithm                          | 10 |

|                                         | 2.4.5 Sleep Algorithm                                   | 20 |

|                                         | 2.4.6 Recalling Process                                 | 23 |

| 2.5                                     | Summary                                                 |    |

| Chapter 3                               | Switching Tree Minimization & Latch Designs             | 25 |

| 3.1                                     | Introduction                                            |    |

| 3.2                                     | Switching Tree Minimization                             |    |

| ع.ر                                     | 3.2.1 Minimization Algorithm                            | 26 |

|                                         | 3.2.2 Switching Tree Minimization Program               |    |

| 3.3                                     | Latch Design                                            |    |

| <b>515</b>                              | 3.3.1 True Single Phase Clocking Latch (TSPC)           |    |

|                                         | 3.3.1.1 TSPC Design Using in teell Library              | 36 |

|                                         | 3.3.1.2 A Full Custom TSPC latch Design                 |    |

|                                         | 3.3.2 Ultra-Fast Dynamic Current Steering Latch         |    |

| 3.4                                     | Summary                                                 |    |

| Chapter 4                               | VLSI Implementation of HyPE                             |    |

| 4.1                                     | Introduction                                            |    |

| 4.2                                     | Pipeline Neuron Design Approach                         |    |

|                                         | 4.2.1 Logic Gate Neuron Design                          |    |

|                                         | 4.2.1.1 8-input Pipeline Neuron Design                  |    |

|                                         | 4.2.1.2 4-input Pipeline Neuron Design                  |    |

|                                         | 4.2.1.3 Stow 8-input Pipeline Neuron Design             |    |

|                                         | 4.2.2.1 8-input Switching Tree Pipeline Dynamic Neuron. | 53 |

|                                         | 4.2.2.2 7-input Switching Tree Pipeline Neuron Design   |    |

|                                         |                                                         |    |

| 4.3        | Single Block Neuron Design Approach 4.3.1 Reorganized Cell 4.3.2 3-input Neuron Design | 57 |

|------------|----------------------------------------------------------------------------------------|----|

| 4.4        | Discussion of Neuron Designs                                                           |    |

| 4.5        | Simulation of Neuron Designs                                                           |    |

| 4.6        | Additional Information on the Neuron Design                                            |    |

| 4.7        | Test Cell for Fabrication                                                              | 64 |

| 4.8        | Summary                                                                                | 66 |

| Chapter 5  | Conclusion                                                                             | 67 |

| 5.1        | Contributions of the Thesis                                                            |    |

| 5.2        | Future Work                                                                            |    |

| REFERENCE  | ES                                                                                     |    |

| Appendix A | The Training Algorithm of HyPE                                                         | 72 |

| A.1        | Equations                                                                              |    |

| A.2        | HyPE Algorithm                                                                         |    |

|            | A.2.1 Overall Training Process                                                         |    |

|            | A.2.2 Initialize Brain Process                                                         | 73 |

|            | A.2.3 Wake Process                                                                     |    |

|            | A.2.4 Sleep Process                                                                    | 74 |

| Appendix B | Source Code of All Programs                                                            | 77 |

| B.1        | C Code for generating input patterns                                                   |    |

| B.2        | Training Program                                                                       |    |

| B.3        | recall program                                                                         |    |

| B.4        | Switching Tree Minimization Program                                                    |    |

| Appendix C | Layout of the Design                                                                   |    |

| Appendix D | Pads Setting in the Test Cell                                                          |    |

| ADDCHUIX D | Faus setting in the rest Cen                                                           |    |

# **List of Figures**

| Figure 2.1  | The Diagram of the Brain Model                                  | 7  |

|-------------|-----------------------------------------------------------------|----|

| Figure 2.2  | HyPE Architecture                                               |    |

| Figure 2.3  | Diagram of a McCulloch-Pitts neuron                             |    |

| Figure 2.4  | Schematic Diagram of the neuron in HyPE                         | 11 |

| Figure 2.5  | Characteristic distribution of Groups A,B,C                     | 13 |

| Figure 2.6  | Character A, B, C                                               | 14 |

| Figure 2.7  | Examples from Character A's pattern                             |    |

| Figure 2.8  | Plot of the Similarity Distribution of Character A, B, C        | 15 |

| Figure 2.9  | The Flow Chart of the Overall Training Algorithm                |    |

| Figure 2.10 | Flow chart of the Wake Algorithm                                | 18 |

| Figure 2.11 | An Example of Imprinting a Neuron                               | 20 |

| Figure 2.12 | Flow Chart of the Sleep Algorithm                               | 21 |

| Figure 2.13 | An Example of Finding, and                                      |    |

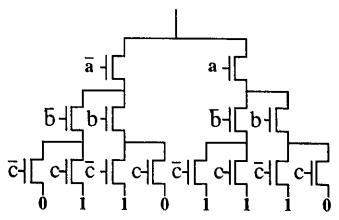

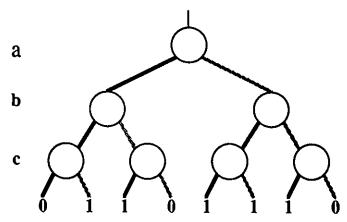

| Figure 3.1  | The Dynamic Logic Diagram                                       |    |

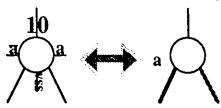

| Figure 3.2  | Graphical Symbol of Tree Component                              | 27 |

| Figure 3.3  | Full Tree of Transistor                                         |    |

| Figure 3.4  | Graphical Representation of Full Tree of Transistor             | 28 |

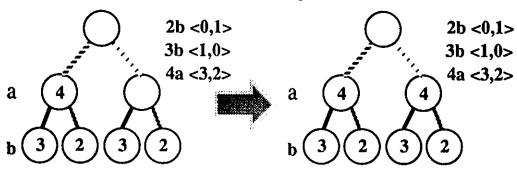

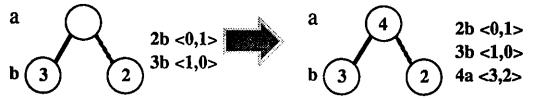

| Figure 3.5  | Rule 1 of Switching Tree Minimization                           | 29 |

| Figure 3.6  | Rule 2 of Switching Tree Minimization                           | 29 |

| Figure 3.7  | Rule 3 of Switching Tree Minimization                           | 29 |

| Figure 3.8  | The Graphical Representation with Node Number and the Key Table | 30 |

| Figure 3.9  | Merged Graphical Representation Tree                            | 30 |

| Figure 3.10 | The Reversed Variable Order Minimization                        | 31 |

| Figure 3.11 | An Example of "Don't Care" Case                                 | 31 |

| Figure 3.12 | The Merged Tree Graphical Representation                        | 33 |

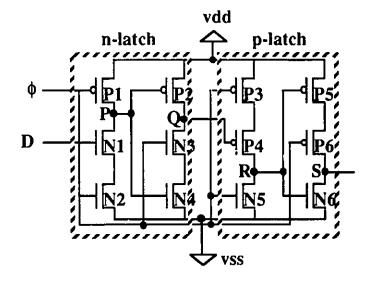

| Figure 3.13 | True Single Phase Clocking (TSPC) Latch                         | 34 |

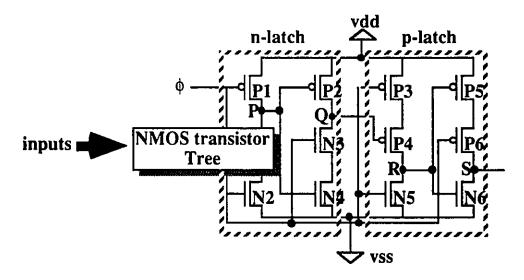

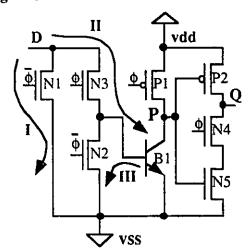

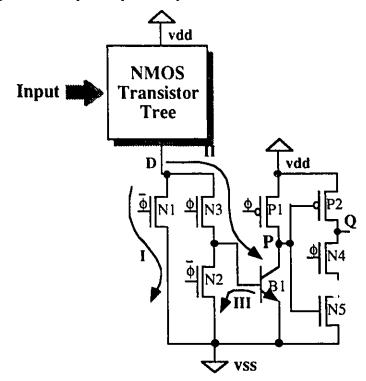

| Figure 3.14 | Replace the N1 transistor with the NMOS Transistor Tree         |    |

| Figure 3.15 | One of the Basic Cell of tcell in BATMOS                        | 36 |

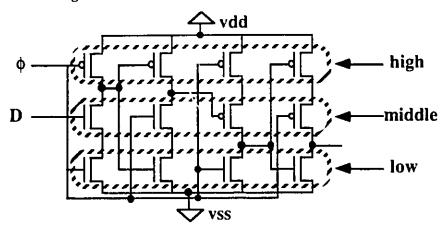

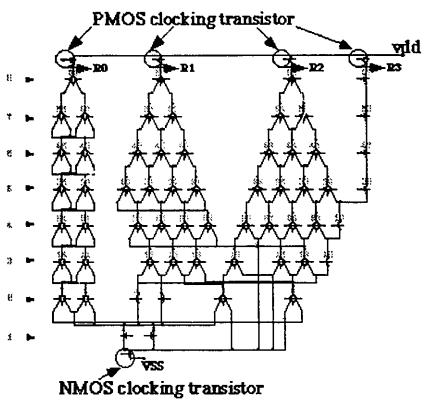

| Figure 3.16 | Transistor Level Division of TSPC Latch                         | 37 |

| Figure 3.17 | TSPC Latch Designed in tcell Format                             | 38 |

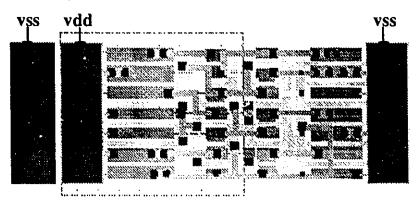

| Figure 3.18 | TSPC Latch Customized Layout Design                             | 38 |

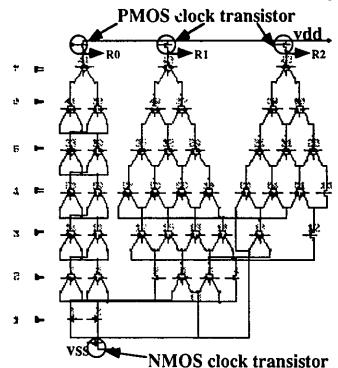

| Figure 3.19 | Master n-latch of UCDCS Latch                                   |    |

| Figure 3.20 | Input Replaced by NMOS Transistor Tree in n-latch               |    |

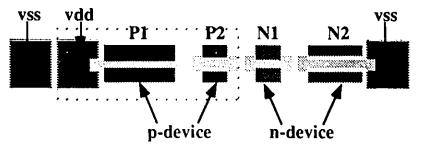

| Figure 3.21 | UCDCS Latch layout Design                                       |    |

| Figure 3.22 | BJT Transistor in BiCMOS                                        |    |

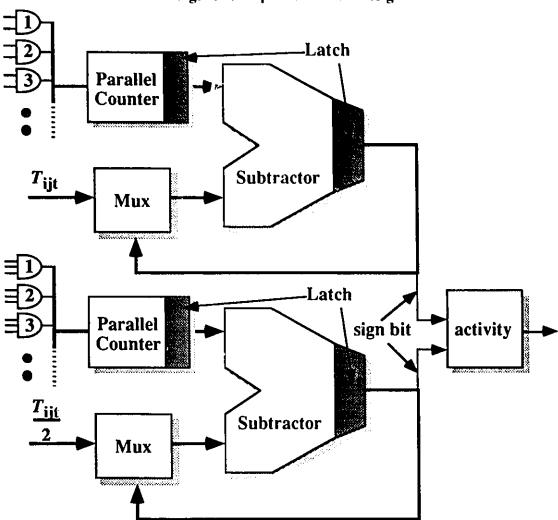

| Figure 4.1  | Pipeline Neuron Design                                          | 44 |

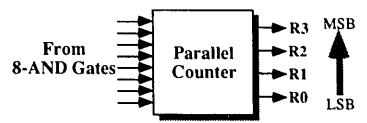

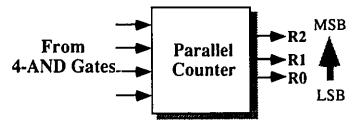

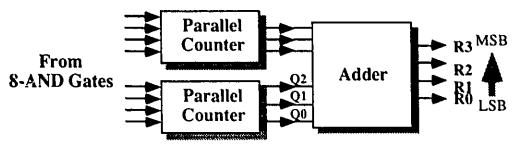

| Figure 4.2  | 8-bit Parallel Counter                                          | 46 |

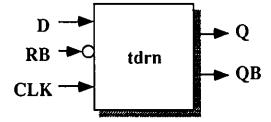

| Figure 4.3  | The Resettable D-type Negative-edge Flip-Flop(tdrn)             | 46 |

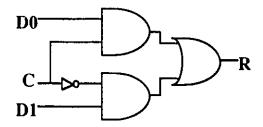

| Figure 4.4  | Schematic of the 2-to-1 Multiplexer                             | 47 |

|             |                                                                 |    |

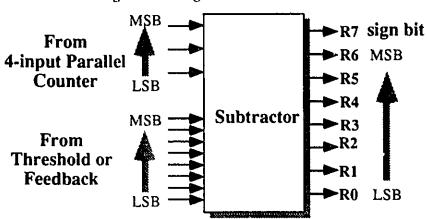

| Figure 4.5  | Diagram of the 8-4 Subtractor                                   | 47  |

|-------------|-----------------------------------------------------------------|-----|

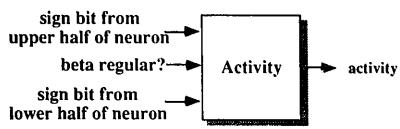

| Figure 4.6  | Diagram of the Activity Block                                   | 48  |

| Figure 4.7  | Diagram of the 4-bit Parallel Counter                           | 48  |

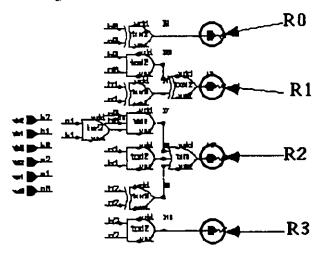

| Figure 4.8  | Diagram of 8-3 Subtractor                                       | 49  |

| Figure 4.9  | Diagram of a Slow 8-bit Parallel Counter                        | 50  |

| Figure 4.10 | Schematic of the Slow 4-bit Parallel Counter                    | 5() |

| Figure 4.11 | Schematic of the 3-3 Adder                                      | 51  |

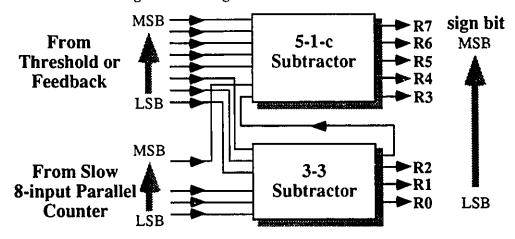

| Figure 4.12 | Diagram of Slow 8-4 Subtractor                                  | 51  |

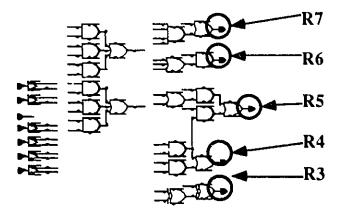

| Figure 4.13 | Schematic of 5-1-e Subtractor                                   | 52  |

| Figure 4.14 | Schematic of 3-3 Subtractor                                     |     |

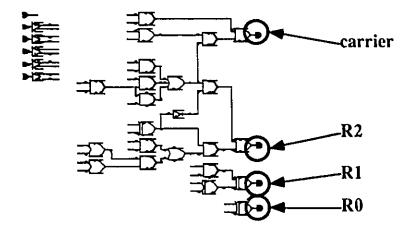

| Figure 4.15 | 8-bit Switching Tree Parallel Counter                           | 53  |

| Figure 4.16 | Schematic Symbol and the Graphical Symbol                       | 54  |

| Figure 4.17 | Schematic of the 8-4 Switching Tree Subtractor                  | 54  |

| Figure 4.18 | Schematic of the 7-bit Parallel Counter with Complement Outputs | 55  |

| Figure 4.19 | Schematic of the 8-3 Subtractor with Complemented Outputs       | 56  |

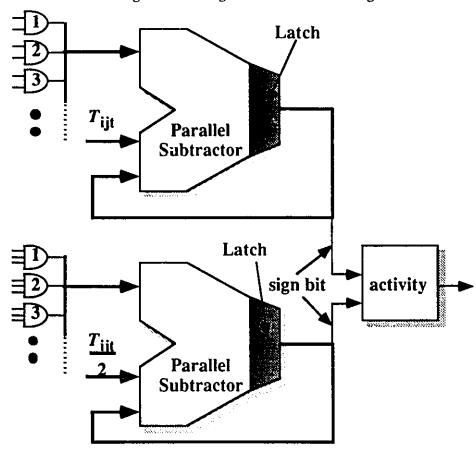

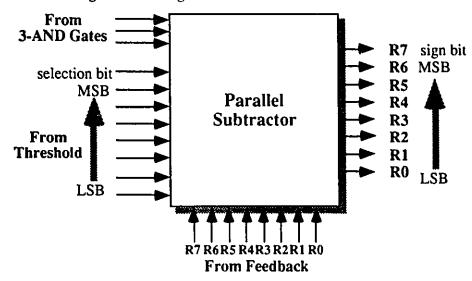

| Figure 4.20 | Single Block Neuron Design                                      | 57  |

| Figure 4.21 | Diagram of the 3-bit Parallel Subtractor                        | 58  |

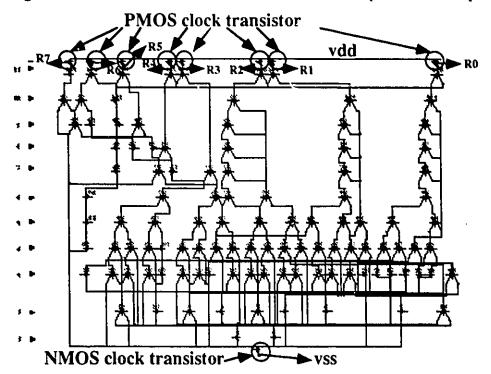

| Figure 4.22 | Schematic of 3-bit Parallel Subtractor using TSPC Latch         |     |

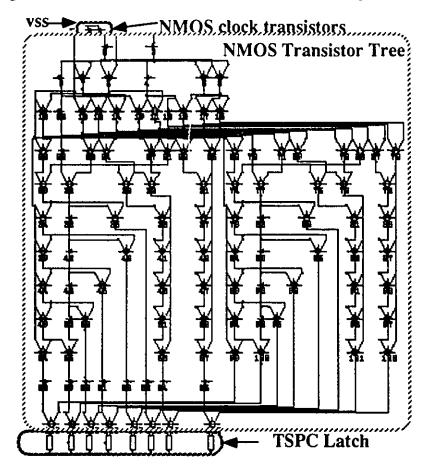

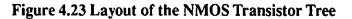

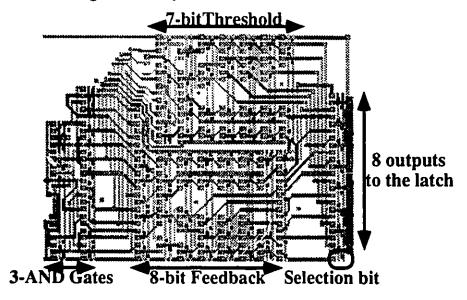

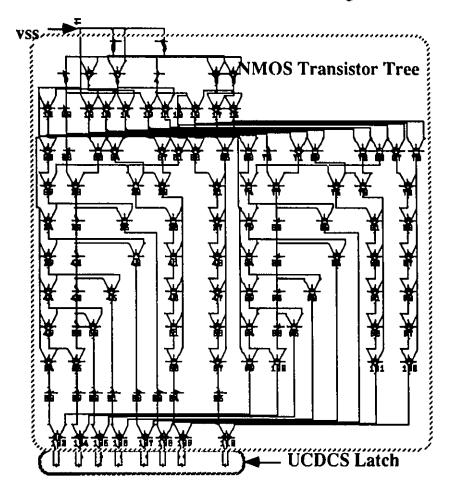

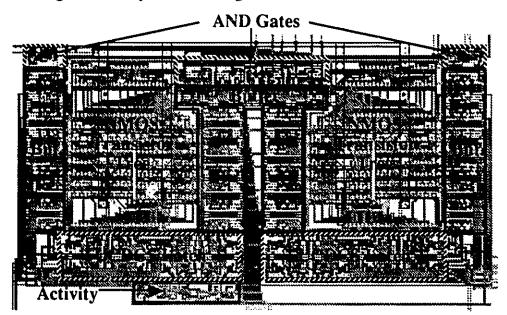

| Figure 4.23 | Layout of the NMOS Transistor Tree                              | 59  |

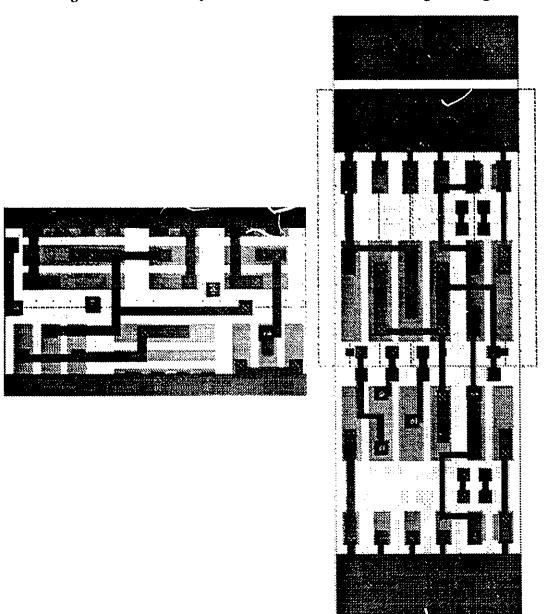

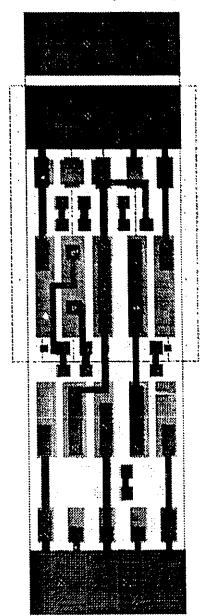

| Figure 4.24 | Schematic of 3-bit Parallel Subtractor Using the UCDCS Latch    | 60  |

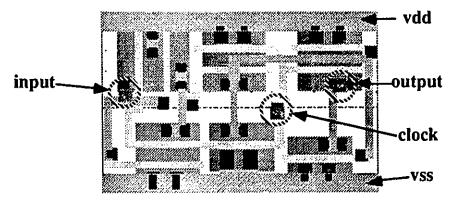

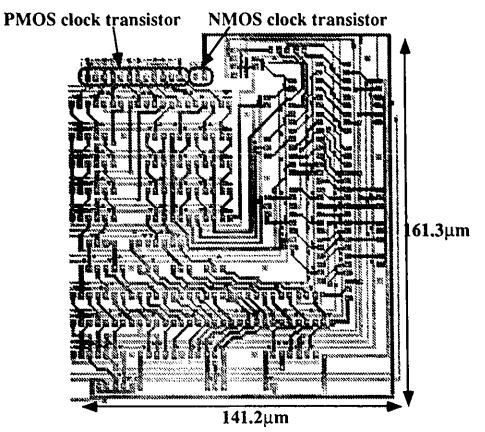

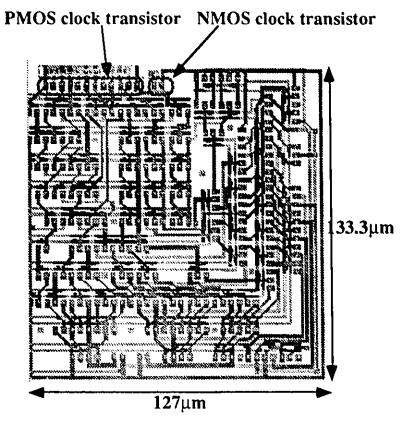

| Figure 4.25 | Layout of the Single Block Neuron with UCDCS Latch              | 61  |

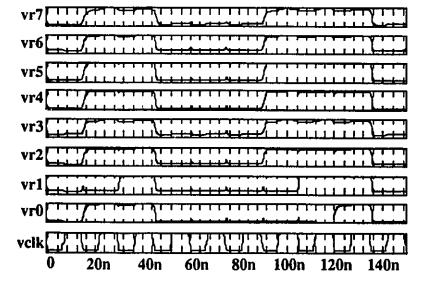

| Figure 4.26 | SPICE Simulation of the TSPC Latch Dynamic Neuron               |     |

| Figure 4.27 | SPICE Simulation of the UCDCS Latch Dynamic Neuron              | 63  |

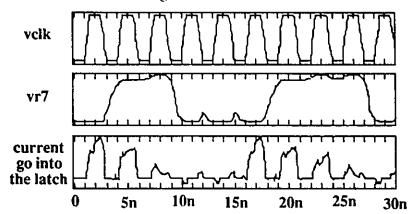

| Figure 4.28 | Simulation of Single UCDCS Latch in 3-bit Parallel Subtractor   | 64  |

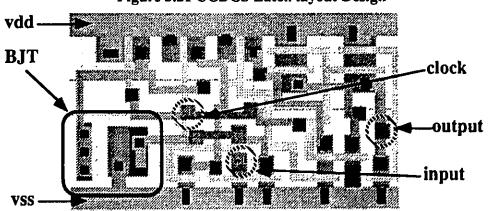

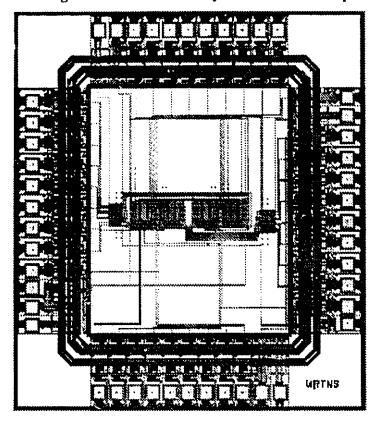

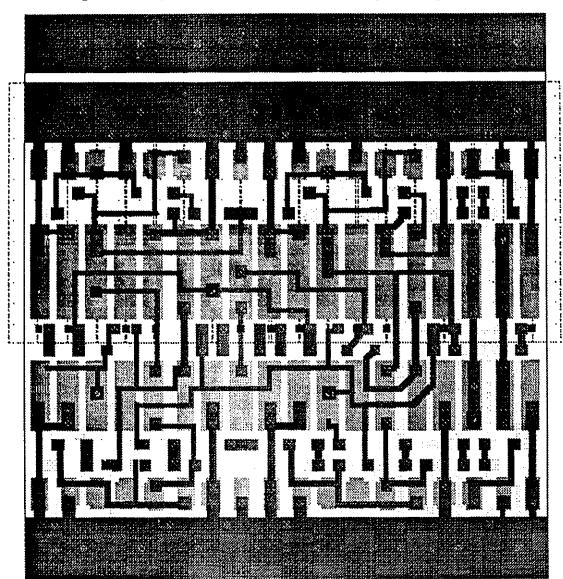

| Figure 4.29 | The Mask Layout of the Test Chip                                | 65  |

| Figure C.1  | Schematic of the 8-bit Counter                                  | 98  |

| Figure C.2  | Schematic of the 8-4 Subtractor                                 | 99  |

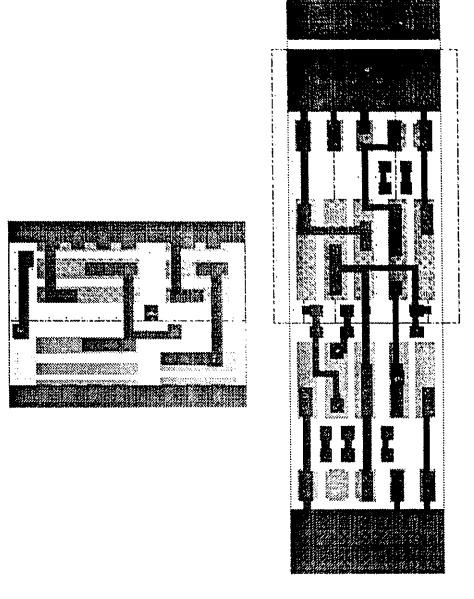

| Figure C.3  | Layout of 8-input Pipeline Logic Gate Neuron                    | 100 |

| Figure C.4  | Schematic of the 4-bit Counter                                  | 101 |

| Figure C.5  | Schematic of the 8-3 Subtractor                                 | 102 |

| Figure C.6  | Layout of 4-input Pipeline Logic Gate Neuron                    | 103 |

| Figure C.7  | Layout of the Resettable D-type Negative-edge Flip-Flop         | 104 |

| Figure C.8  | AND-2 Layout in Custom (left) and Tcell (right)Design           | 105 |

| Figure C.9  | AND-3 Layout in Custom (left) and Tcell (right) Design          | 106 |

| Figure C.10 | Buffer Layout in Custom (left) and Tcell (right) Design         | 107 |

| Figure C.11 | Inverter Layout in Custom (left) and Tcell (right) Design       | 108 |

| Figure C.12 | OR-2 Layout in Custom (left) and Tcell (right) Design           |     |

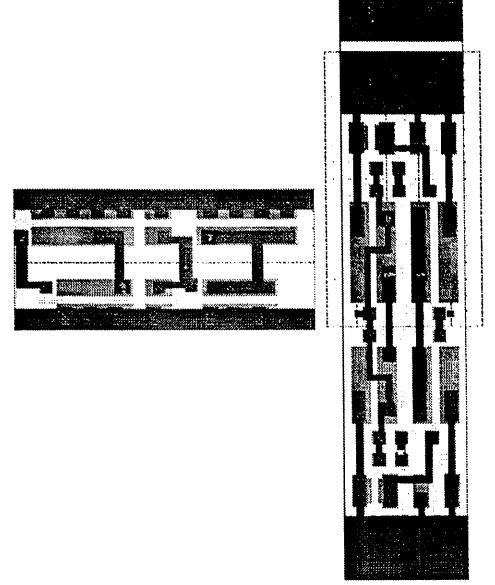

| Figure C.13 | Layout of the 8-bit Parallel Counter with Complement Outputs    | 110 |

| Figure C.14 | Layout of the 8-4 Subtractor with Complement Outputs            | 111 |

| Figure C.15 | Layout of 7-bit Parallel Counter with Complement Outputs        |     |

| Figure C.16 | Layout of the 8-3 Subtractor With Complement Outputs            |     |

| Lni | crsity | οt | W IT | iosor |

|-----|--------|----|------|-------|

# **List of Tables**

| Table 2.1. | Presentation Method's Information                              | 16 |

|------------|----------------------------------------------------------------|----|

| Table 2.2. | Information of Initializing Each Level                         | 17 |

| Table 2.3. | Novelty Arousal controlled Threshold of Virgin Neuron in Level |    |

| Table 2.4. | Limitation of Imprinting Virgin Neuron in each Level           | 20 |

| Table 2.5. | The configuration of Sleep Algorithm                           | 21 |

| Table 3.1. | An Example of Truth Table                                      |    |

| Table 3.2. | Status of Master n-latch in TSPC Latch                         | 35 |

| Table 3.3. | Status of Slave p-latch in TSPC Latch                          | 35 |

| Table 3.4. | Different Combinations of Transistor Size                      |    |

| Table 4.1. | Neuron Parameter Setting                                       |    |

| Table 4.2. | Comparison of Teell and Reorganized Logic Gates                |    |

| Table 4.3. | Capacity of Core in Fabrication                                |    |

| Table 4.4. | Estimation of area per logic gate                              |    |

| Table 4.5. | Functionality of Pad                                           |    |

| Table D.1  | Configuration of the Pad                                       |    |

# List of Symbols

#### **Explaination of Subscripts**

e.g. X<sub>n, i, j, t</sub>

i runs across the neurons in a present level.

j is the level or layer(input(0), alpha(1), Beta(2), Gamma(3), Basal Ganglia)

l is the presentation method (1 is the initial presentation, 2 is the regular presentation, 3 is presentation with the target and non-target pattern)

n runs across the neurons in the upper level.

t is the time step (Pattern application step).

#### List of Notations

AVE Average number of inputs from new virgin alpha neuron to each regular Beta neuron (integer). number of the regular neuron in beta level after the initial wake period  $\beta_{initial}$ (integer). BTF Beta Threshold factor (integer). Neuron Connectivity with the previous level (boolean vector).  $\mathbf{C}_{ii}$  $C_{nijt}$ The element of  $C_{iit}$  (boolean). Regular (for all neurons in previous level, 0 if virgin, 1 if regular, for alpha  $\mathbf{E}_{i-1,t}$ level elements of E are all '1's) (boolean vector). The element of  $E_{i-1, t}$  (boolean).  $E_{n, i-1,t}$  $\mathbf{F}_{j-1,t}$ Firing status record of neurons in previous level (boolean vector).

| The element of $\mathbf{F}_{j+1,j}$ (boolean).                                                       |

|------------------------------------------------------------------------------------------------------|

| The firing population (integer vector).                                                              |

| The element of $\mathbf{FP}_{ji}$ (integer).                                                         |

| Firing status (boolean).                                                                             |

| The input history (integer vector).                                                                  |

| The element of $\mathbf{IH}_{ji}$ (integer).                                                         |

| The input population (integer vector).                                                               |

| The element of $IP_{jt}$ (integer).                                                                  |

| The input record (integer vector).                                                                   |

| The element of $IR_{jl}$ (integer).                                                                  |

| a constant factor by which the pain factor is increased each time pain is experienced.               |

| contants for the input population.                                                                   |

| contants for the input population.                                                                   |

| The maximum number of times that a set of inputs will be used in the $l$ 'th presentation (integer). |

| The population of virgin neuron in alpha level (integer vector).                                     |

| The distribution of firing population of beta level, FP <sub>2,1</sub> (integer vector).             |

| The number of connection of a neuron in each level (integer).                                        |

| The minimum gamma firing (integer).                                                                  |

| The number of neurons in $j$ 'th level (integer).                                                    |

|                                                                                                      |

| NA             | The Novelty Arousal value (integer).                                                            |

|----------------|-------------------------------------------------------------------------------------------------|

| NAC            | Novelty Arousal Criterion (integer).                                                            |

| NAM            | The Novelty Arousal Monitor Value (boolean).                                                    |

| $NV_j$         | The size of virgin neurons in $j$ 'th level (integer).                                          |

| $\mathbf{P}_t$ | The input vector t (boolean vector).                                                            |

| $P_{jl}$       | The limit number of firing of virgin neuron in $l$ 'th presentation at $j$ 'th level (integer). |

| PF             | The pain factor (real).                                                                         |

| PP             | The Pain & Pleasure (boolean).                                                                  |

| $R_{ijt}$      | Am I a regular before (1 is regular 0 is virgin) (boolean).                                     |

| $S_j$          | The size of neurons in $j$ th level (integer).                                                  |

| $S_{jt}$       | This is the set of all neurons in the j'th level $(S_{jt} = S_{R_{jt}} \cup S_{V_{jt}})$ .      |

| $S_{R_{jt}}$   | This is the set of all regular neurons in the j'th level.                                       |

| $S_{V_{jt}}$   | This is the set of all virgin neurons in the j'th level.                                        |

| $SR_j$         | The size of regular neurons in j'th level (integer).                                            |

| $T_{ijt}$      | Threshold of Neuron (integer).                                                                  |

| TNT            | TargetNonTarget (1 if target pattern, 0 if non-target pattern) (boolean).                       |

| $TP_l$         | The number of training pattern used in the $l$ training presentation (integer).                 |

والمعاورة والمستسبب والأوالات

#### **Functions**

Boolean Vector Sum

$\sum_{B} \mathbf{v}$

This counts the number of Boolean 1's in the Boolean vector V.

Vectorize Boolean Outputs

$\Psi_i[G_{iji}]$

This produces a vector of boolean outputs across the i index.

Normalizes vector

$\eta (IH_{\mu})$

This produces a normalized vector output of  $\mathbf{IH}_{jt}$ .

Vectorize Integer Outputs

$VI_{i}[B_{ijt}]$

This produces a vector of integer outputs across the i index.

Random Number

$\Re[low, high]$

This produces an integer number between low and high.

Generate Neuron

$\mathbf{N}[T_{ijt},R_{ijt},\mathbf{C}_{ijt},G_{ijt}]$  This allocate resource for a neuron.

# Chapter 1

#### Introduction

#### 1.1 Motivation of the thesis

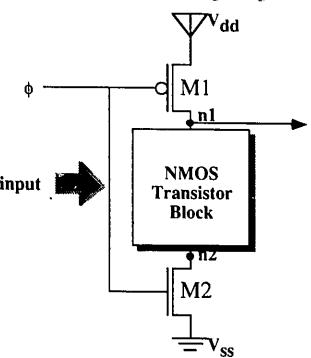

The Hierarchy for pattern extraction (HyPE) artificial neural network was originally proposed by Andrew Coward [1] in the early nineties. It was soon realized that it had the potential to become a complete digital network. A join project between Northern Telecom (NT) and the VLSI Research Group, University of Windsor, was proposed at the same time in order to explore the possibility of implementing HyPE in BATMOS, which was at the time the state of the art fabrication technology available at NT. Our starting basis was a prototype Smalltalk implementation of the HyPE algorithm written by Andrew Coward. As a proof of concept, a single neuron was selected for VLSI implementation. It was not too long before it was realized that the use of tcells, the BATMOS standard library elements, was very expensive in terms of space for this kind of application. Therefore a full custom dynamic logic style was adopted for the implementation of the neuron. This dynamic style is based on a recently proposed timing scheme, the True Single Phase Clock (TSPC), for which novel storage elements using the full advantages of BiCMOS technologies have been designed by the VLSI Group.

### 1.2 Background

The topic of the Artificial Neural Networks (ANNs) has been investigated for a long time. ANNs are widely used in different applications such as pattern recognition, optimization, product of predicting financial analysis and more.

Most of the ANNs work with analog neuron which are easy to program but not so easy to implement in silicon. Recently, researchers have developed digital neural networks, such as the adaptive probability neural network [6][7][8] and the HyPE artificial neural network. Although the digital ANN is easy to implement in silicon, it has the disadvantage that the size of the ANN can be several times larger than the analog ANN.

The HyPE artificial neural network is the focus of this thesis. The purpose of the HyPE artificial neural network is to provide the recognition of suggested patterns sent into the network. Since the HyPE artificial neural network is still under modification and it requires a long time to verify one set of parameters, we need a faster process in order to train the network. This thesis focuses on finding a way to improve the performance of the training process, using the Bipolar Complementary Metal Oxide Semiconductor (BiCMOS) technology provided by Northern Telecom. It also provides an implementation of the general neuron that involves all the functionality of each neuron in the architecture and is the most representative sub-function to implement under the algorithm of interest.

# **1.3** Thesis objective

The original objective of this thesis was to reverse engineer the algorithm from the Smalltalk program which was the only resource available to us in the beginning A rigorous description of the algorithm was to be written as part of this investigation. The other objective was to implement in the VLSI medium the full architecture (or some well defined part of it) in order to improve the training performance of the artificial neural network. As a side effect of this process, a new implementation of the switching tree

minimization procedure had to be written in order to generate the full custom implementations of the functional blocks of the neuron.

## 1.4 Thesis Organization

This thesis includes six chapters. Chapter 1 provides the background of this research and provides the structure of the each chapter in this thesis.

Chapter 2 introduces the hierarchy for pattern extraction (HyPE) artificial neural network. It provides the background, architecture and the algorithm of the HyPE artificial neural network. This chapter focuses on the architecture and the algorithm of the HyPE based on the original Smalltalk program written by L.Andrew Coward[1]. Both of them are discussed deeply step by step and compared with the modern artificial neural network.

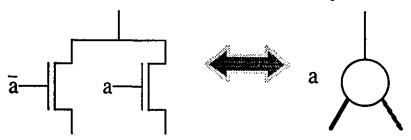

Chapter 3 presents the graphical switching tree minimization algorithm and the two latch designs that are used in this thesis. The graphical switching tree minimization algorithm is proposed by Bryant[14][19]. A switching tree minimization program written in c programming language is presented. The two latch designs are the true single phase clocking (TSPC) latch[12][15] and the ultra fast dynamic current steering (UCDCS) latch proposed by J.C. Czilli[12].

Chapter 4 presents the pipeline neuron implementation approach and the single block neuron implementation approach for the general neuron that can improve the training process of the HyPE artificial neural network. After that it goes through the other directory of approaches that are based on using the standard cell in 0.8µ BATMOS library (tcell) to design the neuron and using the dynamic logic with switching tree minimization to design the neuron. The two designs of 3-input single block dynamic neuron are chosen to use in the implementation of the general neuron. A test cell has been designed and submitted for fabrication.

Introduction Thesis Organization 3

The last chapter, Chapter 5, concludes the work done in this thesis. It provides suggestions for improving the architecture and the algorithm of the HyPE artificial neural network and the way to implement the neuron design for the possible future direction of the research in HyPE project.

Introduction Thesis Organization

# Chapter 2

Hierarchy for

Pattern

Extraction

#### 2.1 Introduction

This chapter discusses the artificial neural network that Andrew L. Coward brings out from the Brain operation system (The Brain Model). This chapter is divided into four sections. Section one is the introduction of this chapter. The second section is the background of the brain model. The third section is the architecture of the Hierarchy for Pattern Extraction (HyPE). The fourth section is the algorithm used in HyPE. The last section is the summary of the HyPE network.

## 2.2 Background of ANN

Artificial Neural Networks (ANNs) have been considered as an area of active research for a long time. Most of the developed artificial neural networks are based on the non-linearity neuron which uses a non-linearity function such as a sigmoid function. These kinds of artificial neural networks have some similarities, such as the non-linearity neuron, fixed network size, ease of simulation, and difficulty to fabricate in Very Large Scale Integrated (VLSI). Although the most current VLSI circuit technology is used, it still faces some difficulty, regarding

fabrication. The original design in the design environment and after the fabrication may have difference dimensions. These differences may be small but they could create a big problem due to the nature of artificial neural networks in VLSI. Since most of the artificial neural networks use a non-linearity function at the output of a neuron, Either fault tolerance of the fabrication process in the training process or to reduce the sensitivity of the artificial neural network need to be included.

There are several ways to bypass this problem. One is using discrete weight and sigmoid function in the software training process. When the artificial neural network is recalling, the hard-limit function replaces the sigmoid function as the non-linearity function of the artificial neuron. Since the artificial neural network uses the discrete weight and hard-limiting function, it adds great flexibility to the design. Although the fabrication process creates some dimension differences, the design can still handle that. This method was applied on two 3µ Complementary Metal-Oxide Semiconductor (CMOS) designs [3][4], on an optical coupled neural network and a 1.2µ CMOS design[5] on programmable optical coupled neural network. Another approach is the Hierarchy for Pattern Extraction (HyPE) artificial neural network architecture that created by Andrew L. Coward[1][21] using the Smalltalk-V programming language in 1990. The other one is the adaptive probability neural network[6][7][8][9]. The HyPE artificial neural network is the architecture, that this thesis focuses on.

# 2.3 Architecture of HyPE

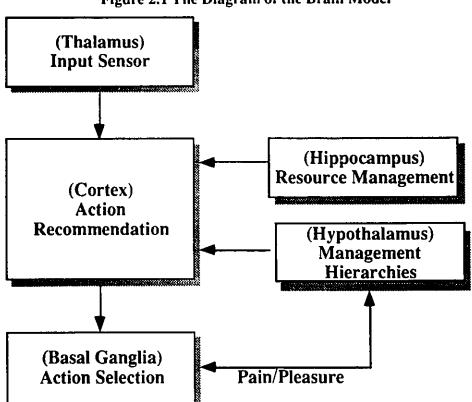

The diagram in Figure 2.1 shows the brain model of Andrew design. Input layer (Thalamus) is the sensor of the network. It presents sensory input signals to the middle layer. The middle Layer (Cortex) is a multilevel pattern declarative memory storage that keeps the characteristic of a target group and gives action recommendation to the network. There are three levels of neurons, Alpha level, Beta level and Gamma level. Each of these levels may contain more than a thousand neurons. It depends on the training process and the training pattern. Output layer (Basal Ganglia) is the action selection section. It contains a single artificial neuron. There are two management systems taking care of the

training process. One of them is resource management (Hippocampus). It contains the mapping of the middle layer neuron resources and assigns additional neurons if the network requires more memory storage. Hypothalamus is the other kind of control management. It controls the novelty arousal that sets the threshold value of each resource neuron (virgin neuron) in the middle layer. It also controls the pleasure and pain signal releasing to the output layer neuron.

Figure 2.1 The Diagram of the Brain Model

In the middle layer, each level contains two regions: the action recommendation region and the unused resource region. The unused resource region (virgin region) contains unused neurons and those are called virgin neurons. Neurons in the action recommendation region (regular region) are called regular neurons. These neurons are the memory storage of the target pattern that give the information, justifying whether the input pattern belongs to the target group or not. The characteristic and the functionality of these neurons will be discussed in more detail in the next section.

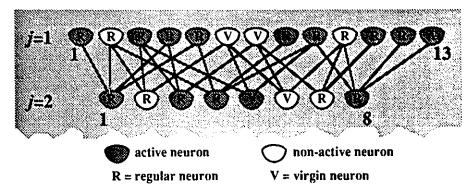

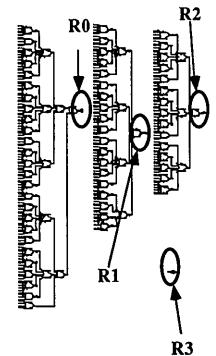

HyPE is a feedforward multilayer hierarchy artificial neural network implementing the Brain Model. The sensor gives the input signal to the input layer. Input signals of the alpha level, in middle layer, are the output signals of the input layer. The output signals of the alpha level neurons will penetrate to the beta level neuron as their input signals. The output signals of the beta level neurons will penetrate to the gamma level neurons and so are the output signals of gamma level. They will become the input signals of the basal ganglia layer neuron. The artificial neural network does not have any connection cross over levels or layers. e.g. there is no connectivity behaviour between alpha level's neurons and gamma level's neurons. It is shown in Figure 2.2.

INPUT LAYER **Input Characteristics** MIDDLE LAYER Alpha level Regular Virgin Region Region Resource Management Beta level Regular Virgin Region Region Novelty 'Gamma level Arousal Regular Virgin Region Region **OUTPUT LAYER** Pain/Pleasure **Action Selection**

Figure 2.2 HyPE Architecture

The arrows in the Figure 2.2 represent the direction of the signal and show all the possible connections between the layers and the levels. There are two things to notice in this figure. First, there is no connection between the beta virgin region and the gamma regular region. The missing connection is based on the present architecture. It can be modified easily by a small modification in the algorithm and the connection can be restored. The other missing connectivity is the gamma virgin region and the output layer. It is also based on the architecture, however it cannot be replaced unless there is a big modification on the algorithm.

#### 2.3.1 Neuron Model

In the HyPE architecture, two types of neurons are used. One is called regular neuron that has already recognized a specific pattern. The other one is called virgin neuron that has not yet recognized any pattern but has been configured to have a high potential to fire and then imprint. Imprinting is a process that transfers a virgin neuron to a regular neuron. This process will be discussed in more detail later. There are three levels of neurons in the middle layer and a neuron in output layer, Basal Ganglia layer. Basically, each neuron has a similar characteristic and functionality except for the output layer neuron. Each neuron contains a threshold value and connectivity to the upper level. The threshold value and connectivity of a neuron normally are unique. This will be clear in the algorithm section.

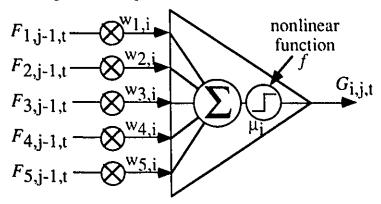

The activity of a neuron depends on the threshold value and connectivity of the neuron. Threshold value for each neuron is an integer number. Connectivity of a neuron is based on the history of the probability of upper level neurons' activity. It will be discussed in more detail in the algorithm. There is no weight on each connection. It is either connected or not. From a modern artificial neural network perspective, there are only two different kinds of weight for each connection. Those are 0 and 1. It is much simpler than the modern artificial neuron. The modern artificial neuron needs to have a weight on each input connection and needs to have a nonlinear activation function after the summation to determine the activity of the neuron. Figure 2.3 shows a schematic diagram of a

McCulloch-Pitts[2] neuron. This model can be equated as the following with notations that used in the HyPE neuron.

$$G_{i,j+1,t} = f_i \left( \sum_{n} w_{ni} G_{n,j,t} - \mu_i \right)$$

(2.1)

Figure 2.3 Diagram of a McCulloch-Pitts neuron

The firing status,  $G_{ijt}$ , represents the output signal of the i'th neuron in the j'th level in the t'th pattern of time process. The upper level firing status,  $F_{n, j-1, t}$ , represents the output signal of the n'th neuron in the (j-1)'th level in the t'th pattern of time process. It is same as the firing status,  $G_{i, j-1, t}$ .  $w_{ni}$ , represents the weight between the i'th neuron in the current level and the n'th neuron in the upper level. It can be a positive value or a negative value.  $\mu_i$  represents the threshold value of the i'th neuron in the j'th level. The nonlinear activation function, f, in McCulloch-Pitts' model is a step function, however it can be modified by using the other nonlinear activation function such as, the signum, sigmoid and threshold logic functions.

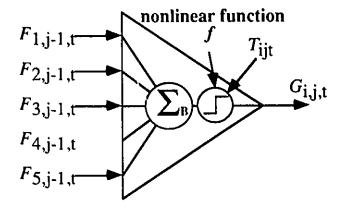

In HyPE, since there is no weight on the input connections, the firing status of the artificial neuron is determined from the sum of active input connections, and then compared with the threshold value of the neuron. If the sum of active input connections is greater or equal to the threshold value, the neuron fires (the firing status is 1). For example, if there are 3 active input connections, and the threshold value of the neuron is 3, then the neuron

fires. In the general case the firing status of a neuron can be modeled in the HyPE as follows:

$$G_{i,j,t} = f\left(\sum_{B} \left[C_{n,i,j,t} \wedge F_{n,j-1,t}\right] - T_{i,j,t}\right)$$

(2.2)

Figure 2.4 Schematic Diagram of the neuron in HyPE

$\sum_{B}$  is a function that sum up the boolean numbers. The threshold,  $T_{ijt}$ , represents the threshold of the i'th neuron in the j'th level in the t'th pattern of processing time. In here j would be declared more clearly. j is defined as the subscript notation for level or layer. In HyPE architecture, input layer is 0, alpha level is 1, beta level is 2, gamma level is 3 and the basal ganglia is 4. j is a positive integer value. The connectivity,  $C_{nijt}$ , represents the connection between the n'th neuron in the (j-1)'th level and the i'th neuron in the j'th level. As the diagram shows, the artificial neuron in HyPE architecture is not fully connected to the upper level or layer. The connectivity is defined by the firing population on the upper level. This will be defined more clearly in the next section. Since the threshold,  $T_{ijt}$ , is an integer value and so is the sum of the input signals, the signal that passes past through the nonlinear activation function, f, is no longer seen as a continuous value. This is one of the advantages of the HyPE architecture.

The model presented above is for a general neuron. It includes neurons in alpha level, virgin neurons in beta level and neurons in gamma level. Regular beta neurons need to have an additional condition to fire:

$$G_{ijt} = f \left\{ \frac{\left(\sum_{B} \left[C_{n,i,j,t} \wedge F_{n,j-1,t}\right] - T_{ijt}\right) \wedge}{\left(2\sum_{B} \left[C_{n,i,j,t} \wedge F_{n,j-1,t} \wedge E_{n,j-1,t}\right] - T_{ijt}\right)} \right\}$$

(2.3)

$E_{n, j-1, t}$  represents the status of the neuron, i.e. whether it is regular neuron (1) or a virgin neuron (0). The additional condition is applied because the regular beta neuron may have some connections from the virgin alpha neuron. This additional condition protects the over firing with the additional active virgin input neuron.

The neuron in the output layer, Basal Ganglia, is a unique neuron in the HyPE architecture. Its connectivity is controlled by the hierarchy management, hypothalamus, with the pain and pleasure feedback. It will be discussed in more detail in the algorithm description. The firing status of this neuron is determined by any active input connectivity occupied. In other words, if it has any active input connections, the neuron is firing. The model of the firing status of Basal Ganglia neuron is shown as in the following:

$$G_{1,4,t} = f\left(\sum_{B} \left[C_{n,1,4,t} \wedge F_{n,3,t}\right] - 1\right)$$

(2.4)

The firing status,  $G_{1,4,t}$ , is the Basal Ganglia neuron firing status.

# 2.4 The HyPE Algorithm

The HyPE algorithm is used to recognize a target group's patterns from the other group of patterns. Due to the complexity of the algorithm, it needs to be divided into 5 parts for further discussion. First is the input pattern for training and then is the overall training process. After that we have the detail of the initialization process, wake process, sleep process and the recalling process.

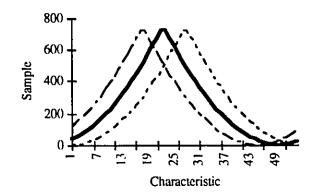

#### 2.4.1 Training Pattern

Patterns that are presented to the network are generated from sampling frequency distribution. The training process requires three groups of patterns, so each of the groups needs to create one distribution. Group distribution is the sampling of the group and the summing up the characteristic of the group. An example is given in Figure 2.5. These are the distributions of the 3 groups of object that have the bell shape sampling frequency. Each of the patterns that are presented to the network are generated from those distributions by randomly selecting 21 characteristic out of the 54 from the example of group distribution in Figure 2.5. The C programming source code, "C Code for generating input patterns" on page 77, is used to generate the 500 input patterns.

Figure 2.5 Characteristic distribution of Groups A,B,C

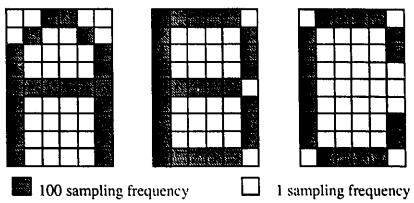

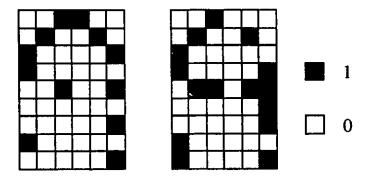

Here is a simple example of 3 characters A, B, C (Figure 2.6). Each character contains 54 characteristic components. Each characteristic component at the edge of the characters has 100 sampling frequency and the other characteristic component has 1 sampling frequency. A group of patterns for each character can be generated by randomly selecting from the sampling frequency distribution in this example.

Figure 2.6 Character A, B, C

There are two examples of patterns that are generated from the distribution of character A in Figure 2.7. These patterns have about 10% distortion from the original character. Using the examples in Figure 2.7, the patterns that are presented to the network are as follows:

001100[010010]10001[100000]001001[000000]000001[100000]100001 001000[010010]100000[100001[011011]000001]000001[100000]100001

Figure 2.7 Examples from Character A's pattern

Using these 500 patterns from each of the characters, one can show the similarity of those patterns. Character A is defined as the target pattern for this network. The similarity of those patterns is the sum of the sampling frequency of each of the characteristics that are presented in those patterns and then normalized with respect to the sum of the sampling frequency of the characteristics in the Character A. e.g. The sum of sampling frequency of Character A in Figure 2.6 is 2232. The similarity of those examples in Figure 2.7 is 53.763% and 67.2%, respectively.

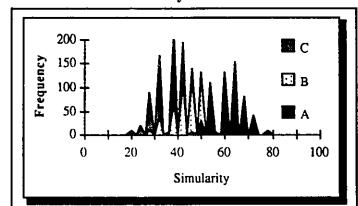

Figure 2.8 shows the similarity distribution of 500 patterns for each of the characters versus the frequency. The similarity distribution provides an idea of possible distinguish ability of the network. A group of character A has an average of 62% similarity, and the similarity of character B and character C is 44% and 36%, respectively.

Figure 2.8 Plot of the Similarity Distribution of Character A, B, C

#### 2.4.2 Overall Training Algorithm

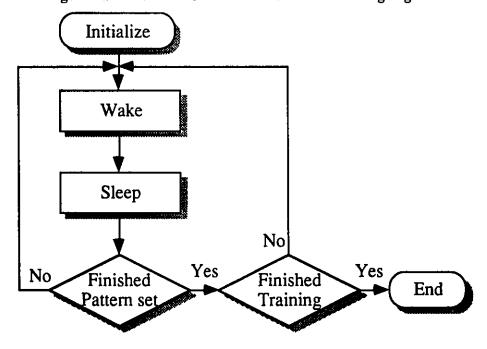

The overall training algorithm, shown as Figure 2.9, is divided into three parts: the initialization algorithm, the wake algorithm and the sleep algorithm.

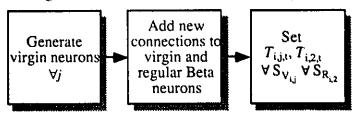

Figure 2.9 The Flow Chart of the Overall Training Algorithm

In the training algorithm, one needs three groups of patterns to train the neural network. One is the target group. The other two are the non-target groups. These patterns are used in three presentation methods. The first presentation method is to initialize the neural network focus on the target group of patterns. The second presentation method is to enhance the recognition of the target group's patterns. The third presentation method is to remove some of the error recognition of the non-target groups' patterns. It is done by putting some non-target groups' patterns into the artificial neural network. Table 2.1 shows the information of the number of patterns presented to the artificial neural network and the maximum number of times that these patterns are presented to the network. In the third presentation method, patterns that are presented to the network are interlacing. Using the example of character A, B and C, the order of patterns presented to the network is the pattern of character A, the pattern of character B, the pattern of character C, and then back to other pattern of character A and so on. Also the set of character A that is presented in the third presentation method is different from the first and the second presentation method.

Table 2.1. Presentation Method's Information

| Presentation<br>Method | Group 1<br>(Target) | Group 2<br>(Non-target) | Group 3<br>(Non-target) | presenting<br>times |

|------------------------|---------------------|-------------------------|-------------------------|---------------------|

| 1                      | 4                   | 0                       | 0                       | 1                   |

| 2                      | 20                  | 0                       | 0                       | 20                  |

| 3                      | 10                  | 10                      | 10                      | 20                  |

#### 2.4.3 Initialization Algorithm

Initialization algorithm is a process that creates a set of neurons in each level in the middle layer. Since the algorithm of HyPE is a digital artificial neural network, it has unlimited potential to learn if there are enough accessible neuron resources. The initialization

algorithm is to supply the amount of neuron resources to the artificial neural network for the first presentation method.

Table 2.2. Information of Initializing Each Level

| Level (j) | Neurons (NV <sub>j</sub> ) | Inputs (m <sub>jt</sub> ) |

|-----------|----------------------------|---------------------------|

| Alpha     | 150                        | 15                        |

| Beta      | 150                        | 17                        |

| Gamma     | 150                        | 14                        |

Table 2.2 show the number of neuron resources in each level when the artificial neural network initializes. It also shows the maximum number of input,  $m_{ji}$ , these neurons can have.

Connectivity of a neuron is randomly selected from the upper level's neurons. Since the artificial neural network does not have any regular neuron in the initial state, it randomly selects from the unit distribution of the population of virgin neurons. The following is the process to select the input connections to each neuron:

$$C_{\Re[1,N_{i-1}],i,j,0} \leftarrow 1; i \in S_{j,t}$$

(2.5)

$m_{jt}$  represents the maximum number of connections.  $\Re[1,N_{j-1}]$  is a random number that randomly selects among 1 and  $N_{j-1}$ .  $N_{j-1}$  is the number of neuron in the j-1 'th level or layer. Because the connections are randomly selected, it is possible to have some duplicated connections. Therefor the number of input connection may be less than  $m_{jt}$  show in Table 2.2.

### 2.4.4 Wake Algorithm

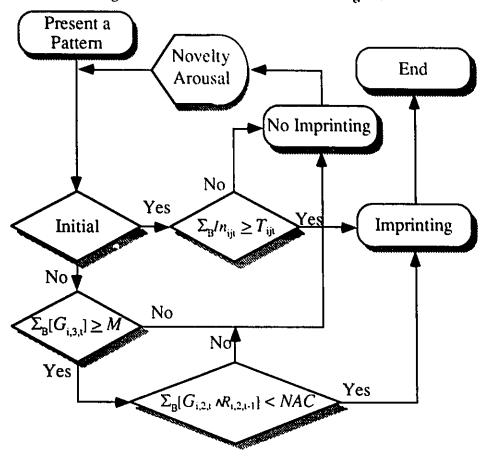

Wake algorithm is a process that trains the neurons in the middle layer to store the information of presented patterns. Flow chart in Figure 2.10 shows the wake algorithm.

Figure 2.10 Flow chart of the Wake Algorithm

A few points in the flowchart need to be discussed. When a pattern is presented to the artificial neural network, it will check to see that the neural network is in the initial state. Initial state is the one which the network is still using the first presentation method that focuses the neural network to recognize the target group. It will check that virgin neurons are active or not. If not, the novelty arousal value will increase. This value controls the threshold value of the virgin neuron in each level in middle layer. Table 2.3 shows how the novelty arousal value effects the threshold value of virgin neuron in each level. Since the neural network is at the initial state, novelty arousal value is set to 1 at the beginning. Therefore the threshold values of virgin neuron in alpha level, beta level and gamma level are 7, 7 and 6, respectively. At the second and third presentation method, the novelty arousal value is set to 0 at the beginning. This is going to let the artificial neural network

check that the pattern is already recognized. That is done because no virgin neuron will have more the 50 input connections.

| Table 2.3. Novelty Arousal | controlled Threshold of | Virgin Neuron in Level |

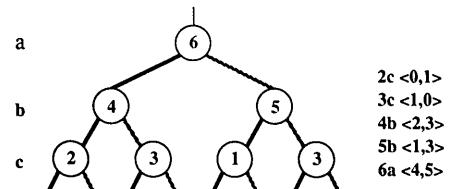

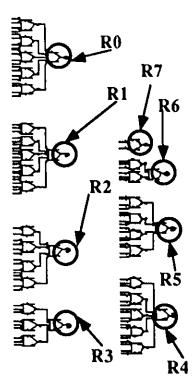

|----------------------------|-------------------------|------------------------|