#### **University of Windsor**

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1994

# BiCMOS technology and some applications in high performance arithmetic structures.

James Christopher. Czilli University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Czilli, James Christopher., "BiCMOS technology and some applications in high performance arithmetic structures." (1994). *Electronic Theses and Dissertations*. 1296. https://scholar.uwindsor.ca/etd/1296

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Sibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

August of the Court of the state of the second

Charles North Williams

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

\_\_\_

Canadä

# BiCMOS Technology and Some Applications in High Performance Arithmetic Structures

by

James Christopher Czilli

A Thesis

Submitted to the Faculty of Graduate Studies through the

Department of Electrical Engineering in Partial Fulfillment

of the Requirements for the Degree of

Master of Applied Science

at the

University of Windsor

Windsor, Ontario February, 1994.

Acquisitions and Bibliographic Services Branch

395 Weilington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your fam Lichter epiterproper

CAN DEC. STATE WHEN PERSON

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

----

ISBN 0-315-93262-7

| Name | TRIMES      | <i>(</i> . | CZILL | 1 |

|------|-------------|------------|-------|---|

|      | <del></del> |            |       | _ |

Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

ELECTRONICS AND ELECTRICAL FRANCERING

SUBJECT TERM

#### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND THE ARTS     | Psychology                  | 0525 | PHILOSOPHY, RELIGION AND |      | Ancient                     | 0579   |

|---------------------------------|-----------------------------|------|--------------------------|------|-----------------------------|--------|

| Architecture 0729               | Reading                     | 0535 | THEOLOGY                 |      | ntedieval                   | 0581   |

| Art History 0377                | Religious                   | 0527 |                          | 0422 | Modern                      | 0582   |

| Cinema 0900                     | Sciences                    | 0714 |                          | 0422 | Black                       | 0328   |

| Dance 0378                      | Secondary                   | 0533 | Religion                 | 0010 | African                     | G331   |

| Fine Arts 0357                  | Social Sciences             | 0534 |                          | 0318 | Asia, Australia and Oceania | 0332   |

|                                 | Sociology of                | 0340 |                          | 0321 | Canadian                    | 0334   |

|                                 | Special .                   | 0529 |                          | 0319 | European                    | 0335   |

| 100111011111                    | Special<br>Teacher Training | 0530 | History of .             | 0320 | Lohn American               | 0336   |

|                                 |                             | 0710 |                          | 0322 | Middle Eastern              | 0333   |

| Mass Communications 0708        | Technology                  | 0288 | Theology                 | 0469 | United States               | 0337   |

| Music 0413                      | Tests and Measurements      | 0747 | =-                       |      | History of Science          | 0383   |

| Sprech Communication 0459       | Vocational .                | Q/4/ | SOCIAL SCIENCES          |      |                             | 0368   |

| Theater . 0465                  | ANGUACE HITTRATURE AND      |      | American Studies         | 0323 | Law<br>Political Science    | 03.40  |

|                                 | Language, literature and    | ,    | Anthropology             |      |                             | 0615   |

| EDUCATION                       | LINGUISTICS                 |      | Archoeology              | 0324 | General                     | 0013   |

| General 0515                    | Language                    |      | Cultural                 | 0326 | International Law and       |        |

| Administration                  | General                     | 0679 | Physical                 | 0327 | Relations                   | 0016   |

| Adult and Continuing            | Ancient                     | 0289 | Business Administration  |      | Public Administration       | 0617   |

| Agricultural 0517               |                             | 0290 |                          | 0310 | Recreation                  | 0814   |

| Art 0273                        | Linguistics                 | 0291 |                          | 0272 | Social Work                 | 0452   |

| Bilingual and Multicultural     |                             | 0271 |                          | 0770 | Sociology                   |        |

| Business 0688                   | Literature                  | 0401 |                          | 0454 | General                     | 0626   |

| Community College 0275          | General                     | 0294 |                          | 0338 | Criminology and Penalogy    | 0627   |

| Curriculum and Instruction 0727 | Classical                   |      |                          |      | Demography                  | 0938   |

| Early Childhood 0518            | Comparative                 | 0295 |                          | 0385 | Ethnic and Racial Studies   | 0631   |

| Elementar, 0524                 | Medieval                    | 0297 | Economics ,              | 0001 | Individual and Family       |        |

| Finance 0277                    | Modern                      | 0298 |                          | 0501 | Studies                     | 0628   |

| Guidance and Counseling 0519    | African                     | 0316 | Agricultural             | 0503 | Industrial and Labor        |        |

|                                 | American                    | 0591 |                          | 0505 | Relations                   | 0629   |

|                                 | Asian                       | 0305 |                          | 0508 | Public and Social Welfare   | 0630   |

| '''g''''                        | Canadian (English)          | 0352 |                          | 0509 | Social Structure and        | . 0000 |

|                                 | Canadian (French)           | 0355 |                          | 0510 | Development                 | 0700   |

|                                 | English                     | 0593 |                          | 0511 | ا امعدا ا                   | 0344   |

| Industrial 0521                 | Germanic                    | 0311 |                          | 0358 | Transportation              | 0709   |

| Language and Literature 0279    | Latin American              | 0312 |                          | 0366 | Habita and Project Planning | 0999   |

| Mathematics 0280                | Middle Eastern              | 0315 | Gerontology              | 0351 | Urban and Regional Planning | 0453   |

| Music                           | Romance                     | 0313 | History                  |      | Women's Studies             | 0433   |

| Philosophy of                   | Slavic and East European    | 0314 | General                  | 0578 |                             |        |

| Physical                        | and the arm and property    |      |                          |      |                             |        |

| •                               |                             |      |                          |      |                             |        |

#### THE SCIENCES AND ENGINEERING

| BIOLOGICAL SCIENCES                    | Geodesy                                                                                                                                                                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Agriculture                            | Geology 0372                                                                                                                                                              |

| General 047                            |                                                                                                                                                                           |

| Agronomy                               | 35 Hydrology 0388                                                                                                                                                         |

| Animal Culture and                     | Mineralian (141)                                                                                                                                                          |

| Nutration 042                          | 75 Paleobotány 0345                                                                                                                                                       |

| Nutrition                              | 76 Paleoecology 0426                                                                                                                                                      |

|                                        |                                                                                                                                                                           |

| Technology                             | 59 Paleazvology 0985                                                                                                                                                      |

| Foresto, and Wildlife 04               | 78 Palyadory 0427                                                                                                                                                         |

| Plant Culture                          | 59         Paleozoology         0985           78         Palynology         0427           79         Physical Geography         0388           00         00         00 |

| Plant Pathology04                      | 80 Physical Oceanography 0415                                                                                                                                             |

| Plant Physiology                       | 17                                                                                                                                                                        |

| Range Management077                    | HEALTH AND ENVIRONMENTAL                                                                                                                                                  |

| Wood Technology 07                     |                                                                                                                                                                           |

| Biology                                | 2 · · · · · · ·                                                                                                                                                           |

| General 036                            | Environmental Sciences                                                                                                                                                    |

| Anatomy 021                            | = Decim Sciences                                                                                                                                                          |

| Biostatistics 030                      |                                                                                                                                                                           |

|                                        | Audiology                                                                                                                                                                 |

| Botony 030                             | 08 Audiology 0300<br>Chemotherapy 0992                                                                                                                                    |

| Çeli 03                                | ' l'henheim (170)                                                                                                                                                         |

| Ecology                                |                                                                                                                                                                           |

| Entomology 03                          | D3 Harried Management 0760                                                                                                                                                |

| Genetics                               | Human Development 0758                                                                                                                                                    |

| Limnology                              | 7-3 Immunology 0987                                                                                                                                                       |

| Microbiology04                         | Madicine and Surgery IIIA.                                                                                                                                                |

| Molecular 034                          | Y' Mantol Haolth 17327                                                                                                                                                    |

| Neuroscience 03                        | 17 Numina (1549)                                                                                                                                                          |

| Oceanography                           | 10 Number 0570                                                                                                                                                            |

| Physiology04                           | 33 Characan and Grandalam 0380                                                                                                                                            |

| Radiation                              | 61 Occupational Health and                                                                                                                                                |

| Veterinary Science07                   | 78 Thereas 0354                                                                                                                                                           |

| Zoology 04                             | 78 Therapy 0354<br>72 Ophthalmology 0381                                                                                                                                  |

| Biophysics                             | Particles (1971)                                                                                                                                                          |

| General                                | 86 Pathology 0571<br>Phormocology 0419                                                                                                                                    |

| Medical 07                             | 60 Phormacology 0417                                                                                                                                                      |

|                                        | riginocy                                                                                                                                                                  |

| EARTH SCIENCES                         | Physical Therapy                                                                                                                                                          |

| Biogeochemistry                        | 25 Public Health                                                                                                                                                          |

| Geochemistry 00                        | Ca Rediviogy                                                                                                                                                              |

| CCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCCC | Recreation                                                                                                                                                                |

|                                        |                                                                                                                                                                           |

| Speech Pathology Toxicology Home Economics | 0460<br>. 0383<br>. 0386 |

|--------------------------------------------|--------------------------|

| PHYSICAL SCIENCES                          |                          |

| Pure Sciences                              |                          |

| Chemistry                                  |                          |

| Genéral                                    | .0485                    |

| Agricultural                               | . 0749                   |

| Analytical                                 | .0486                    |

| Biochemistry                               | 0487                     |

| Inorganic                                  | . 0488                   |

| Nuclear                                    | 0738                     |

| Organic                                    | 0490                     |

| Pharmoceutical                             |                          |

| Physical                                   |                          |

| Polymer                                    | 0495                     |

| Radiation                                  | 0754                     |

| Mathematics                                | . 0405                   |

| Physics                                    |                          |

| General                                    | 0605                     |

| Acoustics                                  | 0986                     |

| Astronomy and                              |                          |

| Astrophysics                               | ,0606                    |

| Atmospheric Science                        | 0608                     |

| Atomic                                     | 0748                     |

| Atomic                                     | 0607                     |

| Elementory Porticles and                   |                          |

| High Energy<br>Fluid and Plasma            | 0798                     |

| Fluid and Plasma                           | 0759                     |

| Molecular                                  | 0609                     |

| Nuclear                                    | 0610                     |

| Optics                                     | 0752                     |

| Rodiation                                  | 0756                     |

| Solid State                                | 0611                     |

| Statistics                                 | 0463                     |

| Applied Sciences                           |                          |

| Applied Mechanics                          | 0344                     |

| Computer Science                           | 0004                     |

| Composer science                           | 0704                     |

|                                            |                          |

| Engineering General Aerospoce Agricultural Automotive Biomedical Chemical Civil Electronics and Electrical Heat and Thermodynamics Hydraulic Industrial Marine Materials Science Mechanical Metallurgy Mining Nuclear Packaging Petroleum Sanitary and Municipal System Science Geotechnology Operations Research Plastics Technology Textile Technology | 0538<br>0539<br>0540<br>0541<br>0542<br>0543<br>0548<br>0545<br>0546<br>0547<br>0794<br>0551<br>0552<br>0552<br>0552<br>0554<br>0795<br>0795<br>0795 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| General                                                                                                                                                                                                                                                                                                                                                  | 0621                                                                                                                                                 |

| Behavioral                                                                                                                                                                                                                                                                                                                                               | 0622                                                                                                                                                 |

| Developmental                                                                                                                                                                                                                                                                                                                                            | 0620                                                                                                                                                 |

| Experimental                                                                                                                                                                                                                                                                                                                                             | 0624                                                                                                                                                 |

| Personality                                                                                                                                                                                                                                                                                                                                              | 0625                                                                                                                                                 |

| Physiological                                                                                                                                                                                                                                                                                                                                            | 0989                                                                                                                                                 |

| Psychobiology<br>Psychometrics                                                                                                                                                                                                                                                                                                                           | 0632                                                                                                                                                 |

| Social                                                                                                                                                                                                                                                                                                                                                   | 0451                                                                                                                                                 |

All Rights Reserved. No part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author.

#### **Abstract**

This work provides a treatment of BiCMOS technology from several perspectives. The manner in which the modern BiCMOS process evolved from a predominantly CMOS processing base is discussed, and a survey of special processing technologies is given. Without these advanced techniques the current level of BiCMOS and CMOS process performance would be unattainable. Examples of such include trench isolation, lightly doped drain structures, and advanced metallization techniques. Additionally, BATMOS, Northern Telecom's BiCMOS process technology is described in detail. Issues pertaining to BiCMOS process scalability, device scalability, and process tradeoffs are discussed. Included are such topics as active device scaling, second order effects which become important in scaled technologies, BiCMOS process tradeoffs, and latchup in BiCMOS. Several high performance arithmetic architectures were implemented in the form of macrocells, and their design is discussed. Toward that end, a survey of hardware multipliers is given, concentrating on the parallel types, and two new recently proposed architectures are described which form the basis for five of the six macrocells. As well, the implementation of a fast adder macrocell is treated. Some details of the design process of these macrocells are also highlighted. The use of BiCMOS in the realization of dynamic, massively pipelined arithmetic structures is explored. A review of pipelining strategies is briefly given, followed by a description of the true single phase clocking (TSPC) technique. Factors effecting the implementation of NMOS transistor switching trees in BATMOS is investigated, and key simulation results are reported. A new latching principle is described which is based on a current steering concept. Several new latch structures based on this principle are described and simulation results from test structures are presented. The performance of these new structures is compared to the TSPC technique. and simulation results of both latching arrangements used with a synthesized switching tree based mod 7 multiplier are presented. Finally, an ultra fast latching structure is introduced, simulation results are presented, and some additional discussion is given.

Dedicated with love to my family.

### Acknowledgments

The support and guidance offered by G. A. Jullien was invaluable in the successful completion of this thesis. His knowledge and enthusiasm provided a source of inspiration, and many of the ideas contained in this work were precipitated from informative discussions with him. W. C. Miller also gave insightful comments and observations which provided important direction for this work. S. Bandyopadhyay is recognized as having served a valuable supervisory role on my committee. Always willing to offer his time, Zhongde Wang provided extensive input in the area of hardware multipliers. Additionally, my family has been a constant source of strength, support, and encouragement which has allowed me to persevere through the difficult times. Finally, my friends are acknowledged for their understanding and patience. Micronet provided funding for a portion of this work.

# Table of Contents

| Chap | oter 1                                    | 1    |

|------|-------------------------------------------|------|

| INTR | ODUCTION                                  | 1    |

| 1.1  | Introduction                              | i    |

| 1.2  | Thesis Objectives                         | 2    |

| 1.2  | Thesis Organization                       |      |

|      | oter 2                                    | 4    |

| -    | CESS TECHNOLOGY                           | 4    |

|      |                                           | 4    |

| 2.1  | Introduction                              |      |

| 2.2  | Silicon and Process Basics                | 4    |

| 2.3  | Typical CMOS Process Flow                 | 7    |

| 2.4  | Evolution of the BiCMOS Process Flow      | 9    |

| 2.5  | Advanced Processing Techniques            | . 13 |

|      | 2.5.1 Epitaxy                             | . 13 |

|      | 2.5.2 Buried Layers                       |      |

|      | 2.5.3 Lightly Doped Drain (LDD)           | . 14 |

|      | 2.5.4 Polysilicon Emitters                |      |

|      | 2.5.5 Silicidation                        | . 16 |

|      | 2.5.6 Local Interconnect (LI)             | 17   |

|      | 2.5.7 Local Oxidation of Silicon (LOCOS)  | 18   |

|      | 2.5.8 Trench Isolation                    |      |

|      | 2.5.9 Metallization and Planarization     | 22   |

| 2.6  | BATMOS: Northern Telecom's BiCMOS Process | 23   |

|      | 2.6.1 Introduction                        | 23   |

|      | 2 6 2 Process Synopsis                    | 23   |

|      | 2.6.3 Detailed Process Description        | 24   |

| 2.7  | Summary                                   |      |

| Chap | iter 3           |                                            | 29 |

|------|------------------|--------------------------------------------|----|

| SCAL | ING. DEVICE      | E, AND PROCESS CONSIDERATIONS              | 29 |

| 3.1  | Introduction.    |                                            | 29 |

| 3.2  | Scaling of Activ | ve Devices                                 | 30 |

| 3.3  | Active Devi      | ce Issues                                  | 37 |

|      | 3.3.1 MOS D      | Device Issues                              | 38 |

|      | 3.3.1.1          | Channel Length Modulation                  | 38 |

|      | 3.3.1.2          | Threshold Voltage                          | 38 |

|      | 3.3.1.3          | Subthreshold Current                       | 41 |

|      | 3.3.1.4          | Velocity Saturation                        | 43 |

|      | 3.3.1.5          | Mobility Degradation                       | 44 |

|      | 3.3.1.6          | Effect of Very Thin Gate Oxide             | 44 |

|      | 3.3.1.7          | 7 Source and Drain Resistance              | 45 |

|      | 3.3.1.8          | Drain Induced Barrier Lowering (DIBL)      | 46 |

|      | 3.3.1.9          | 9 Hot Carrier Effects                      | 47 |

|      | 3.3.2 Bipola     | r Device Issues                            | 48 |

|      | 3.3.2.           | 1 Extrinsic and Intrinsic Device           | 49 |

|      | 3.3.2.           | 2 Conductivity Modulation (Webster Effect) | 50 |

|      | 3.3.2.           | Base Pushout (Kirk Effect)                 | 51 |

|      | 3.3.2.           | 4 Base width Modulation (Early Effect)     | 51 |

|      | 3.3.2.           | 5 Current Gain                             | 52 |

|      | 3.3.2.           | 6 Punchthrough                             | 52 |

|      | 3.3.2.           | 7 Reachthrough                             | 53 |

|      | 3.3.2.           |                                            |    |

|      | 3.3.2.           | 9 Polysilicon Emitters                     | 55 |

|      | 3.3.2.           | 10 Parasitic Resistances                   | 56 |

| 3.4  | Bipolar and      | CMOS Devices in a BiCMOS Process           | 58 |

| 3.5  | Latchup          |                                            | 60 |

| 3.6  | Summary          |                                            | 67 |

| Cha  | apter 4          |                                            | 69 |

| HIG  | H PERFORM        | IANCE ARITHMETIC CELLS                     | 69 |

| 4.1  | Introductio      | n                                          | 69 |

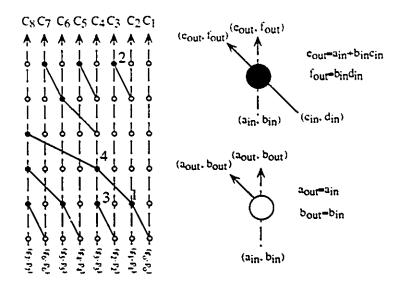

| 4.2 | Multipliers                                           | 70  |

|-----|-------------------------------------------------------|-----|

| 4.3 | Macrocells                                            | 83  |

|     | 4.3.1 Two Bit Full Adder Multiplier                   | 83  |

|     | 4.3.2 Column Compression Multiplier                   |     |

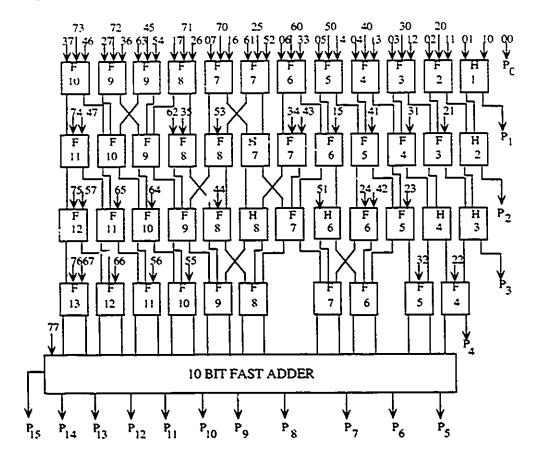

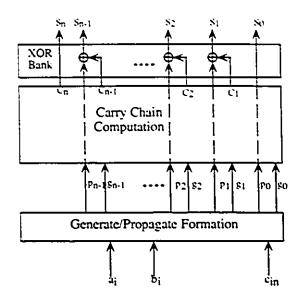

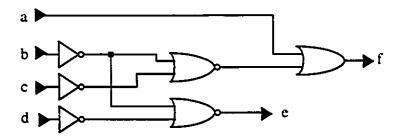

|     | 4.3.3 High Performance Adder                          | 87  |

| 4.4 | Additional Discussion of Work Completed               | 91  |

| 4.5 | Summary                                               | 95  |

| Cha | pter 5                                                | 96  |

| CLO | CKING STRATEGIES FOR PIPELINED ARITHMETIC             |     |

| STR | UCTURES                                               | 96  |

| 5.1 | Introduction                                          | 96  |

| 5.2 | Pipeline Clocking and Circuit Techniques              | 96  |

| 5.3 | True Single Phase Clocking (TSPC)                     | 98  |

| 5.4 | NMOS Trees In BATMOS                                  | 103 |

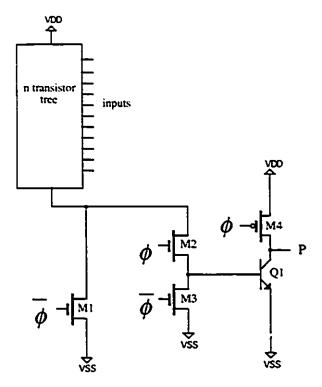

| 5.5 | BiCMOS in Dynamic Circuits                            | 108 |

| 5.6 | Current Steering (CS) Latch                           | 109 |

|     | 5.6.1 Simulation of Current Steering Latch Structures | 115 |

|     | 5.6.2 Ultra Fast Current Steering Latch Structure     | 122 |

| 5.7 | Additional Discussion                                 | 123 |

| 5.8 | Summary                                               | 128 |

| Cha | pter 6                                                | 130 |

| CON | CLUSIONS AND SUGGESTIONS FOR FUTURE WORK              | 130 |

| 6.1 | Conclusions                                           | 130 |

| 6.2 | Future Work                                           | 132 |

| Ref | erences                                               | 134 |

| App | pendix A                                              | 146 |

| EDC | GE™ BICMOS ENVIRONMENT HINTS                          | 140 |

| A 1 | Introduction                                          | 147 |

| A | 2 Lis* of Hints                         | 147 |

|---|-----------------------------------------|-----|

| A | Appendix B                              | 150 |

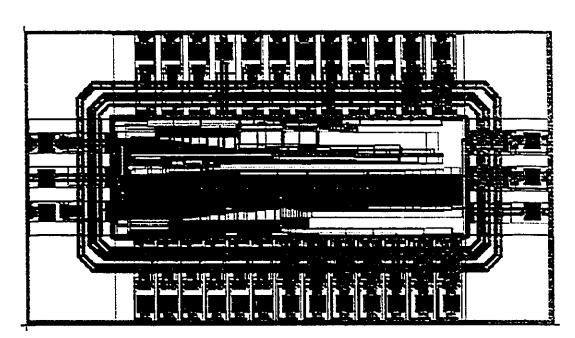

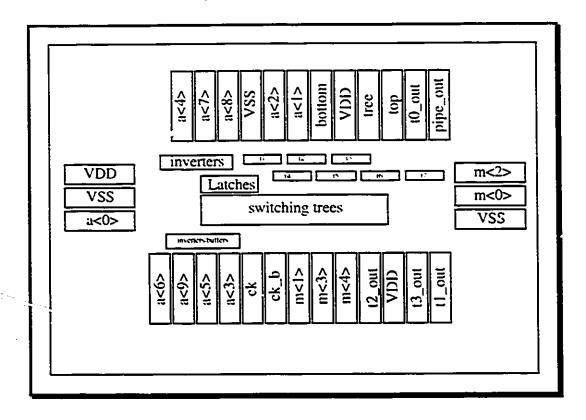

| N | IACROCELL LAYOUTS                       | 150 |

| В | .l Introduction                         | 151 |

| В | Macrocells Implemented in Pure CMOS     | 151 |

| В | 3.3 Macrocells Implemented in BiCMOS    | 154 |

| В | 3.4 Macrocell Implemented in ECL        | 156 |

| A | Appendix C                              | 157 |

| N | MACROCELL SPECIFIC DETAILS              | 157 |

| C | C.1 Introduction                        | 158 |

| C | C.2 Macrocells Implemented in Pure CMOS | 159 |

| C | C.3 Macrocells Implemented in BiCMOS    | 160 |

| C | C.4 Macrocell Implemented in ECL        | 161 |

| Ā | Appendix D                              | 162 |

| I | Email                                   | 162 |

| A | Appendix E                              | 164 |

| I | PROGRAMS                                | 164 |

| F | E.1 Introduction                        | 165 |

| I | E.2 Removal of Extraneous pins          | 165 |

| I | E.3 Conversion of CMOS4S to BATMOS      | 166 |

| H | E.4 Sample STL file                     | 171 |

| ı | Appendix F                              | 173 |

| I | MULTIPLIER CHIP                         | 173 |

| ] | F.1 Summary and Pinout                  | 174 |

|   | Appendix G                              | 176 |

|   | MOD 17 CHIP                             | 176 |

| ( | G. I. Summary and Pinout                | 177 |

Vita Auctoris 180

# List of Figures

| Figure 2.1: P Well CMOS Process Cross-section                               | 8  |

|-----------------------------------------------------------------------------|----|

| Figure 2.2: Low End BiCMOS Process                                          | 9  |

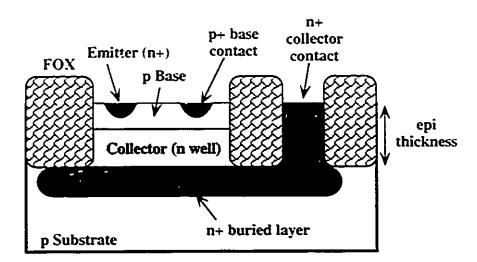

| Figure 2.3: BiCMOS Process With Buried Layers and Deep Collector Contact    | 10 |

| Figure 2.4: BiCMOS Process With Self Aligned Buried Layers and Poly Emitter | 11 |

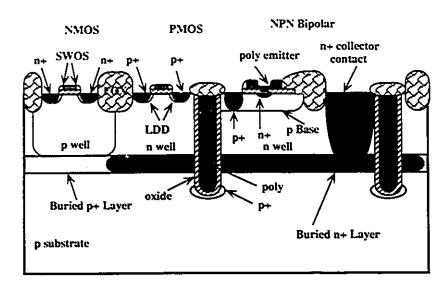

| Figure 2.5: High Performance BiCMOS process Cross-section                   | 13 |

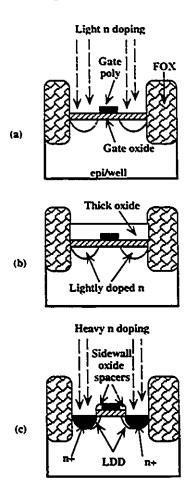

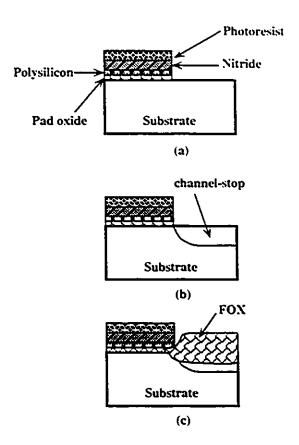

| Figure 2.6: Steps in Forming LDD Structures                                 | 15 |

| Figure 2.7: Poly Emitter and Poly Contacted Emitter Formation               | 16 |

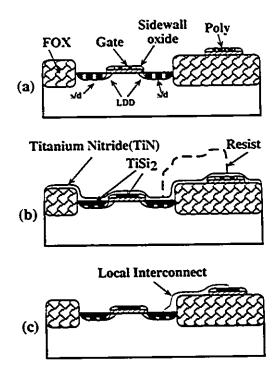

| Figure 2.8: Process Steps In Forming LI                                     | 17 |

| Figure 2.9: Inverter Connections Implemented with LI                        | 18 |

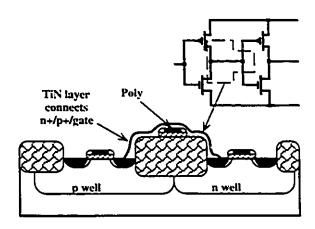

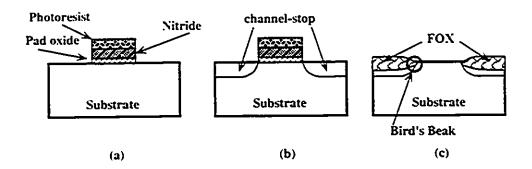

| Figure 2.10: Simple LOCOS Isolation Structure Formation                     | 19 |

| Figure 2.11: Poly Buffer LOCOS Isolation Structure Formation                | 20 |

| Figure 2.12: Example of Bipolar process with LOCOS Isolation                | 21 |

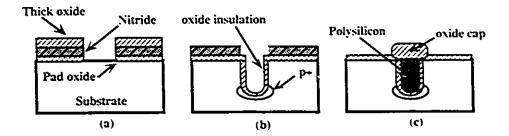

| Figure 2.13: Process Steps For Trench Isolation Structure                   | 22 |

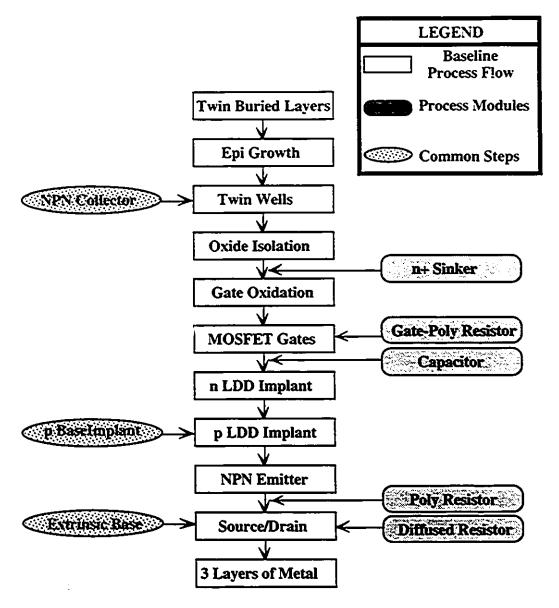

| Figure 2.14: Flow Chart Showing Major Processing Steps                      | 25 |

| Figure 3.1: Illustration of Channel Length Modulation                       | 39 |

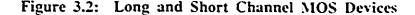

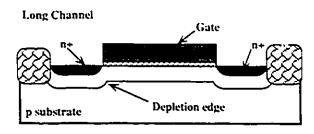

| Figure 3.2: Long and Short Channel MOS Devices                              | 40 |

| Figure 3.3: Conceptual Illustration of Charge in a Short Channel Device     | 41 |

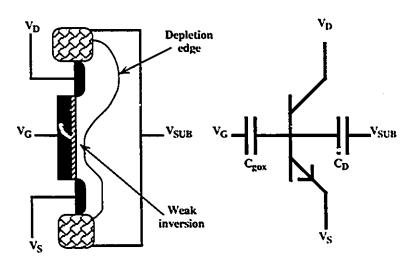

| Figure 3.4: Weakly Inverted MOSFET—Bipolar Analogy                          | 42 |

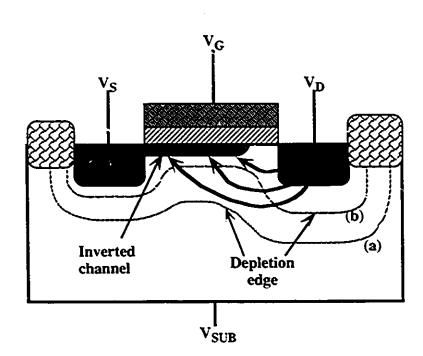

| Figure 3.5: Mechanism for Drain Induced Barrier Lowering                    | 47 |

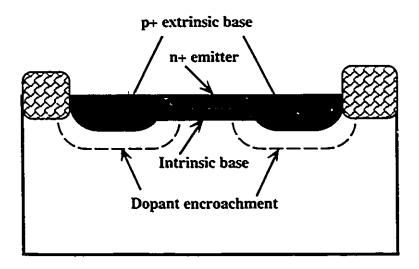

| Figure 3.6: Intrinsic Base Region With Extrinsic Base Dopant Encroachment   | 49 |

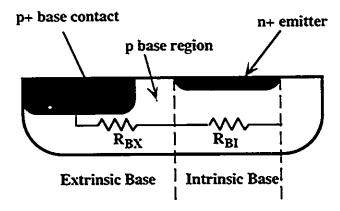

| Figure 3.7: Concept of Intrinsic and Extrinsic Base Resistance              | 57 |

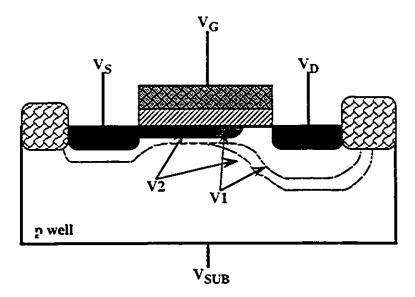

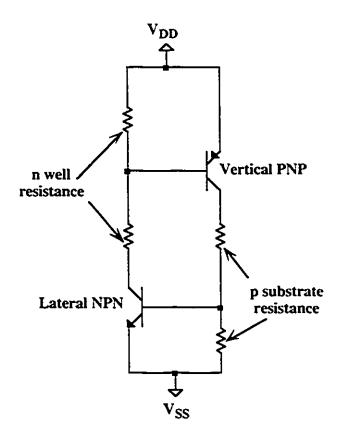

| Figure 3.8: Latchup in an N Well CMOS Process                               | 6  |

| Figure 3.9: Lumped Element Model For Latchup                                | 62 |

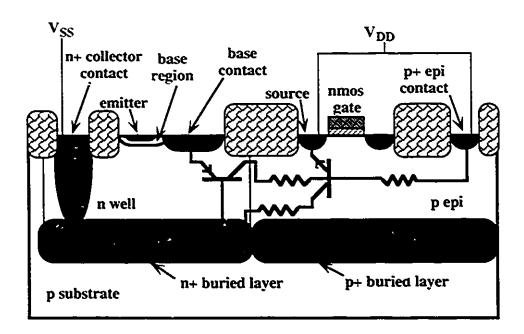

| Figure 3.10: Latchup in an Advanced BiCMOS Technology                       | 63 |

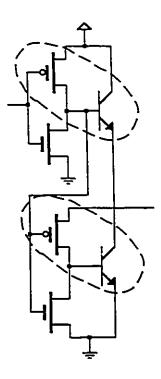

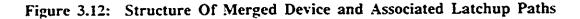

| Figure 3.11: Merged Devices in a BiCMOS Buffer                        | 64  |

|-----------------------------------------------------------------------|-----|

| Figure 3.12: Structure Of Merged Device and Associated Latchup Paths  | 65  |

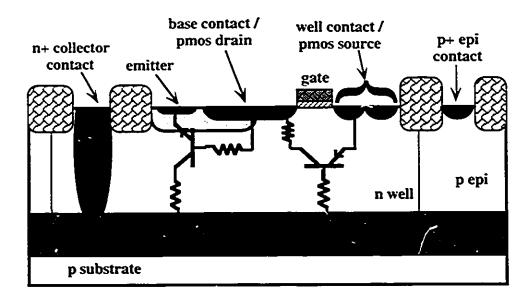

| Figure 3.13: Well Structures In Advanced BiCMOS Processes             | 66  |

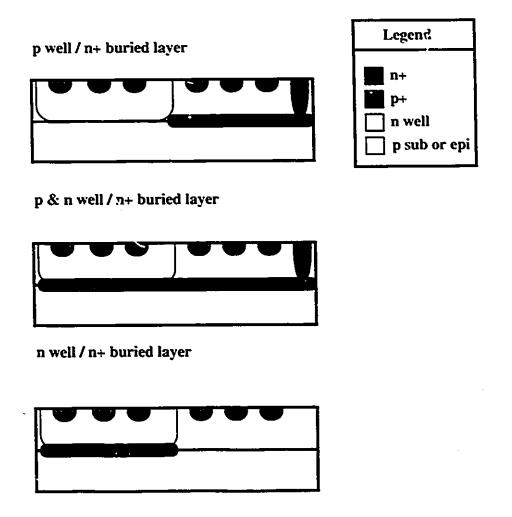

| Figure 4.1: The multiplication process                                | 70  |

| Figure 4.2: Simple Array Multiplier                                   | 71  |

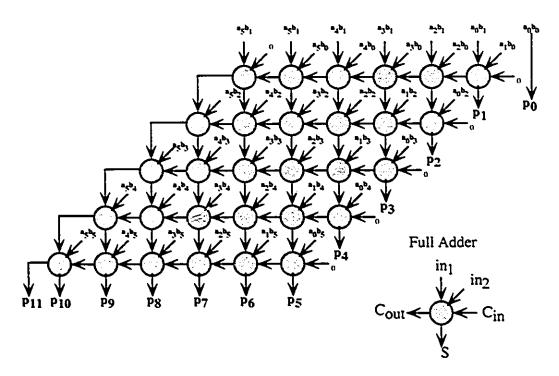

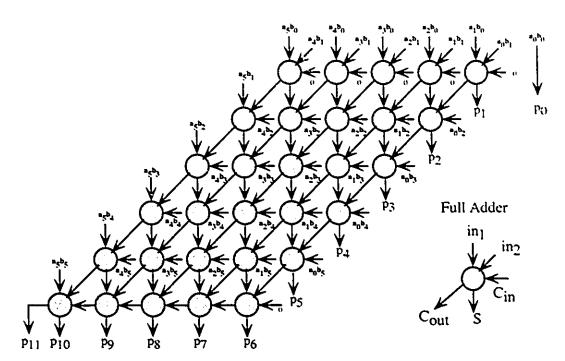

| Figure 4.3: CSA Array Multiplier                                      | 72  |

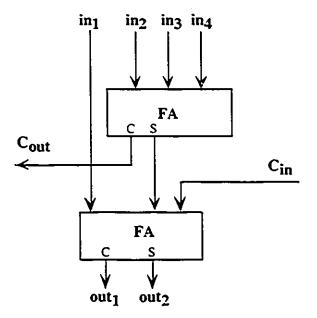

| Figure 4.4: A (4:2) Compressor                                        | 74  |

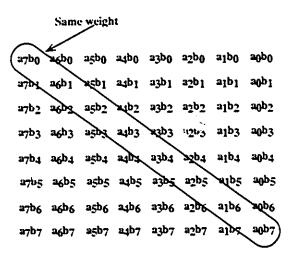

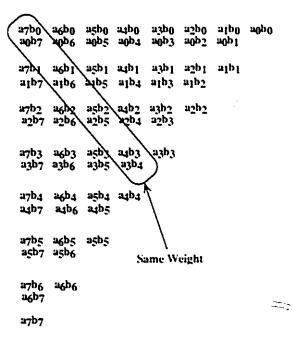

| Figure 4.5: Square Partial Product Array                              | 75  |

| Figure 4.6: Folded Partial Product Array                              | 76  |

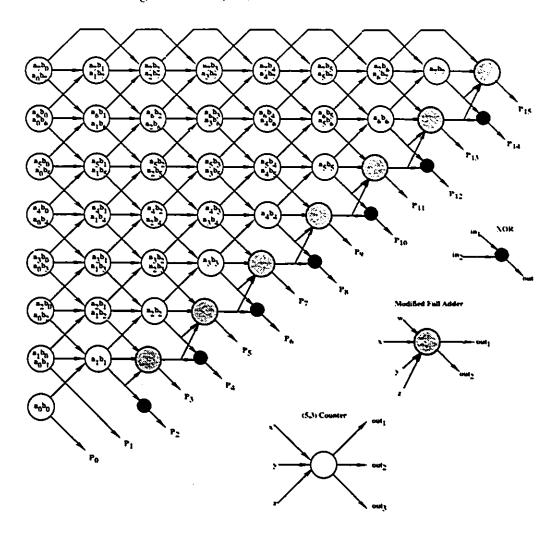

| Figure 4.7: (5.3) Counter Architecture                                | 77  |

| Figure 4.8: Comparison of Several Multiplication Algorithms           | 81  |

| Figure 4.9: Wang's Linear Parallel Multiplier Architecture            | 84  |

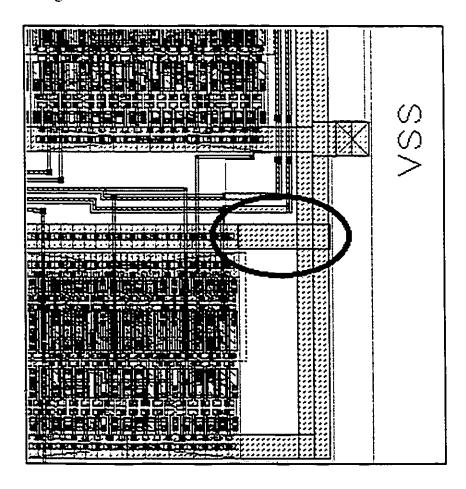

| Figure 4.10: Layout of Wang's Linear Parallel Multiplier              | 85  |

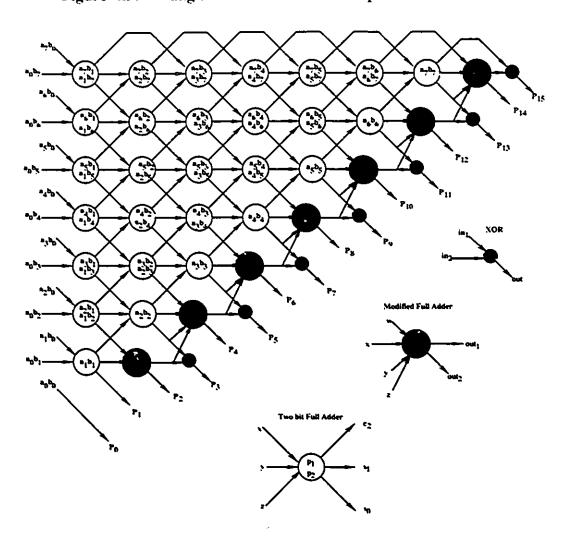

| Figure 4.11: Wang's Column Compression Multiplier Architecture        | 86  |

| Figure 4.12: Layout of Wang's Column Compression Multiplier           | 87  |

| Figure 4.13: Tree Nature of Function Computation                      | 90  |

| Figure 4.14: Block Diagram of Adder                                   | 91  |

| Figure 4.15: Special Bit Processor Circuit                            | 91  |

| Figure 4.16: Layout of High Performance Adder                         | 92  |

| Figure 4.17: The Manual Connection of a Cell Row                      | 93  |

| Figure 4.18: Multiplier Chip Submitted for Fabrication                | 94  |

| Figure 5.1: Pipeline Concept                                          | 97  |

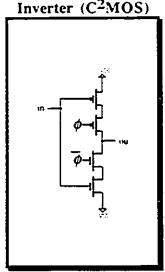

| Figure 5.2: Clocked Inverter (C2MOS)                                  | 98  |

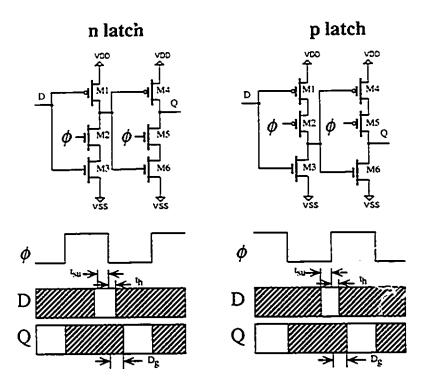

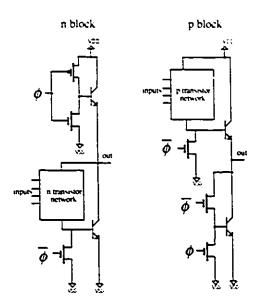

| Figure 5.3: N-C2MOS and P-C2MOS Latch structures                      | 100 |

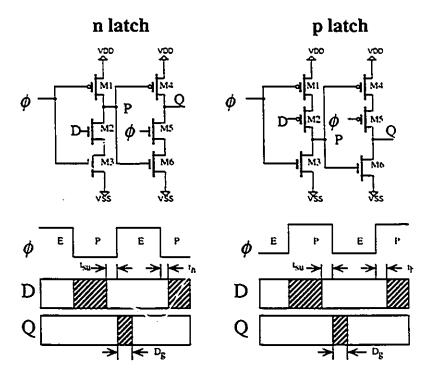

| Figure 5.4: TSPC Precharged n and p Latch structures                  | 101 |

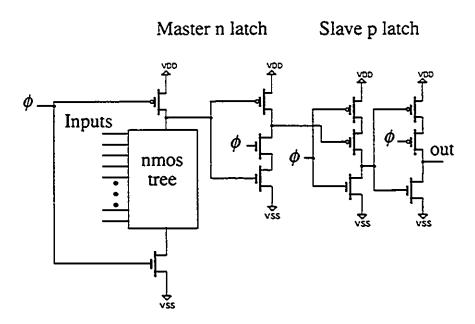

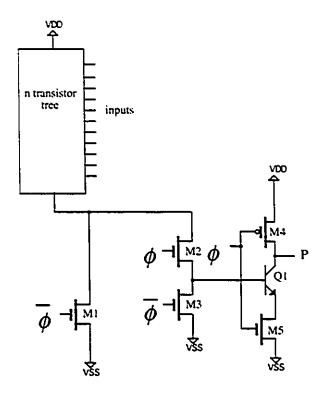

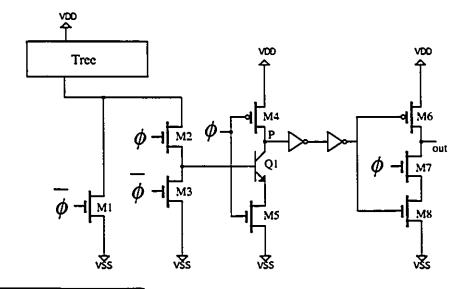

| Figure 5.5: Switching Tree embedded in a Master—Slave Latch           | 102 |

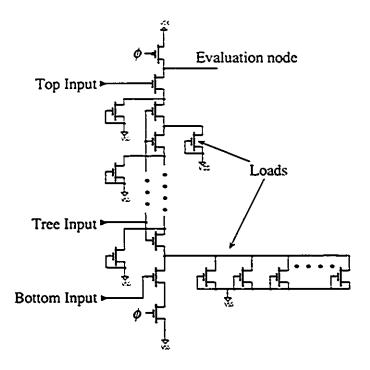

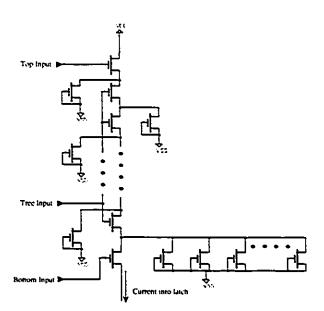

| Figure 5.6: Test Structure For Switching Trees Embedded in TSPC Latch | 104 |

).)

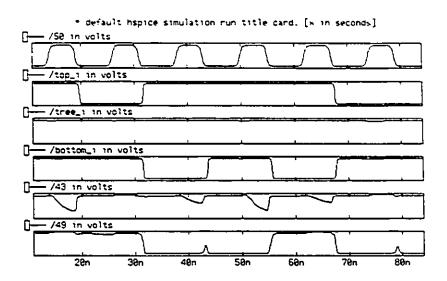

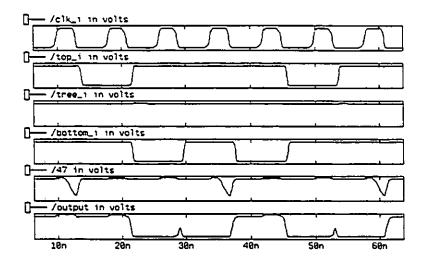

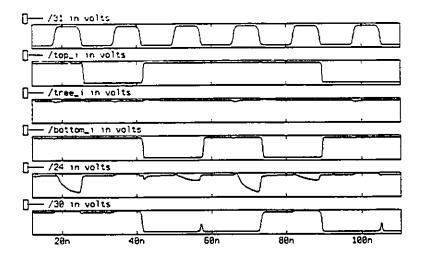

| Figure 5.7: 16 High, Bottom Loaded Test Structure at 83 MHz                    | 105 |

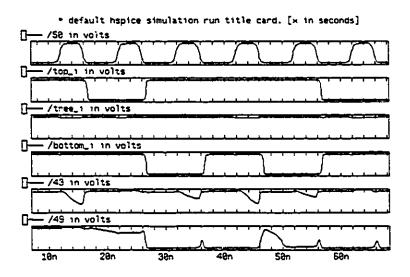

|--------------------------------------------------------------------------------|-----|

| Figure 5.8: 16 High, Bottom Loaded Test Structure at 100 MHz                   | 105 |

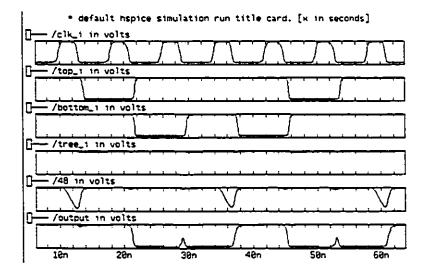

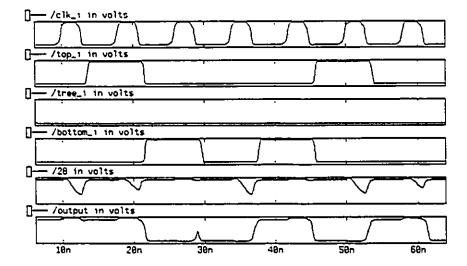

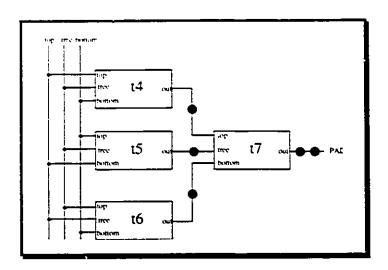

| Figure 5.9: Mod 7 multiplier at 100 MHz                                        | 107 |

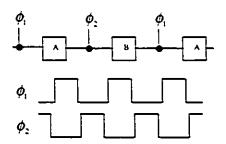

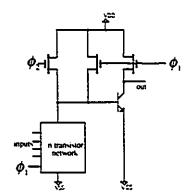

| Figure 5.10: Two Phase Dynamic Circuit                                         | 108 |

| Figure 5.11: Example of Kuo's Circuits                                         | 109 |

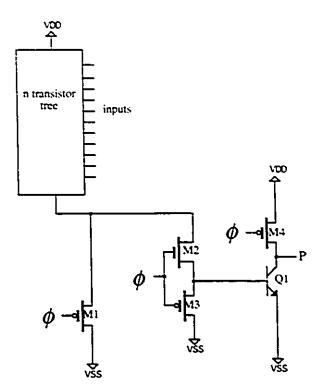

| Figure 5.12: Current Steering Concept                                          | 110 |

| Figure 5.13: Revised Current Steering Circuit                                  | 113 |

| Figure 5.14: DICS n Latch                                                      | 113 |

| Figure 5.15: DSCS n Latch                                                      | 114 |

| Figure 5.16: CDCS n Latch                                                      | 115 |

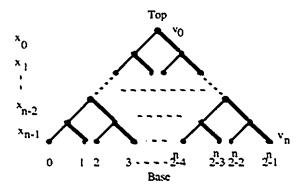

| Figure 5.17: A Binary Tree                                                     | 116 |

| Figure 5.18: Test Structure For New Latch                                      | 117 |

| Figure 5.19: Failure Mode Unique to Initial Version of New Latch               | 118 |

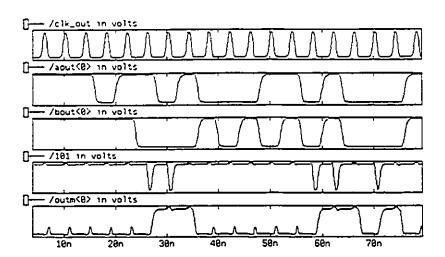

| Figure 5.20: CDCS n Latch At 125 MHz                                           | 119 |

| Figure 5.21: Mod 7 Multiplier at 200 MHz                                       | 120 |

| Figure 5.22: Mod 17 Multiplier Chip                                            | 121 |

| Figure 5.23: Modified PE Section                                               | 122 |

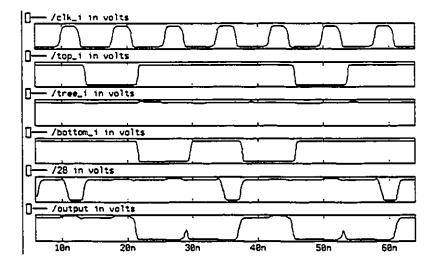

| Figure 5.24: Test Structure at 125 MHz                                         | 123 |

| Figure 5.25: Mod 7 Multiplier at 250 MHz                                       | 124 |

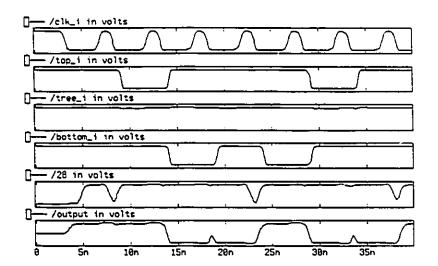

| Figure 5.26: UCDCS Test Structure With Large Transistors at 125 MHz            | 124 |

| Figure 5.27: UCDCS Test Structure With Large Transistors at 200 MHz            | 125 |

| Figure 5.28: TSPC Test Structure With Large Transistors at 83 MHz              | 126 |

| Figure 5.29: Latch With PMOS Chain                                             | 126 |

| Figure 6.1: Suggestion For TSPC Version of Current Steering Latch.             | 133 |

| Figure B.1: Dadda Style Multiplier (dadda_top)                                 | 151 |

| Figure B.2: Two Bit Full Adder Multiplier Using Full Adder Cells (tbfa_fa_top) | 152 |

| Figure B.3: Two Bit Full Adder Multiplier Using Simple Gates (tbfa_g_top)      | 153 |

| Figure B.4: | Dadda Style Multiplier (dadda_top_bic)                            | 154 |

|-------------|-------------------------------------------------------------------|-----|

| Figure B.5: | Two Bit Full Adder Multiplier Using Simple Gates (tbfa_g_bic_top) | 155 |

| Figure B.6: | Fast Adder (adder_top)                                            | 156 |

| Figure F.1: | Pinout Diagram                                                    | 174 |

| Figure G.1: | Pinout Diagram                                                    | 177 |

| Figure G.2: | Simulated Pipeline                                                | 179 |

# List of Symbols

| ß                                                 | effective current gain of bipolar transistor |

|---------------------------------------------------|----------------------------------------------|

| $\boldsymbol{\beta}_{j}$                          | peak common emitter current gain             |

| $\Delta V$                                        | voltage change                               |

| $\mathcal{E}_{ox}$                                | relative permittivity of silicon dioxide     |

| $\boldsymbol{\varepsilon}_{\scriptscriptstyle v}$ | relative permittivity of silicon             |

| $\mathcal{E}_{o}$                                 | permittivity of free space                   |

| $\phi_{\varsigma}$                                | surface potential                            |

| κ                                                 | figure of merit for MOS devices              |

| μ                                                 | mobility                                     |

| $\mu_n$                                           | electron mobility                            |

| $\rho_i$                                          | number of partial product rows per stage     |

| ν                                                 | velocity                                     |

| V.,                                               | saturation velocity                          |

| $BV_{CBO}$                                        | collector—base breakdown voltage             |

| $BV_{CEO}$                                        | collector—emitter breakdown voltage          |

| $C_{L}$                                           | load capacitance                             |

| $C_{gox}$                                         | gate oxide capacitance per unit area         |

| $C_{_{\!\scriptscriptstyle \mathcal{R}}}$         | gate capacitance                             |

| $C_{inv}$                                         | inversion layer capacitance                  |

| $C_{D}$                                           | depletion capacitance                        |

| $D_{_{\mathcal{R}}}$                              | latch delay                                  |

| $D_{nb}$                                          | diffusion constant for electrons in base     |

| $D_{pe}$                                          | diffusion constant for holes in emitter      |

| E                                                 | electric field                               |

| $E_{br}$                                          | avalanche critical field                     |

| $f_{T}$                                           | cut-off frequency                            |

| g <sub>m</sub>                                    | transconductance                             |

| in <sub>ij</sub>                                  | inputs to a counter                          |

| $I_{c}$                                           | collector current                            |

| $I_{DS}$                                          | drain current                                |

| $I_{avg}$                                         | average current                              |

|                                                   |                                              |

K number of stages in partial product reduction array k scaling factor scaling factor k,  $k_{\gamma}$ scaling factor horizontal scale factor k, vertical scale factor  $k_{c}$ voltage scale factor k, • B Boltzman constant diffusion length of holes in emitter  $L_{\kappa}$ MOSFET channel length L collector doping concentration  $N_c$ emitter doping concentration  $N_E$ substrate doping  $N_{SUB}$  $N_R$ peak base doping q charge  $Q_n$ inversion charge base Gummel number  $Q_{B}$ emitter resistance  $R_{\scriptscriptstyle F}$ output resistance r" collector resistance  $R_{c}$ base resistance  $R_R$ S subthreshold swing T temperature  $T_{D}$ circuit delay gate oxide thickness  $I_{\rm gen}$  $l_h$ hold time 1,,, setup time  $V_{CE}$ voltage between collector and emitter  $V_{DD}$ + supply voltage drain to source voltage  $V_{DS}$  $V_{GS}$ gate voltage with respect to the source  $V_{pt}$ punchthrough voltage  $V_{rr}$ reachthrough voltage  $V_{\rm ec}$ - supply voltage  $V_r$ MOS threshold voltage

NMOS threshold voltage

$V_{TN}$

| $V_{TP}$             | PMOS threshold voltage |

|----------------------|------------------------|

| $W_{C}$              | collector width        |

| $W_{_{\mathcal{B}}}$ | base width             |

| W                    | MOSFET channel width   |

| $W_{\mathcal{E}}$    | emitter width          |

| $X_{j}$              | junction depth         |

# Chapter 1

#### INTRODUCTION

#### 1.1 Introduction

BiCMOS technology constitutes a marriage of CMOS and bipolar technologies. Both types of devices are available on the same wafer, which means that the advantages of both may be reaped at the expense of extra process complexity. CMOS devices offer low power dissipation, wide noise margins, and a very high packing density. Bipolar junction transistors (BJTs) offer high switching speed, high current density per unit area, and flexible I/O levels. Since the mid 1970s, CMOS has been the mainstream semiconductor technology chiefly because of its packing density, and power dissipation. Bipolar technologies were usually used for small but fast system subcircuits, and they had to be manufactured on separate substrates. In a BiCMOS process, both CMOS and bipolar devices are available on the same chip, thus affording the option of using both devices simultaneously in an integrated design.

BiCMOS fills a market gap between very dense, medium speed CMOS chips, and bipolar ECL integrated circuits with high power consumption. It no longer is a niche technology, however, since its utility has been recognized on a broad scale. It has been used in the implementation of gate arrays [1], static RAMs (SRAMs) [2], dynamic RAMs (DRAMs) [3], and complex subsystems such as a phase locked loop clock generator [4]. The Pentium® microprocessor from Intel, and the Super Sparc® RISC processor from Sun Micro-systems/Texas Instruments are both examples of microprocessors which have been implemented with BiCMOS technology [5]. Usually BiCMOS designs are predominantly CMOS based, and the bipolar devices are used only where their qualities are most useful. Common applications for the Bipolar devices include gates with high drive for high capacitance nodes [6], which exploit the device's high transconductance, and sense amps in memory chips [3], which exploit their superior analog qualities. Misuse of the bipolar devices can lead to unnecessarily large designs and compromised performance [7]. The

former is due to the additional space occupied by bipolar transistors while the latter is due to the fact that a CMOS gate can switch faster under light loads than a BiCMOS gate<sup>1</sup>.

# 1.2 Thesis Objectives

This thesis work has three main objectives. The first is to provide a survey of current BiCMOS processing techniques and methodologies, as well as process considerations which determine device behaviour. The second involves the design and characterization of several high performance arithmetic macrocells<sup>2</sup>. The third objective is to investigate the application of BiCMOS technology in the realization of massively pipelined arithmetic structures.

### 1.2 Thesis Organization

This work is organized into six chapters. The first chapter comprises this introduction, while the second describes BiCMOS processing techniques and methodologies. The manner in which the modern BiCMOS process evolved from a predominantly CMOS processing base is discussed. Special processing technologies are described which are used to form structures without which the current level of BiCMOS and CMOS process performance would be unattainable. Examples include trench isolation, lightly doped drain (LDD) structures, and advanced metallization techniques. Finally, BATMOS, Northern Telecom's BiCMOS process technology, is described in detail.

The third chapter delves into issues pertaining to BiCMOS process scalability, device scalability, and process tradeoffs. A brief description of classical scaling of MOS devices is given, followed by a summary of other scaling methods for MOS and bipolar devices. Many second order effects become prominent performance limiting factors when feature sizes shrink, and some of these factors are discussed for both MOS and bipolar devices. Due to the presence of both device types in BiCMOS, many process tradeoffs must be made, and the main ones are discussed. Finally, a treatment of latchup is given, including a short review of latchup in CMOS, as well as a discussion of new modes which can only occur in a BiCMOS process.

<sup>1</sup> This statement is based on a conventional totem-pole style gate [8].

<sup>&</sup>lt;sup>2</sup> This work was funded under a contract with the Canadian Microelectronics Corporation, and the Micronet Network of Centres of Excellence (with four member universities).

The fourth chapter deals with the design and characterization of several high performance arithmetic macrocells. A survey of hardware multipliers is given, concentrating on the parallel types. Booth encoding is briefly explained, and two new recently proposed architectures are described. The implementation of these architectures in the form of macrocells is discussed, as well as the implementation of a fast adder macrocell. Some details of the design process of these macrocells are also described.

Chapter five investigates the use of BiCMOS in the realization of pipelined arithmetic structures. A review of pipelining strategies is briefly given, followed by a description of the true single phase clocking (TSPC) technique. Factors effecting the implementation of NMOS transistor switching trees in BATMOS is investigated, and key simulation results are presented. A new latching principle is described which is based on a current steering concept. Several new structures based on this principle are described and simulation results are presented. The performance of these new structures is compared to the TSPC technique, and simulation results of both latching arrangements used with a synthesized switching tree based mod 7 multiplier are presented. Finally, an ultra fast latching structure is introduced, simulation results are presented, and some additional discussion is given.

The final chapter summarizes this work including pertinent results, and also offers suggestions for future work.

# Chapter 2

### PROCESS TECHNOLOGY

#### 2.1 Introduction

BiCMOS is the name given to semiconductor fabrication technologies which are designed to include both CMOS and bipolar devices on the same die. Usually the process is optimized for performance, cost, or analog compatibility but, unfortunately, the paths to these ends usually diverge. A process which has been optimized for speed is usually characterized by small feature size (< 1 µm in 1993), thin gate oxide, the presence of an epitaxial layer, 2 or 3 layers of low resistance interconnect and advanced isolation techniques. In cost optimized processes, a reduced number of mask levels, and no epitaxial layer yield a simpler fabrication process at the cost of compromised device performance. An analog process will have less aggressive design rules, a thick epitaxial layer and oxide layers, and may be designed for higher operating voltages ( 10V to 15V). It is important to realize that the development of BiCMOS technology has been driven from a CMOS processing base, which explains why low end BiCMOS processes may have, in total, only one or two additional mask levels when compared to the CMOS parent process. In this chapter, typical CMOS fabrication techniques and practices are examined briefly, and then successive process changes are described to illustrate the evolution of a high performance BiCMOS technology from the basic CMOS process flow. Advanced processing techniques will be covered, and BATMOS, Northern Telecom's BiCMOS process, will be discussed.

### 2.2 Silicon and Process Basics

The electrical conductivity of silicon is between that of an insulator and that of a conductor, which is why it is called a semiconductor. Through a process called doping, impurities are purposely introduced into the crystal lattice structure of the silicon which alter its electrical

behaviour. A typical substrate doping<sup>1</sup> concentration is approximately 10<sup>15</sup> atoms/cm<sup>3</sup>. while the particle density of silicon is on the order of  $10^{22}$  atoms/cm<sup>3</sup>. This means that the addition of only 1 dopant atom per 107 silicon atoms almost completely controls the electrical properties of the silicon. Impurities are classified as either donors or acceptors. Donors are penta-valent elements whose atomic structure results in a loosely bound electron when the atom is embedded in the silicon lattice. Acceptors, on the contrary, result in an empty electron position being created in the lattice. This space, or hole, behaves in many circumstances as a positively charged particle which is free to move through the lattice. Both electrons and holes are called charge carriers because their movement constitutes current through a semiconductor. For the above reasons, silicon which has been doped with an acceptor dopant such as boron, is called p type since the majority charge carriers (holes) possess a positive charge. Similarly, silicon doped with a donor impurity such as phosphorus is called n type since the charge carriers (electrons) have a negative charge. Integrated circuits are formed on substrates which are part of a larger wafer. These wafers are sliced from large, single crystal silicon cylinders. There are several fundamental processing techniques which are then applied to the wafers. These basic techniques are elemental to any silicon semiconductor fabrication process.

Semiconductor fabrication is comprised essentially of an iteration of several fundamental processes including oxidation, deposition, etching, photolithography, diffusion and ion implantation. The first three are used at different times in the process flow for different reasons, while the latter two are employed chiefly for the purpose of doping. Silicon oxide may be grown or deposited. Oxidation, or oxide growth is the process by which a layer of silicon dioxide (SiO2) is formed on the surface of the wafer. It is important for device isolation as well as stress relief and dopant masking. When grown on the surface, it consumes silicon, and the oxide grows into, as well as out of the silicon substrate surface. Deposition is the means by which thin films of various materials are established on the surface of the wafer. There are many different forms of deposition, including chemical vapour deposition (CVD), vacuum deposition and sputtering. Oxide and nitride are usually deposited by CVD, and metal interconnect such as aluminum is usually sputtered. Etching is the process of selective removal of materials from the wafer, which may include portions of layers or films which have been deposited on the substrate, or some of the substrate itself. Wet etching is accomplished with liquid chemicals while dry etching, or plasma etching, is implemented with ionized gases. Photolithography is a process which renders

<sup>&</sup>lt;sup>1</sup> This will vary widely depending on the substrate architecture.

geometrically specific depositions generated from design data which are used as masks for etching as well as other processes such as implantation. The chemical agent used is called a photoresist, due to its unique sensitivity to light and its resistance to etching agents. The photolithographic process, in the traditional sense, involves the light projection of design mask information onto a deposited layer of photoresist. The light chemically alters the resist, and the unaltered areas are removed with a solvent, leaving behind the required geometry. This process is called developing the photoresist. During the etching procedure, the areas underneath the resist are protected from the etching agent, or etchant. In recent years, the need for smaller and smaller line widths in the photolithographic process have prompted the development of techniques using lasers [9] and X rays [10] instead of normal light. Some recent techniques use a process called electron beam lithography (EBL) to generate chip geometries on the wafer with a high energy electron beam.

In order to introduce impurities into the silicon substrate two main techniques are used which can be classified as diffusion and implantation. Diffusion is a process which achieves impurity placement within the silicon crystal lattice by providing a concentration gradient of dopant atoms. Under high temperature, typically 800 °C to 1400 °C, the atoms diffuse into the silicon, creating the dopant profile for the region. Different profiles can be achieved by using a finite or infinite dopant source. In either case, temperature and time are the critical factors, and thus high temperature steps are usually confined to the front end of the fabrication sequence in order to limit uncontrolled diffusion after domant profile establishment. Selective diffusion can be achieved by using silicon dioxide as a barrier. Wells are patterned and etched into a thick layer of oxide and the wafer is exposed to a dopant source, with the oxide blocking diffusion in unexposed areas. Ion implantation involves the acceleration of impurity atoms toward the substrate to be doped. The kinetic energy of the atoms is such that they are able to penetrate the crystal structure, thus achieving lattice placement. This technique allows implantation through a thin layer of oxide and very accurate doping profile control, both of which are very desirable traits. Disadvantages include the lattice damage resulting from the collision of dopant atoms with the crystal, and the sophisticated and expensive equipment required to implement the procedure. For the former reason, an implantation step is usually followed at some point by a high temperature anneal to repair the crystal lattice damage. A combination of implantation and diffusion may be used, where a shallow dopant implant is heated to allow the impurity to diffuse into the bulk. Many different improvements and variations to the

above basic practices have been implemented, but all semiconductor fabrication technologies still rely on these fundamental processes.

# 2.3 Typical CMOS Process Flow

As an example of a typical CMOS process flow, consider the CMOS3DLM process [11], which begins by patterning the p wells on the n substrate. These will be areas of p type silicon, and they will allow the creation of NMOS transistors. To form the wells, a layer of thick oxide is grown across the wafer, and a layer of photoresist is deposited. Using PWELL design mask information, the wafer is exposed, developed and etched to selectively remove oxide where p wells are to be implanted. A thin layer of oxide is grown over the exposed areas, and the p wells are implanted through this oxide. The thin and thick oxides are removed and a new layer of thin oxide is grown across the entire wafer. After this step, the resulting wells consist of areas of light p doping. Next, the NWELL mask layer information is used to define regions which will receive an n implant, or channel stopper, to set the threshold of non-active regions in the n substrate. This will assure that the parasitic device thresholds are such that there will not be inversion under the field oxide during normal operation of the chip. The PWELL mask is used to pattern a layer of photoresist over the p well areas to protect them from the channel stopper implant, which is carried out through the thin oxide covering the wafer. The photoresist is then removed, and a layer of silicon nitride (Si3N4) is deposited and patterned using the DEVWELL (device well) mask. Thus, regions which are to become parts of MOS transistors, diffusion interconnects, and capacitors are masked by the Si3N4. Photoresist is deposited and developed using the PGUARD mask, and a p implant into the p wells is performed next as a channel stopper. Since the device wells are still covered by nitride, they are protected from this implant, as are all regions outside of the areas defined by the PGUARD mask.

The photoresist is removed and a thick oxide is grown over the entire wafer, except in the areas covered by Si<sub>3</sub>N<sub>4</sub>. This oxide is called field oxide (FOX), and does not form in the device well regions since nitride inhibits oxide growth. The nitride is removed, and a thin gate oxide is grown over the device well areas. The NWELL mask is again used to pattern photoresist, and a p implant is used to adjust the threshold of the device wells in the n substrate which will later form PMOS transistors. This is necessary to counteract the previous n type channel stopper implant which was performed near the beginning of the process. If capacitors are to be created, the CAPDOP mask is used to define device wells

which will undergo a heavy p+ implantation through the gate oxide to form the bottom capacitor plates. At this stage, all device well regions are covered with gate oxide, and all other regions of the wafer are blanketed with FOX. A layer of polycrystalline silicon referred to as polysilicon, or simply poly, is deposited over the entire wafer, doped n+, and a layer of photoresist is then deposited. The POLY1 mask is used to develop the resist, thus defining MOSFET gates, interconnections, and capacitor top plates, and the wafer is then etched. The NPLUS mask is used to photolithographically define areas of n+ doping which will form the source/drain structures of the NMOS transistors, and n substrate contact areas. Similarly, the PPLUS mask is used to define the p+ regions corresponding to similar structures. The n+ poly involved in the source/drain doping step for the PMOS devices remains n+, despite the counter doping, due to their high n+ concentration.

Figure 2.1: P Well CMOS Process Cross-section

A thick layer of oxide is deposited over the entire wafer as an isolation layer on which the first level of metal interconnect will be patterned. The CONTACT mask is used to define contact windows which are etched away to allow the underlying layers to be contacted. A layer of aluminum is deposited across the entire wafer, and the METAL1 mask is used to define its geometry. This involves similar steps as before, i.e. photoresist development and etching. Another layer of SiO2 is deposited over the wafer to isolate the metal interconnect. VIA mask information is used to etch contact windows through the oxide to the underlying metal, thus allowing contact between the two metal layers. Another layer of metal is deposited over the wafer, and patterned using the METAL2 mask. Bonding and pad contacts are made to this level of interconnect. Finally, a passivation layer is deposited across the entire wafer. The GLASS mask information is used to etch openings to the

metal bonding pads, thus allowing connection by bonding wires. A cross-section of this process showing the important diffusions is shown in Figure 2.1.

#### 2.4 Evolution of the BiCMOS Process Flow

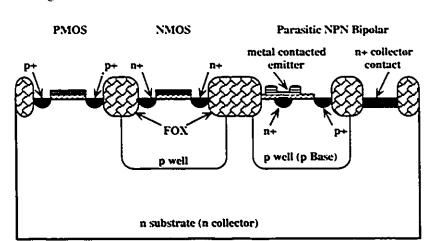

Considering the previous process description, it can readily be seen that a bipolar device is present in parasitic form, as shown in Figure 2.1. These devices have been effectively used as optical sensors in neural network designs [12], even though they are not an intentionally fabricated device. In such an application, the p well in which NMOS transistors are normally formed serves as the base. The substrate acts as the collector and a source/drain diffusion constitutes the emitter. This is a very poor quality transistor, however, since it possesses a very large effective base width. The chief difference in a BiCMOS process is that the BJT is intentionally designed into the process flow, and thus there are added features which increase the performance of these devices.

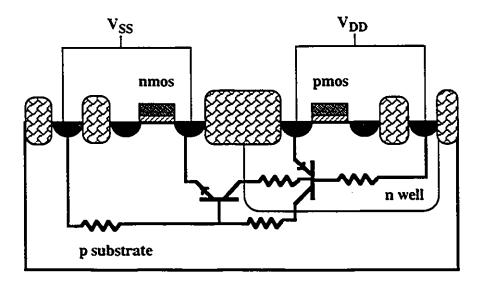

Since the main limitation in the above example of a bipolar device is the base width, a low end BiCMOS process can be envisioned with the addition of only one additional mask layer to form a thin base. Consider a simple n well CMOS process with the conceptual cross-section illustrated in Figure 2.2.

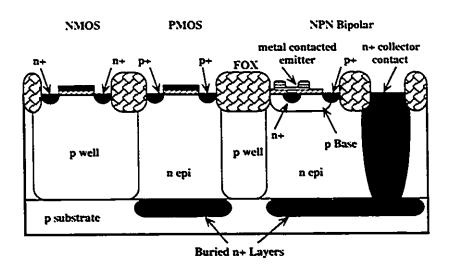

Figure 2.2: Low End BiCMOS Process

An NPN transistor has been formed with the n well acting as the collector, an n+ NMOS source/drain diffusion acting as the metal contacted emitter and a PMOS source/drain p+ diffusion acting as the base contact. With the addition of one extra mask level, a thin base has been formed by a single p implantation step, thus yielding a bipolar structure with

much higher performance than in the parasitic case. Typical base regions in early BiCMOS technologies were about 1µm deep with a doping of about 10<sup>17</sup> atoms cm<sup>3</sup>. Even though this is a substantial improvement, the quality of the bipolar device has still been compromised in order to maintain common fabrication steps with its CMOS parent process. The main limitation inherent to this bipolar structure arises from the lightly doped n well, which has a correspondingly high resistance. This will cause the collector resistance to be high, which in turn will yield a device with low cutoff frequency, poor current drive, and a high collector-emitter saturation voltage. All these factors will limit the performance of the BJT.

Figure 2.3: BiCMOS Process With Buried Layers and Deep Collector

Contact

The collector resistance can be reduced in several ways, all of which are at the cost of increased process complexity. Consider Figure 2.3 which shows a conceptual cross-section of an improved BiCMOS process. Buried n+ layers have been implanted into the p substrate and an n doped epitaxial layer, or epi, has been grown on top of this (typically a few microns thick). Since the buried n+ layers and the n wells are aligned, an additional mask level is not required. An extra mask level has been added to define a deep n+ contact which traverses the depth of the epi in order to form a low resistance contact to the underlying buried layer. This contact can be implanted after FOX formation. In addition to reducing the collector resistance, the buried layers also reduce the susceptibility of the process to latchup by effectively reducing bulk resistance. There are, however, several drawbacks to this scenario, one of which is that the packing density of the devices is limited due to isolation considerations. Two adjacent n+ layers corresponding to two

separate bipolar devices must be separated by a large distance of lightly doped p substrate to avoid collector to collector punchthrough from one device to the other. This is due to the fact that since the substrate is lightly doped, and the buried layers are heavily doped, the depletion regions resulting from the pn junctions formed where the two regions meet will extend a large distance into the p substrate. Unfortunately, simply raising the substrate doping is not an optimal solution. Although this will allow closer device spacing, the increased doping will cause a corresponding increase in the collector—substrate capacitance, thus reducing bipolar performance. Another problem with the above bipolar structure is that the n epi region must be counter doped in order to isolate n well regions. and to form p wells for NMOS devices. Counter doping the n type epi layer causes processing difficulties as well as performance reduction in NMOS transistors due to mobility degradation. Since the n+ emitter and the source drain diffusion share the same process step, a low quality emitter is rendered which is contacted by metal. This limits device performance<sup>1</sup>. Even with these shortcomings, the bipolar devices resulting from this process are far superior to those of the process illustrated in Figure 2.2. The improvement has been realized by the addition of only two mask levels to the baseline CMOS process. The first one defines the thin p base implant, and the second defines the n+ deep collector implant.

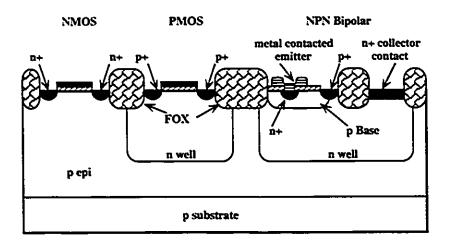

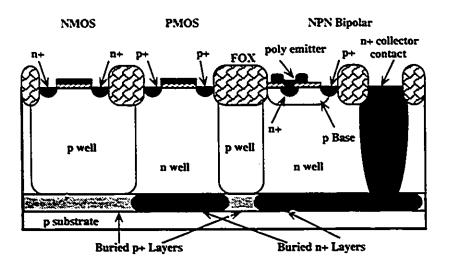

Figure 2.4: BiCMOS Process With Self Aligned Buried Layers and Poly Emitter

Examining Figure 2.4, an improvement to the above process can be made by providing self aligned buried n+ and buried p+ layers. This effectively reduces the minimum collector to

<sup>&</sup>lt;sup>1</sup> Emitter considerations will be discussed in chapter 3.

collector spacing, but increases the collector sidewall capacitance because an extra, highly doped, pn junction sidewall capacitance component is present. Since there is a buried p+ as well as a buried n+ layer, however, the substrate doping can be reduced, thus shrinking the net collector capacitance without compromise of packing density. A near intrinsic epi is grown, and self aligned n wells and p wells are defined. This eliminates the counter doping problem encountered with the n-type epi mentioned previously, and is what is referred to as a twin-tub process, since both well regions are doped individually.