#### **University of Windsor**

#### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1991

#### Communication architectures for single-chip data routers.

Gopal. Panneerselvam University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Panneerselvam, Gopal., "Communication architectures for single-chip data routers." (1991). *Electronic Theses and Dissertations*. 1481.

https://scholar.uwindsor.ca/etd/1481

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in tull or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a tait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# COMMUNICATION ARCHITECTURES FOR SINGLE-CHIP DATA ROUTERS

by

#### Gopal Panneerselvam

A Dissertation Submitted to the

Faculty of Graduate Studies and Research

through the Department of Electrical Engineering

in partial fulfillment of the requirements for the Degree of

Doctor of Philosophy

at the University of Windsor

Windsor, Ontario, Canada 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-72803-5

Gopal Panneerselvam 1991

© All Rights Reserved

# **ABSTRACT**

This dissertation presents a novel architectural technique for systolic architectures for applications which traditionally use high wire organizations in VLSI.

Following a review of current VLSI research and VLSI models, this dissertation argues for a particular computational model (Chazelle's model) as being appropriate for today's VLSI and ULSI technology.

Systolic arrays are particularly suited for applications where only local interprocessor communication of data is required. In areas where non local data communication is predominant, the so called "high wire organizations" are traditionally used. Such networks include sorting arrays, interconnection arrays. Using Chazelle's model, an analysis of well known interconnection networks shows that "inefficient" systolic arrays, for routing and for sorting, outperform, so far as asymptotic performance metrics are concerned, high wire organizations traditionally used for such applications.

This dissertation then proposes a new systolic architecture using the novel design philosophy of locally long but globally short connections. This involves designing arrays using large, complex cells instead of fine grained cells. This is termed "systolic architectures using cells of controllable complexity" since the latency and/or pipeline period requirement of a user determines the size and hence the interconnection complexity of the cells in a systolic array of complex cells. It turns out that many important application areas (e.g., interconnection networks, sorting networks and FFT) are suitable candidates for this approach. This class of architectures is well suited for ULSI implementation.

An experiment in designing interconnection networks show that this concept of arrays using cells of controllable complexity is useful, even in current 1.2µ VLSI technology.

## ACKNOWLEDGEMENT

I would like to express my cincere gratitude to my supervisors, Dr. G.A. Jullien, Dr S. Bandyopadhyay and Dr W. C. Miller for their patience, concern, advice and personal support during my stay in Windsor. Without this constant encouragement and stimulating discussions, it would have been impossible to complete this investigation. I also express my gratitude to members of my advisory committee, Dr. H.W. Kwan and Dr. Frost for their numerous comments and suggestions during this period.

I am grateful to Dr.E. Swartzlander, University of Texas at Austin, who has agreed to act as my external examiner, in spite of his extremely busy schedule. I am also grateful for his valuable suggestions.

During my investigations, Mr Bruce Erickson, Research Manager VLSI Research Group, has been extremely helpful. Without this support, it would have been very difficult to use the VLSI design tools effectively. I am also very thankful to all my colleagues in the VLSI research group. In particular, I would like to acknowledge the moral and intellectual support I have received from Mr A. Annaamalai, Mr. D. Phoukas, Mr Bill Robison, Ms. A. Sarkar, Mr. Ed Scott, Prof. Wang and Dr. D. Zhang. Mr D. Reaume and Dr.N.M Wigley of Mathematics department have been generous with their time and valuable advice.

Without the unstinting moral support, encouragement and love I received from my wife Nirmala during many difficult periods, this work would not have been possible. My daughter Priya made all this effort worth while.

Finally, I express my heartfelt thanks to my parents who sacrificed so much so that I may get ahead in life. Without their love, encouragement and care, I could not have reached this point in my career.

# TABLE OF CONTENTS

| CHAPTE | R 1 INTRODUCTION1                                     |

|--------|-------------------------------------------------------|

| 1.1    | PREAMBLE1                                             |

| 1.2    | COMPETING ARCHITECTURES IN THE VLSI /ULSI ENVIRONMENT |

|        | 1.2.1 SYSTOLIC ARCHITECTURES2                         |

|        | 1.2.2 HIGH WIRE ORGANIZATIONS                         |

| 1.3    | NEED FOR VLSI MODELS                                  |

| 1.4    | SCOPE OF THIS THESIS5                                 |

| СНАРТЕ | ER 2 REVIEW OF VLSI/ULSI MODELS9                      |

| 2.1    | INTRODUCTION9                                         |

| 2,2    | MODELLING A VLSI CIRCUIT                              |

| 2.3    | TIME13                                                |

| 2.4    | AREA                                                  |

| 2.5    | I/O CONSIDERATIONS                                    |

| 2.6    | PERFORMANCE METRIC FOR VLSI                           |

| 2.7    | EFFECT OF SCALING IN VLSI/ULSI                        |

| 2.8    | A MODEL FOR ULSI TECHNOLOGY21                         |

| 2.9    | SUMMARY23                                             |

| CHAPTE | R 3 ULSI SYSTOLIC ARRAYS FOR ROUTING AND FAST         |

| COMPUT | ATIONS24                                              |

| 3.1    | INTRODUCTION24                                        |

| 3.2    | ANALYSIS OF SOME INTERCONNECTION NETWORKS                   |

|--------|-------------------------------------------------------------|

| 3.3    | A SYSTOLIC ARRAY FOR ROUTING33                              |

| 3.4    | SORTING NETWORKS FOR SELF ROUTING36                         |

| 3.5    | SUMMARY41                                                   |

| CHAPTE | ER 4 SYSTOLIC ARCHITECTURES WITH CELLS OF CONTROLLABLE      |

| COMPLI | EXITY42                                                     |

| 4.1    | INTRODUCTION42                                              |

| 4.2    | THE LLGS PHILOSOPHY43                                       |

| 4.3    | A SYSTOLIC ARRAY FOR SORTING                                |

| 4.4    | DESIGN OF MERGING CELLS                                     |

|        | 4.4.1 A CELL FOR BITONIC MERGING54                          |

|        | 4.4.2 A CELL FOR ODD-EVEN MERGE SORTING57                   |

| 4.5    | PIPELINING WITHIN THE CELL                                  |

| 4.6    | ANALYSIS OF SYSTOLIC ARRAYS FOR SORTING USING COMPLEX CELLS |

| 4.7    | DESIGN OF A SYSTOLIC ARRAY FOR ROUTING                      |

| 4.8    | DESIGN OF A NEW TWO DIMENSIONAL SYSTOLIC SORTING NETWORK    |

| 4.9    | COMPLEXITY OF THE ALGORITHM70                               |

| 4.10   | A NEW NETWORK FOR SORTING WITH COMPLEX CELLS70              |

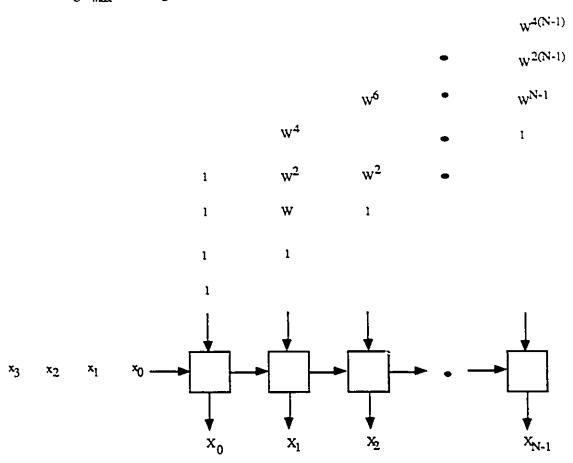

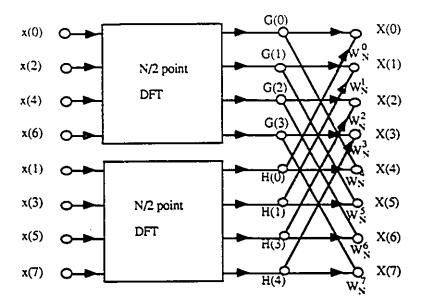

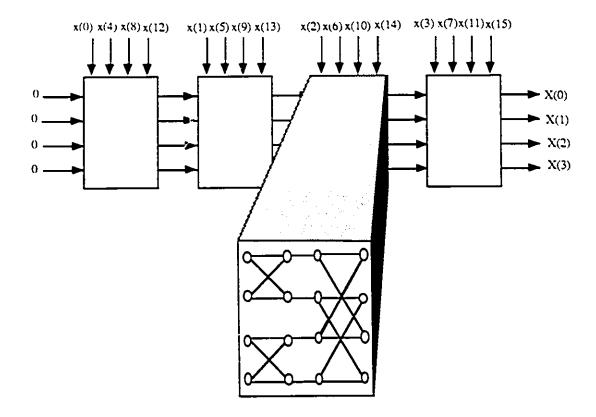

| 4.11   | DESIGN OF AN FFT SYSTOLIC ARRAY71                           |

| 4.12   | SUMMARY77                                                   |

| СНАРТЕ | R 5 FABRICATION OF VLSI INTERCONNECTION ARRAYS79            |

| 5.1   | INTRODUCTION79                                                   |

|-------|------------------------------------------------------------------|

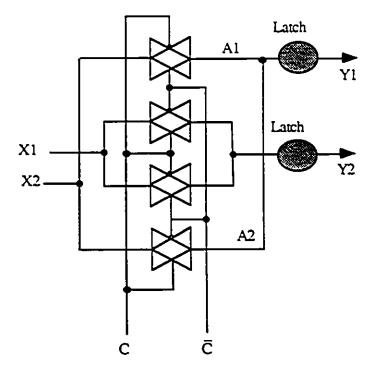

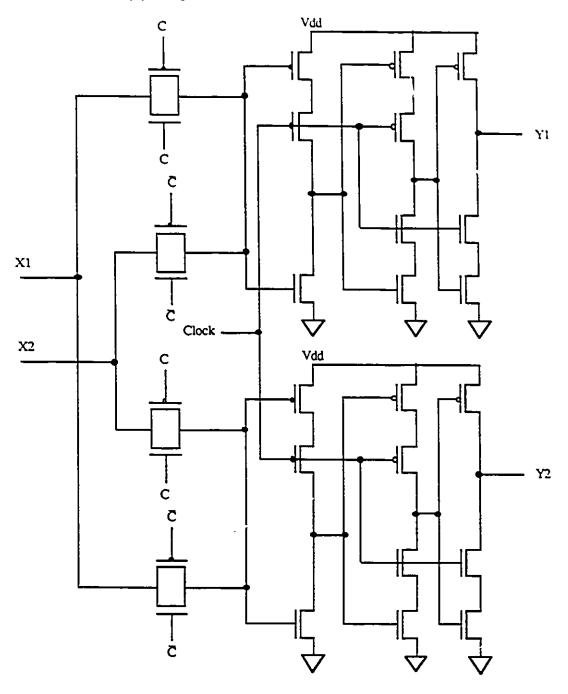

| 5.2   | DESIGNING A LATCHED SWITCH80                                     |

| 5.3   | ESTIMATION OF WIRE DELAYS                                        |

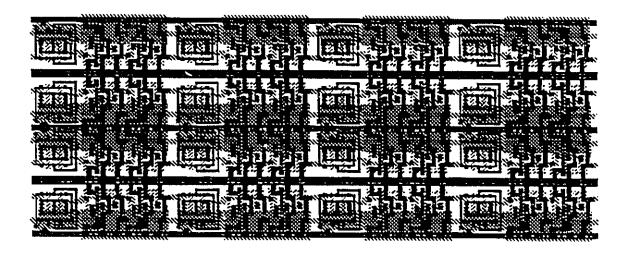

| 5.4   | DESIGNING A SYSTOLIC ARRAY OF SWITCHES88                         |

| 5.5   | DESIGN OF A BUTTERFLY USING AN AUTOMATIC PLACE AND ROUTE PACKAGE |

| 5.6   | DESIGN OF A BUTTERFLY USING CUSTOM LAYOUT94                      |

| 5.7   | A MODEL FOR LAYOUTS OF BUTTERFLY NETWORKS OF ARBITRARY SIZE 94   |

| 5.8   | SIJMMARY102                                                      |

| СНАРТ | ER 6 CONCLUSIONS104                                              |

| 6.1   | CONCLUSIONS104                                                   |

| 6.2   | DISCUSSION105                                                    |

| 6.2   | SUGGESTIONS FOR FUTURE WORK108                                   |

| REF   | ERENCES110                                                       |

| VITA  | A AUCTORIS                                                       |

# **CHAPTER**

1

#### INTRODUCTION

#### 1.1 PREAMBLE

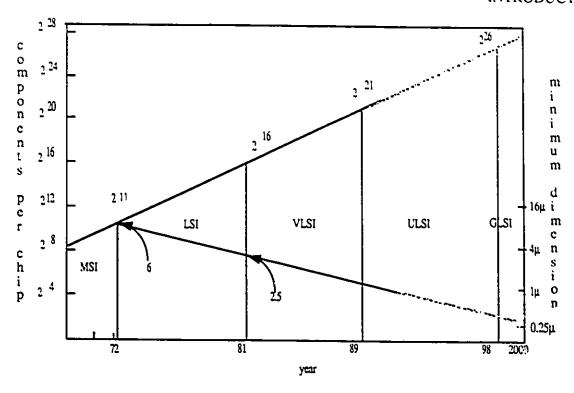

The continuing evolution of semiconductor technology, with respect to reduction of minimum feature size, enlargement of chip area and improvement in packing efficiency has made it feasible to put millions of transistors in a single chip. The industry is emerging from the Very Large Scale Integration (VLSI) era into the Ultra Large Scale Integration (ULSI) era (feature size < 1µm) [47][46][16]. Reismen's curve in Figure 1.1 depicts this dramatic development [61][16]. It is expected that 16M DRAM (0.5µ technology) will be commercially available in 1993 [16]. 64 MByte DRAMs are currently under development and will undoubtedly be in the market place by the middle of the decade. In view of these developments, it is important to look at the change in architectures that we wish to place on high density chips as we traverse the VLSI/ULSI technology boundary. The theme that will emerge from this thesis is that solutions which are expensive in terms of number of active elements but are more efficient in terms of layout area and speed of operation are the order of the day for applications that will be in the supercomputer class. We will identify such architectures with a class of systolic arrays [34][33][35][40][41] that we expect will blossom as the technology develops. Systolic arrays are well established for arithmetic computation, where only local inter processor data movements are required. In this thesis, we will show that systolic arrays are further applicable for data routing applications, where data moves rapidly, such as sorting or interconnection networks.

Figure 1.1 Reisman curve. Number of component density versus time.

# 1.2.1 COMPETING ARCHITECTURES IN THE VLSI /ULSI ENVIRONMENT

As the technology advances, it is important to examine the existing architectures and compare them from the technological point of view, as well as with the advancement of CAD tools. We can divide these architectures into two major categories using their communication structures, namely, locally connected systolic organizations and high wire organizations [82].

### 1.2.1 SYSTOLIC ARCHITECTURES

A systolic array is a set of interconnected cells, each capable of performing some simple operation [34][40]. Systolic architectures have been investigated over the last ten years for important classes of digital systems. Although their use has been somewhat limited, this is undoubtedly due to the mis-match of silicon technology available during the time that these architectures were developed. Our thesis is that certain classes of systolic arrays will become important as the technology provides greater integration density.

The main reason for our optimism is that systolic architectures provide an area efficient layout without communication overhead by exploiting the nearest neighbor connection on regular geometrical shaped processors [34][40][18]. Various circuits based on systolic architectures have been proposed for applications such as matrix computations, data base machines, digital signal processing and simulated annealing [9][35][36][48][55][77][75]. Systolic arrays have high throughput since they use extensive pipelining. The nearest neighbor connection is an important property of systolic arrays since complex interconnections are expensive in terms of silicon area in VLSI/ULSI designs.

It is convenient to test the electrical characteristics of a small number of cells thoroughly before designing a systolic array using a large number of such cells. Diagnosis of such structures is often quite straight forward [60] involving a constant number of test vectors independent of the size of the array. With this architectural simplicity, researchers have extensively investigated systolic architecture in VLSI design methodology. Many researchers recommend systolic architectures as a suitable candidate for future generation chips or integrated systems, viz., Wafer-Scale-Integration (WSI), 3-D chips [39][76].

#### 1.2.2 HIGH WIRE ORGANIZATIONS

High wire organizations consist of processors or nodes connected using long communication links to achieve an optimal number of processors, with a minimum number of steps. Their ability to transmit large amounts of data across arbitrary boundaries quickly gives these organizations an essential advantage, for many important applications, over organizations like the rectangular grid. These high wire organizations are recommended for "supercomputers". The fast communication capabilities are essential for data routing applications such as interconnection networks, sorting, FFT computations, etc. The implementation aspects of high wire organizations in VLSI have been studied by many researchers [19,25,30,42,78-80,82], and their results have shown that the area required for interconnection dominates processor area.

In this dissertation we examine both high wire and systolic organizations for currently available technologies, and show that systolic organizations are not only suitable for arithmetic computation, which only require local data movement, but are also suitable for high data routing applications in the ULSI environment.

#### 1.3 NEED FOR VLSI MODELS

In order to analyze the performance of different VLSI circuits, it is important to have an adequate model. Prior to the VLSI era, the complexity of a circuit was measured in terms of the gate or transistor count. In VLSI implementations, however, the area needed for interconnecting active devices became very important. In the so called 'high wire' organizations [82] this area is far higher than the area occupied by active devices. A number of models have been investigated in recent times [8][12][11][45][78][79]. These models allow us to estimate the asymptotic bounds on characteristics such as chip area, computational time, latency time and pipeline period. Such models are technology

independent. We have to remember that the asymptotic bounds on the performance predicted by these models will be particularly useful as we move into progressively denser ULSI circuits in the next few years where the number of cells in a chip will be at least a hundred times larger than they are today [20][16]. Asymptotic bounds show the relationship of the inputs on the parameters of area and time; however, the value of the asymptotic constants are hidden. In this thesis we propose a pragmatic design methodology for VLSI and ULSI technologies that includes the importance of these constants.

#### 1.4 SCOPE OF THIS THESIS

In this thesis, we investigate applications of systolic arrays for routing applications. We explore novel non traditional applications of systolic arrays and show that, in terms of asymptotic bounds, simple systolic arrays have better asymptotic performance bounds than circuits based on more complex interconnections. Several such circuits have been proposed in the literature. Traditional designs have attempted to minimize the number of processing elements in digital systems. In the ULSI era, a complex digital subsystem consisting of numerous processing elements can be fabricated on a single chip. We show that the asymptotic bounds on the performance of such systems need to take the intercell propagation delays into account. Using an appropriate VLSI model, which does take this delay into account, we show that simple systolic realizations are potentially superior to solutions which attempt to minimize the number of processors using a high wire organization. However, minimizing the number of processors is also an important factor, which we considered when taking into account minimizing communication overhead. The resulting methodology yields a new class of area and time efficient systolic architectures.

In chapter 2, we briefly review key concepts in VLSI design that allow the determination of performance metric for VLSI circuits and argue for Chazelle's model [11] in the emerging ULSI era.

In chapter 3, we look at the applicability of systolic arrays in designing interconnection networks. In multiprocessor design, efficient data communication capabilities are extremely important and, in this context, we analyze a number of popular routing networks. We show that if the propagation delays are taken into account, the performance metric of networks which are currently popular are not attractive. We also examine a "cross bar switch" type network, that can be easily realized as a systolic array, and even though the number of 2X2 switches in such a network is large, the propagation delay between stages of the network is constant, independent of the size of the array. The performance metric of the systolic routing network are superior to routing networks which use high wire organizations. We follow this by a critical evaluation of the problem of self routing [50] in such networks. In a multiprocessor system, the routing network may have to change permutations quite frequently. Indeed, every successive communication from a given processor may specify different processors as destinations. This means that the time required to determine the switch settings in a routing network may be a very significant factor when determining the throughput rate of the network. A straight forward way to handle this problem is to use a self routing [50] scheme. A perimeter sorting network [14] is an obvious solution to achieve self routing. We show that a sorting network, based on the systolic version of Kautz' network [28], has a better performance metric compared to sorting networks requiring fewer processors and high wire organizations. The low latency time makes this S-array attractive in designing interconnection networks.

In chapter 4, we define a new concept of *locally long*, *globally short* interconnections in a systolic array; this concept is offered as a technique for handling massively parallel computational networks for ULSI densities. Using sorting as the main application area, we

have defined complex cells in which the intracell communication uses a high wire organization. The size of a cell is determined by the desired pipeline period and the fabrication technology. Using these cells as a basic building block, we then define systolic arrays for sorting where the intercell communication is based on local (nearest neighbors) connections alone. Using this approach it is possible to achieve a compromise between the complex interconnection of a high wire organization requiring relatively few cells and simple organization of a systolic architecture requiring more processors. We call this approach 'systolic architectures using cells of controllable complexity' since the complexity of intracell communication, which has a direct bearing on the complexity of the cells constituting the array, may change from application to application. This complexity is determined by user requirements and the fabrication technology being used. Then we present another perimeter sorting algorithm which may be readily realized by a systolic network using 2X2 comparators. This network has the same asymptotic bounds as the Sarray, so far as the area and time are concerned, but actually requires fewer cells. This approach is also amenable to the complex cell approach. We finally show that the concept of complex cells is useful in deriving globally short routing architectures; we demonstrate that this concept maps to computationally intensive routing networks using the Fast Fourier Transform (FFT) as an example.

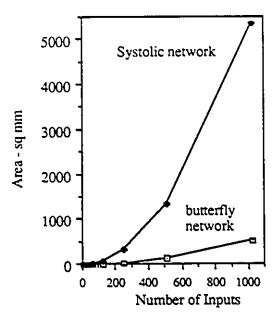

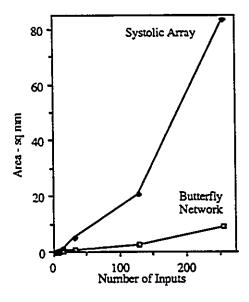

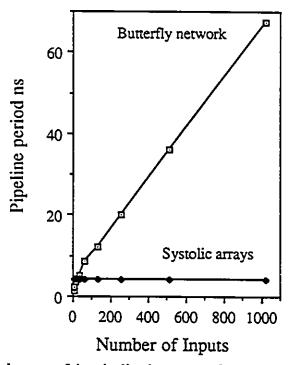

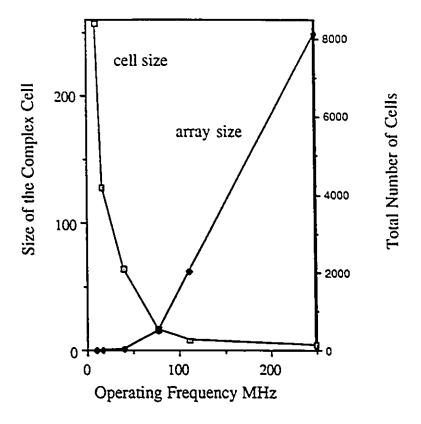

Finally, in Chapter 5, we cement the new concepts introduced in this research work using empirical results obtained from a double metal CMOS 1.2  $\mu$  fabrication technology. We consider routing as the application area and design a systolic array and butterfly network using a layout scheme which is applicable to networks of any size. We develop a model for the area and time of a butterfly element of arbitrary size and determine that a network of such butterflies has a considerably smaller area compared to a systolic layout; however, the pipeline period of a butterfly degrades linearly with the size of the network. We use our model to examine different scenarios ranging from a very fast routing network to a network

with relatively low speed requirements. We observe that for different speed requirements, it is advantageous to use systolic arrays with cells of different sizes. This establishes the fact that, even for current technologies, our approach of systolic architectures using cells of controllable complexity offers advantages over conventional designs.

We conclude the thesis with a discussion of the findings of the Usearch work in Chapter 6. Suggestions for future work are also offered.

# **CHAPTER**

2

REVIEW OF VLSI/ULSI MODELS

#### 2.1 INTRODUCTION

Since different VLSI circuits may have completely distinct characteristics, it was difficult, in the past, to come up with a standard way to compare circuits to solve a given problem. Another difficulty was to estimate how the complexity of the circuit changes if the size of the problem changes. A substantial amount of investigation into these problems has led to models of computation for VLSI. These theoretical models are essential for evaluating and comparing circuit performances and in establishing lower bounds on chip areas and computation times. In this chapter we review, briefly, how this modelling is performed and argue for a particular model which appears appropriate for ULSI technology. In subsequent chapters, we will use this model to compare existing VLSI and ULSI arrays.

The most important parameters in any VLSI computational model are the area of the circuit and its speed. The size of the circuit is extremely important even in printed circuit board design [73]; in VLSI fabrication, the cost of fabrication of a circuit is an exponential function of its area, A, [82]; the maximum die area for a single chip is on the order of 1cm<sup>2</sup>. Silicon area consumed is more important than the transistor or gate count used in earlier performance metric. Thompson shows in his dissertation [79] that, in many circuits, the area of the chip is determined by the interconnection area rather than the area occupied by transistors. In other words, communication in VLSI is not free. Since

communication between transistors may require more silicon area than the area for the active elements themselves, it is important to consider the actual layout of active elements in the plane, along with their interconnections, when analyzing a VLSI circuit.

Two parameters are important in determining the speed of a circuit. The first parameter is the time of computation, T. We also use the term latency time, interchangeably with the term "time of computation", to describe T. One way of determining this parameter is by counting the number of elementary operations that are performed by the circuit when computing its output [78]. However, a more convenient way is to measure speed as the time between the application of the first input bit and the appearance of the last output bit [11]. We will follow the latter convention. The second parameter is the pipeline period, P. This is determined by the minimum time separating two input sets [83].

In this chapter we briefly review the graphical model for VLSI circuits, and speculate on how the trends in this decade will affect the design of next generation ULSI circuits. We review the notion of area in graph theoretic terms. To model time, we examine four popular models. We look at restrictions on I/O placement and use a conservative and practical method to place I/O pads for this investigation. We describe popular performance metric for VLSI circuits which are in the form AT, AT<sup>2</sup>, AP and ATP and their physical significances. We have used all these metric in this thesis. Finally we look at the current trends in ULSI technology. We argue that, in view of ULSI trends, for high wire organizations, among the four models for time estimation that we have mentioned, the linear delay model for time is most applicable.

#### 2.2 MODELLING A VLSI CIRCUIT

Pioneering work on models for VLSI computation was performed by Thompson [78][79]. Brent R.P. and H.T. Kung [8], Mead [44][45], Vuillemin [83], Chazelle and Monier [12], [11], Lipton et al. [43]. Mead and Rem are among the first investigators who pointed out a need for a novel complexity theory, which involves functions of both area and time, so that, when estimating the area, the size of the processing element as well as wire area is to be included [45]. Mead and Conway also introduced VLSI design using  $\lambda$ , the elementary distance unit [44].  $\lambda$  depends on technology and has steadily become smaller with time. Abelson was among the first to point out that communication between processors is a significant cost in the complexity of distributed systems [1].

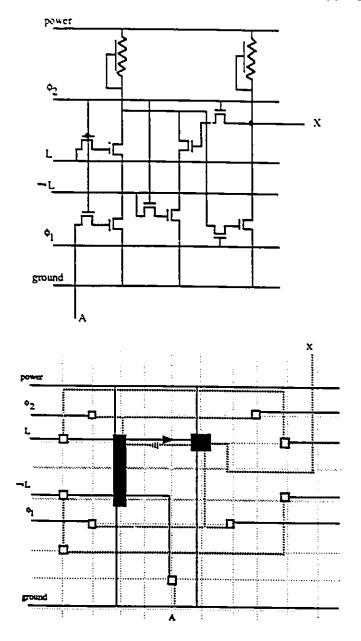

We now describe, in some detail, the graph model we will use in this thesis. Any VLSI circuit can be modelled [79] by a directed planar graph where the nodes correspond to the active elements, e.g., transistors, or cluster of transistors, or gates (Thompson uses the term nexus [78] for nodes) and edges representing interconnections. The edges are used for transfer of information from one node to another node, to a power line or to clock generators. The computational graph is depicted as a grid of unit squares. This is the reason why the model is known as the grid model. Each side of unit square in the grid model represents manufacturing and physical limitations. Following the recommendations of Mead and Conway, this minimal spacing in the grid model is  $4\lambda$ . This gives us the size.  $16\lambda^2$ , of a unit square. One unit square is just large enough to contain one transistor or one wire cross over. Wires are laid out on a grid with unit spacing. If two metal layers are available, one layer is devoted to the x direction and the other to the y direction as described in [44]. Wires meet only at a node, which are represented as squares. If d wires connect to a node, then the node is a square with side d. At most two wires may cross each other at any point in a plane. Wire may not cross over nodes, nor can nodes cross over nodes. A grid model realization is illustrated in Figure 2.1 [82].

Figure 2.1 A simple register cell and its grid model representation

VLSI circuits are implemented as convex planar graphs, because of heat-dissipation and packing requirement [8]. This is a convention that we will follow in our systolic arrays.

#### **2.3 TIME**

A unit of time is the minimum time in which an event occurs (e.g., the time taken for a transistor to switch). In a practical circuit, for instance, using a two phase clock, the unit time is between the leading edges of the clocks driving each of the two phases [82].

Models differ radically in the mechanism they use to compute the time of computation T. There are four models that have been proposed for estimating communication time in a VLSI circuit as discussed below:

- i) Constant time model: In this model, a bit requires constant time τ to propagate along a wire regardless of the length of the wire [8]. This has also been called the synchronous model.

- ii) Logarithmic time model: In this model, a bit requires a time O(log 1) time to propagate along a wire length 1 [44] and [80]. This assumes that there are log 1 stages of drivers to amplify the signal. Larger drivers, of course, occupy more area, but never take more than 10% of the wire they drive [79], [80].

- iii) Capacitive model: In this model a bit requires O(1) time to propagate along a wire of length 1 [7].

- iv) Diffusion model: In this model a bit requires a time O(12) to propagate along a wire of length 1 [11][68].

The ultimate justification for the linear model comes from a speed-of-light argument. No information can propagate faster than light. Moreover, in practice, parasitic effects reduce the speed of propagation several orders of magnitude below that limit and this makes the linear dependency important [11].

Based purely on asymptotic considerations, the diffusion model appears most realistic since the resistance, R, and the capacitance, C, of a wire of length 1 are both proportional to 1. Thus the RC delay is proportional to  $1^2$ . Thompson as well as Mead and Conway indicate that the propagation delays may be made independent of the wire length by fitting larger drivers to longer wires. This is applicable for short wires typical of VLSI circuits fabricated in the early eighties. Chazelle suggested that it may be necessary to decompose long wires into wires of constant length connected by delay (computing the identity function). This gives us the linear delay model. A careful analysis of physical phenomena occurring in VLSI circuits appears in [7]. This reference considers the synchronous, capacitive and diffusion model, and defines a figure of merit  $\gamma = \frac{c_1}{C_0}$  where c is the capacitance of wire per unit length, 1 is the length of wire and C0 is the capacitance of the active device. They conclude that

- for small  $\gamma$ , ( $\gamma < 1$ ), the propagation delay is constant (synchronous model)

- for moderate  $\gamma$ , ( $1 \le \gamma \le 1000$ ), the propagation delay is linear (capacitive model)

- for large  $\gamma$ , (1000  $\sim \gamma$ ), the propagation delay is nonlinear (diffusion model)

In terms of the technology of the early eighties, the synchronous model was quite valid. The trend, however, is definitely to, at least, moderate values of  $\gamma$  and we will see, in section 2.8, Chazelle's assumption, that the time of propagation along the wire is at least proportional to the length of the wire, appears to be accurate in the foreseeable future. In our analysis we will use the linear delay model.

#### 2.4 AREA

The lower bound on the total area, A, of the embedded communication graph occupied on a grid is equal to the number of unit squares occupied by wires or nodes. The number of squares in the smallest bounding rectangle is represented as the upper bound [79]. Baudet [6], Krishnan [32] and Kurdahi et al. [37] proposed different approaches for measurements of area; however we follow Thompson's method.

Figure 2.2 Thompson layout for n=16 Shuffle Exchange graph.

As an example, Fig 2.2 shows the communication graph for a shuffle exchange network. The lower bound here is 58 units and the upper bound is 60 units.

#### 2.5 I/O CONSIDERATIONS

Placement of I/O pads and the possibility of replication of input pads have some importance in VLSI complexity analysis. Savage [66][67], assumed that each input variable is supplied exactly once to the chip and each input enters at one place on a chip. Kedem and Zorat [29] showed that relaxation of Savage's restrictions (i.e., input replications both in

space and in time) may be quite profitable. Baudet [6] assumed that both inputs and outputs are data independent, and input variables are read only once. Memory based storage structures are proposed by Wong and Kung [84]. Other researchers have imposed limitations on I/O port size, minimal area I/O port, fixed area I/O port and entropy constraints for internal data communication [8][11][83][86].

In our discussions, we have not looked at I/O considerations in great detail. In our designs, we will ensure that all data input to (or output from) an array is along the perimeter of the chip. This avoids the problem of considering the additional overhead of routing the input (output) lines inside the array itself.

#### 2.6 PERFORMANCE METRIC FOR VLSI

As explained earlier, the performance from VLSI models is measured by using area, A, and time, T, or some combination of these two [45]. Thompson proved his lower bounds on the performance of a VLSI circuit by considering the communication graph for a VLSI array. He defined a minimum bisection width ' $\omega$ ' of the communication graph as the number of edges that need to be removed to disconnect one half of the vertices from the other half. The area of the graph is proved to be at least proportional to the square of its bisection width since Thompson showed that  $A \ge \omega^2/4$ . The time taken by the communication graph (to solve a n-point DFT problem or a sorting problem) is at least inversely proportional to its width,  $(T = \Omega(n \log n)/\omega)$ .

Different researchers have proposed different performance metric based on the area, A, and time, T. The most common metric is the area time product AT. Another bound  $AT^2$  has also been used, and many 'strong' lower bounds, that do match the best circuit we can construct, are lower bounds on the product  $AT^2$  [82]. This bound is based not on memory

requirement or input/output rate, but on the requirements for information flow within the chip [82]. One convenient way to characterize all metrics used in the literature is to use the general form  $AT^{x}$ , for some x,  $0 \le x \le 2$ . The time taken by the communication graph (to solve the n-point DFT or sorting problem) is at least inversely proportional to its width,  $(T = \Omega(n \log n)/\omega)$ . The minimum value of a performance metric having the form  $AT^{x}$  occurs, when  $\omega = \theta(n^{1/2})$ . This leads to a general lower bound [79].

$$AT^{X} = \Omega(n^{1+x/2} \log^{X} n), \text{ for } 0 \le x \le 2$$

(2.1)

For pipelined systems, Chazelle et al. introduced the ATP bound where P is the pipeline period. For many applications (e.g., digital signal processing), latency time is not very important. What is important is to have a very high throughput rate. A good circuit, in such applications should have a low area, A, and a low pipeline period, P. For such applications, the metric, AP, is an appropriate lower bound [6].

In our investigations, we will use the metrics AT,  $AT^2$ , ATP and AP to analyze the complexity of VLSI circuits.

#### 2.7 EFFECT OF SCALING IN VLSI/ULSI

Miniaturization of MOS transistor dimensions continues to improve circuit speed and packing density. Ideal scaling theory was one of the first approaches to model the shrinking of MOS transistors [15]. When a MOS device is scaled in five dimensions — the three physical dimensions, voltage level, and doping concentration, it leads to greater speed and density as well as lower power consumption. Scaling improves circuit performance by reducing capacitances and voltage swings and, at the same time, ensures the physical integrity of devices by keeping the electrical field constant

[3][16][20][24][44][47][46][71]. Voltage scaling has not yet been a major factor due to commercial considerations [3].

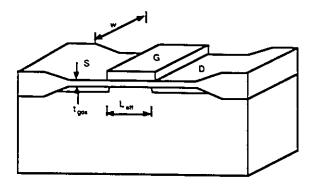

An MOS transistor is shown in Fig 2.3.

Figure 2. 3 A MOS transistor.

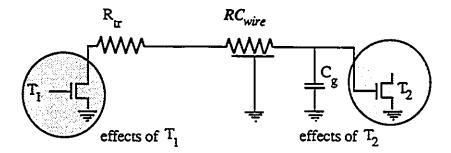

Table 2.1 [3] shows the effects of scaling on such devices. The table shows that, with scaling, devices get faster, power dissipation and power-delay products of the devices are reduced, packing density improves, and power dissipation density remains constant. Fast chips that integrate a large number of transistors become possible and the VLSI era has now given way to the ULSI era with continuing improvements in scaling [47][46]. Interconnection issues are the main factors that determine the number of elements in the circuit that can be integrated on a chip with a given chip performance [3][20][2][23][24][51][62] [63][64][65][71][87]. This is true for CMOS, bipolar, and gallium arsenide (GaAs) technologies [3].

Table 2.1 Scaling effects on Transistor

| Parameter                                                                        | Scaling factor S |

|----------------------------------------------------------------------------------|------------------|

| Dimension (W,L,tgox, Xj)                                                         | 1/S              |

| Substrate doping (NSUB)                                                          | s                |

| Voltage (V <sub>DD</sub> , V <sub>TN</sub> , V <sub>TP</sub> )                   | 1/S              |

| Current per device ( $I_{DS}\alpha W \epsilon_{ox}/L t_{gox} (V_{DD} - V_T)^2$ ) | 1/S              |

| Gate Capacitance ( $Cg = \varepsilon_{OX}WL/t_{gOX}$ )                           | 1/S              |

| Transistor on-resistance                                                         | 1                |

| Intrinsic gate delay( $t=C_g\Delta v/I_{av}=R_{tr}C_g$ )                         | 1/\$             |

| Power-dissipation per gate (P=IV)                                                | 1/S2             |

| Power-delay product per gate (P*t)                                               | 1/\$3            |

| Area per device (A=WL)                                                           | 1/S <sup>2</sup> |

| Power-dissipation density (P/A)                                                  | 1                |

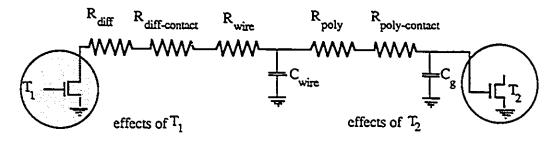

Scaling effects occur on both interconnection capacitance and resistance. With increasing chip dimensions, parasitic interconnection capacitance dominates the gate capacitance, and the speed improvement expected from simple scaling does not apply to circuits that drive global communication lines. Simple scaling assumes a reduction in the capacitive loading due to wires. This is true, locally, when a circuit is connected only to its neighbors, but for circuits that drive long global wires, the capacitive loading actually increases because chips get bigger with time. Large capacitive loads also increase power consumption.

Table 2.2. Scaling effects on interconnection

| Parameter                                                                             | Scaling factor                 |

|---------------------------------------------------------------------------------------|--------------------------------|

| Cross sectional dimension (Wint, Hint, Wsp, tox)                                      | 1/S                            |

| Resistance per unit length (Rint=rint/WintHint)                                       | s <sup>2</sup>                 |

| Capacitance per unit length(Cint=eoxWint/tox)                                         | 1                              |

| RC constant per unit length (Rint Cint)                                               | S <sup>2</sup>                 |

| Local interconnection length (l <sub>loc</sub> )                                      | 1/S                            |

| Local interconnection RC delay(Rint Cint l <sup>2</sup> loc)                          | 1                              |

| Die size (D <sub>C</sub> )                                                            | Sc                             |

| Global interconnection length (lint)                                                  | Sc                             |

| Global interconnection RC delay(R <sub>int</sub> C <sub>int</sub> l <sup>2</sup> int) | s <sup>2</sup> Sc <sup>2</sup> |

| Transmission line of flight (lint/vc)                                                 | Sc                             |

S, S<sub>C</sub>: Scaling factor for device dimension and chip size respectively

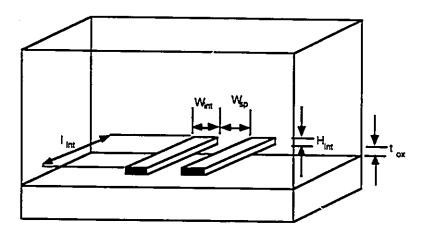

In addition to large capacitance loads resulting from long interconnections, the resistance of the lines also becomes a major concern. Simple scaling of local and global interconnections is summarized in Table 2.2 which uses interconnection parameters shown in Fig 2.4.

Figure 2.4 Interconnection parameters.

In addition to scaling down the size of individual devices, chip size has increased continuously throughout the evolution of ICs. This can be modelled as a chip scaling factor  $S_C$ , which represents the increase in the length of the one side of a die. As a result, global interconnection length,  $l_{int}$ , increases by  $S_C$ , and the distributed RC delay of long lines degrades by  $S^2S_C^2$ .

When the width of the wire is increased, resistance drops, but the capacitance increases by the same amount. Consequently, the RC constant cannot be reduced by adjusting mask dimensions and is solely determined by the technology [4][3]. This is a very important factor in determining the limitations in using long wires in a VLSI circuit and future improvements in S and S<sub>C</sub> will mean rapid increase in the interconnection delay.

#### 2.8 A MODEL FOR ULSI TECHNOLOGY

As shown in Table 2.1 and 2.2, scaling reduces not only the dimensions of a device but also increases its speed. On the other hand, for interconnections, the global interconnection RC constant per unit length is increased by  $S^2S_c^2$ . Thus, with the evolution of technology, device delay is decreasing but interconnection delay is increasing; the wire delay controls the speed of the computations rather than the device delay [3]. In a ULSI environment, long wires pay double penalty - both silicon area and propagation delay increase. The computational model we choose for ULSI has to reflect these scaling effects. An important paper in this area is by Zhou et al [87].

The fact that the dimensions for interconnections do not scale is important in wire delay assumption. For example in  $3\mu$  and  $1.2\mu$  technologies, the metal 1 widths (3 and 2.0 microns, respectively, obtained from Canadian Microelectronics Corporation design rules) are not even scaled by a factor of 2 as would be expected using simple scaling assumptions

[10]. In sub micron technologies, a minimum size transistor of  $0.1\mu$  device width can not directly drive a metal width of  $1\mu$ ; this limits the driving capability of devices and also does not utilize the maximum scaling effect. Thus, as the technology evolves, the chip area is further dominated by wire area and propagation time by the wire delay.

We have mentioned earlier that Bilardi et al [7] defined a figure of merit  $\gamma = \frac{cl}{C0}$  where c is the capacitance of wire per unit length, l is the length of wire and C<sub>0</sub> is the capacitance of the active device. As the technology advances, the capacitance per unit length of the wires in a multilevel interconnection scheme approaches a lower limit of 2 pF/cm with SiO<sub>2</sub> as the dielectric material [71]. In practice approximately 3 pF/cm is achieved, whereas a minimum size gate capacitance is 2 x 10<sup>-3</sup>pF [4]. This yields a high value for  $\gamma$ , in the range of 10<sup>3</sup>, as shown in Bilardi et al. for a minimum wire length of 1 cm. For such value of  $\gamma$ , the wire delay of Chazelle et al. and Seitz's model is expected to be predominant [7]. Therefore, we will use Chazelle's linear model for calculations of wire delay. In fact, for values of  $\gamma > 10^3$ , the nonlinear effect starts to become important. We are actually being conservative when we assume the capacitive model. If we assume the diffusion effect, where the delay is proportional to the square of wire length, the effect of wire delays degrade the performances of VLSI circuits even more drastically.

Apart from the fact that ULSI circuits should have a low value for performance metric (e.g.,  $AT^2$ , ATP) the regularity of interconnection in a ULSI array is very desirable from a technological point of view. As pointed out by Sasaki, the performance measure for ULSI technologies should have: function per unit area, throughput (or performance) per function, and the regularity factor of the circuit itself [65]. Systolic arrays are ideally suited for ULSI technologies, so far as the regularity factor is concerned, and in chapters 3 and 4 we show that they also have attractive performance metrics.

We summarize that in modelling VLSI/ULSI circuits, the grid model is applicable, the performance metric AT,  $AT^2$ , ATP and AP are useful and it is appropriate to use the capacitive model to estimate time.

#### 2.9 SUMMARY

In this chapter we have introduced the subject of modelling for VLSI/ULSI circuits. An extensive review has been performed on models that have previously been proposed to predict area and time performance limits for large systems on silicon. As technology improves, devices scale, and the effect of such scaling on performance metric has also been explored. We have determined that the capacitive model is most appropriate for computing time metric, and that the grid model most suitable for computing area metric. We will use a variety of cost functions, involving both of these metric, in our following comparison studies.

# **CHAPTER**

3

ULSI SYSTOLIC

ARRAYS FOR

ROUTING AND FAST

COMPUTATIONS

#### 3.1 INTRODUCTION

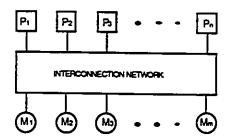

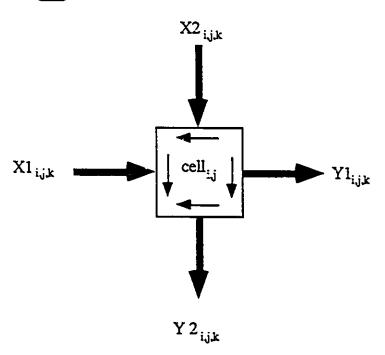

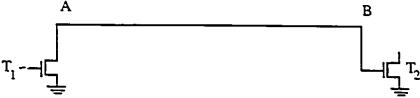

In a supercomputer there are many processors and many memory modules. During any computation, the processors have to communicate data to other processors and to different memory modules. It is very important that this communication be carried out as fast as possible since this is often the bottleneck in determining the throughput capabilities of a multiprocessor system. Interconnection networks are used to communicate signals from n sources (processors) to m destinations (processors and/or memories). A general model for an interconnection network for communication between processors and memory modules is shown in Figure 3.1. Typically, an interconnection network consists of several stages, where each stage consists of a number of 2x2 switches.

Figure 3.1. Concurrent processing systems.

When a processor wishes to communicate with another processor or memory, the communication time varies, depending on which processor is the source for this communication and which is the destination processor. In designing an interconnection network, a very important goal is to reduce the worst case communication time for any source/destination pair. In pipelined systems, the pipeline period is often more important than the latency time. In such cases, we typically connect latches to every switch in order to reduce the pipeline period.

Implementing such interconnection networks in VLSI has been a basic problem for some time and has been studied thoroughly by many researchers [19][25][30][42][78][82]. The communication architectures of most popular interconnection networks are referred to as 'high wire organizations' [82], since a significant amount of communication layout area between stages is needed for such networks.

In ULSI, these high wire organizations not only pay penalties in terms of area but also in terms of propagation delay, since long wires, as explained in chapter II, imply significant communication delays. Evolving ULSI technology permits us to design larger routing networks (i.e. a network which can handle more inputs) on a single monolithic piece of silicon. In this chapter we will prove that, based on the capacitive model chosen in chapter II, high wire organizations are no longer likely to be efficient. Further, we will show that a straight forward "cross bar" type routing network, proposed many years earlier, actually has asymptotic performance measures superior to those of routing networks requiring fewer switches.

In this chapter we also analyze the performance of a number of standard routing networks using the capacitive model. Then we present a "systolicized" version of an interconnection network which has been proposed by Kautz in 1968 [28]. We compare the performance metric of this network to those of the standard networks found in recent literature. In

Chapter I, we briefly reviewed the problem of self routing. In this chapter, we look at a simple sorting array which has the same intercell communication architecture as the Kautz array. This array can be readily used for self routing and has better performance, compared to other arrays for perimeter sorting, once we take the intercell delay into account using the capacitive model.

# 3.2 ANALYSIS OF SOME INTERCONNECTION NETWORKS

Interconnection networks are classified either by the number of stages (i.e., single stage also called a recirculating network or multistage networks) or by their function (i.e., blocking, rearrangeable or nonblocking networks) [17][26].

In blocking networks, simultaneous connections of more than one path may result in conflicts in the use of network communication links. An example of a blocking network is the perfect shuffle network. A network is rearrangeable if it can perform all possible connections between inputs and outputs by rearranging its existing connections so that a connection path for a new I/O pair can always be established. An example of the rearrangeable network is the Benes network. A network that can handle all possible connections without blocking is called a nonblocking network. The Clos network is a nonblocking network.

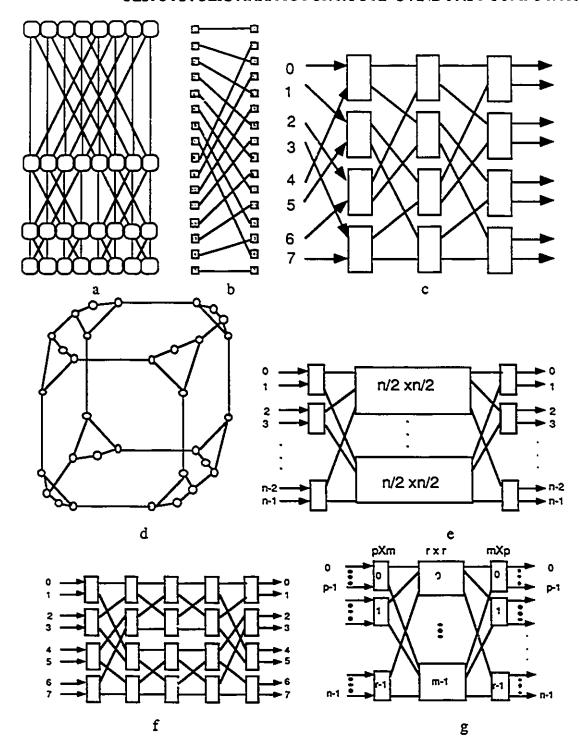

A number of well known interconnection networks are shown in Fig 3.2. These interconnection networks have been described in [13][17][21][26][38][52][53][56][57][58] [59][70][72][81][85]. Every network that we consider has n inputs and n outputs, where  $n=2^k$ , for some k. Each node in an interconnection network consists of a 2X2 switch and buffers to store the output of this switch.

Figure 3.2 a. Butterfly network for n=8, b.Shuffle Exchange for n=16, c. Recirculating Shuffle exchange network for n=8, d. Cube connected network for n=32, e. Benes network, f. Benes network for n=8 & g. Clos network.

This ensures that these networks are fully pipelined so that, with every clock pulse, one set of data may be applied to the input of the interconnection network. After the requisite latency period, determined by the number of stages of cells each input bit has to pass through and the delay per stage, the output corresponding to a given set of inputs is available.

The delay D in a given stage is determined by the delay of the switch and the delay due to communication from the output of that stage to the input of the next stage. We assume that the system clock we use generates clock pulses at a frequency such that the time period is greater than the worst value of D. Since the worst value  $D_{\text{max}}$  of D is determined by the largest wire length, our pipeline period is taken to be the inverse of  $D_{\text{max}}$ .

In order to realize any given permutation in a rearrangeable network, the setting of each individual 2X2 switch in the network has to be determined externally. As mentioned earlier, determining the switch settings can be a complex problem in its own right. At this point we assume that a separate piece of hardware or software has correctly set the network switches for the desired permutation. When we speak of the latency period T of the network we assume that the switches are already set correctly and the time for setting the switches are not included in estimating T.

Pioneering studies of VLSI circuits and their performance metric took place in late seventies and early eighties. At that point in time, the state of the art in VLSI circuits was such that the synchronous model [8], where the time required for data communication is constant, was quite appropriate. This model is reviewed in Chapter 2 (Section 2.2). We recall that the present state of the art in VLSI/ULSI technology means that much smaller circuit elements are now technologically feasible and that the penalty due to long wires have become more pronounced. This means that the computation of VLSI/ULSI metric should be based on the capacitive model so that the worst case communication delay is

proportional to the maximum length of wire between active areas (Section 2.8). We now look at the ramifications of the capacitive model on the performance metric of several well known interconnection networks, namely Butterfly, Shuffle Exchange, Clos, Benes and Cube Connected Cycles [19][80][82][59][42]. The interesting point about this analysis is that the asymptotic performance metric of well known circuits, in terms of the VLSI/ULSI model we have chosen, have degraded significantly.

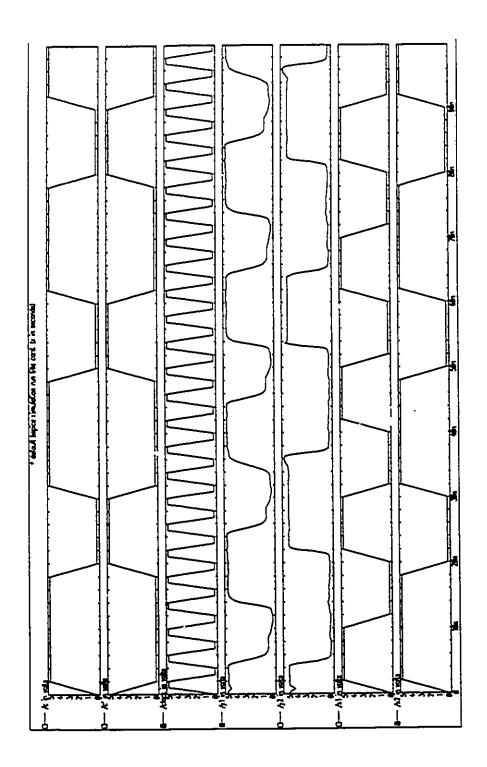

Table 3.1: Area and time complexities of interconnection networks.

|                  | Spa                   | ace/area Comple                       | exity               | Time complexity |                          |                     |  |

|------------------|-----------------------|---------------------------------------|---------------------|-----------------|--------------------------|---------------------|--|

| Topology         | Gate model            | Synchronou<br>s model                 | Capacitive<br>model | Gate<br>model   | Synchro<br>nous<br>model | Capacitive<br>model |  |

| Butterfly        | O(n log n)            | O(n <sup>2</sup> )                    | O(n <sup>2</sup> )  | O(logn)         | O(logn)                  | O(n log n)          |  |

| Shuffle exchange | O(n log n )           | O(n <sup>2</sup> )                    | O(n <sup>2</sup> )  | O(logn)         | O(logn)                  | O(n log n)          |  |

| ccc              | n                     | O(n <sup>2</sup> /log <sup>2</sup> n) | $O(n^2/\log^2 n)$   | O(logn)         | O(logn)                  | O(n log n)          |  |

| Benes<br>network | O(n log n)            | O(n <sup>2</sup> )                    | O(n <sup>2</sup> )  | O(logn)         | O(logn)                  | O(n log n)          |  |

| Clos<br>Network  | O (n <sup>1.5</sup> ) | O(n <sup>2</sup> )                    | O(n <sup>2</sup> )  | O(1)            | O(n)                     | O(n )               |  |

In Table 3.1 we present the area and time complexities for the interconnection networks shown in Fig 3.2. In this table we use three of the models mentioned in chapter 2. The first is the gate count model where the number of logic gates and storage devices is taken to be a measure of the area complexity of the circuit. The second model is the synchronous model where the delay in communication is taken to be independent of the wire length. The third model is the capacitive model where the delay in propagation is linearly proportional

to the length of the wire. The reason for changes in the VLSI area/time complexities when we go from one model to another is that each model makes different cost assumptions.

In the gate model, the area of the active device is the factor which determines cost. On the other hand, in the synchronous model, the actual silicon area to fabricate the circuit determines cost. This area includes both areas for the active devices as well as the areas for the interconnections between active areas. The butterfly network, the shuffle exchange network and the Benes network require  $O(n \log n)$  space complexity and  $O(\log n)$  time complexity in the gate model. The VLSI implementation considerations change the area complexity of these networks from  $O(n \log n)$  to  $O(n^2)$  in the synchronous model. The time has not changed since this model ignores the wire delay. As explained in Chapter 2, we are now approaching the situation where this delay cannot be ignored for high wire organizations. The degradation of the time complexity, when this delay is taken into consideration, is very important and has been shown in the last column of table 3.1.

We will formally prove the correctness of the complexity values in the entries of Table 3.1 using Theorem 3.1.

#### Theorem 3.1:

If the capacitive model for VLSI is used, the areas (A), times (T), pipelined periods (P) and the performance metric (AT, ATP, AT<sup>2</sup>) of the networks shown in Fig 3.2 are as shown in Tables 3.1 and 3.2.

# Proof:

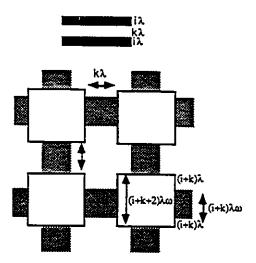

We will consider only the case of the Butterfly network here since the analyses for other networks are quite similar. We will use design constrains of the type described in [44]. Let us consider the geometrical structure of the butterfly network. We assume that  $\lambda$  is the minimum feature size allowed by the technology. We will measure all lengths in terms of

$\lambda$ . Let us assume that, all processing elements or switches are squares which occupy at least LxL area, i.e.,  $O(L^2)$ , where L is a side of the switch. Each side of the switch has a maximum of  $\omega$  inputs or outputs (for this network  $\omega$  is 2). Connections laid out in metalization layers need a minimum line width of  $i\lambda$  (3 $\lambda$  for Mead and Conway design rules in 3 $\mu$  technology) and a minimum distance between adjacent lines (minimum pitch) of k $\lambda$  units, where i and k are suitably chosen numbers (k=3 $\mu$  for Mead and Conway design rules). A data path containing  $\omega$  parallel communication lines requires a width of (i+k) $\lambda\omega$  units. Each cell has two inputs and outputs. Therefore, L is at least  $\omega$ (i + k) $\lambda$  units and a lower bound on the processor area is ((i+k) $\lambda\omega$ )<sup>2</sup>.

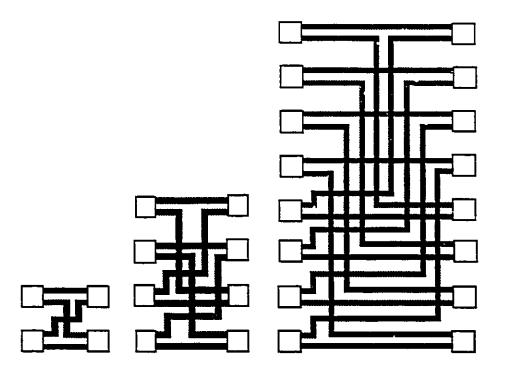

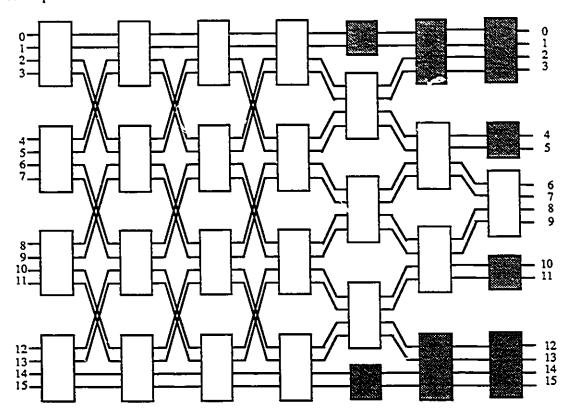

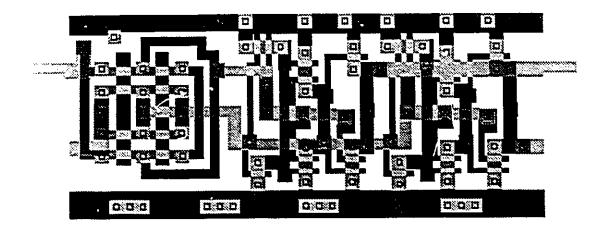

By using Mead and Conway design rules, area-efficient layouts of Butterfly networks for n = 2, 4 and 8 are shown in Figure 3.3. As expected, the area for interconnection between switches increases exponentially as n increases (Figure 3.3 b).

We will use  $P_{r,q}$  to denote the qth switch in the rth stage where the first and last switches in any stage are switches 0 and n-1. Let us consider the last stage s of an n input butterfly network, where  $s = \log \iota$ . (and we assume that n is a power of 2). The output of the switch  $P_{s-1,j}$  has to be connected to switches  $P_{s,j}$  and  $P_{s,n/2+j}$  switch, for all j,  $0 \le j < n$ . We will term the connection from  $P_{s-1,j}$  to  $P_{s,j}$  ( $P_{s,n/2+j}$ ) as the first(second) connection. Even though, the first connection from switch  $P_{s-1,j}$  connects the output of  $P_{s-1,j}$  to a cell in the same row, the length of the wire is determined by the other wires. The second connection passes through n/2 switches in vertical direction and in horizontal direction it has to pass through n-1 other wires. Therefore, the minimum length of this wire (in using  $\lambda$  as the unit) is

$$1/2 (L+k)n + (i+k)\omega (n-1)$$

The length of the array is (L+k)n and the width is  $(i+k)\omega$  (n-1). Thus the interconnection area of this stage is

$$(L+k) n * (i+k)\omega (n-1) \approx O(n^2).$$

We are not considering the area of the cell since this will add a linear term to the total area of this stage. The total wire area of the network is:

$$\sum_{i=1}^{(n)} O(n^2)$$

Therefore the area is O(n<sup>2</sup>). The longest wire length is

$$(n/2) (L+k) + (i+k)\omega (n-1) \approx O(n)$$

.

The pipeline period is determined by the maximum delay requires for the longest time of the network. Thus the pipeline period is O(n).

Figure 3.3 a. The layout for a mesh interconnection, in which the width between two switches has a fixed distance, each bus consists of  $\omega$  wires of width  $(i+k)\lambda$ .

Figure 3.3 b: Layouts for the modules n=2, 4 and 8 points butterfly networks, the distance between two consecutive stages depends upon the number of inputs of the module.

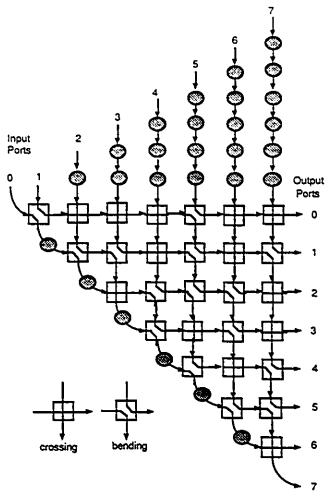

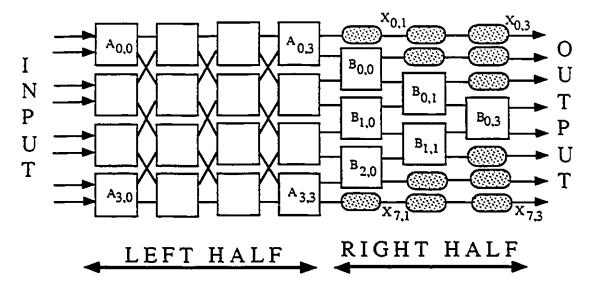

# 3.3 A SYSTOLIC ARRAY FOR ROUTING

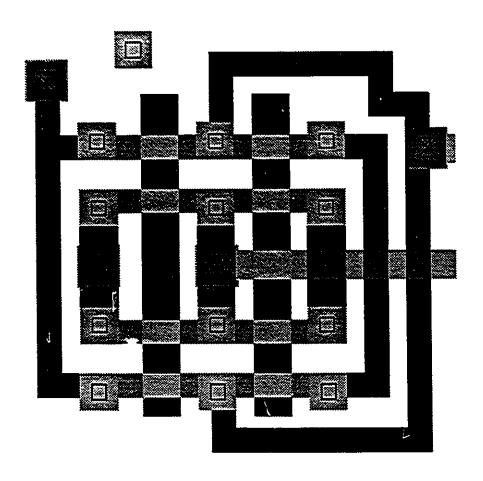

A cellular interconnection array was suggested by Kautz et al. [28]. In this part of the chapter, we study a very similar array which is obtained by a minor modification of the Kautz array. The "systolicized" modification of Kautz's interconnection array that we study is shown in Fig 3.4 where each 2X2 switch in a cell has been augmented by two buffers to store the two outputs of the switch. This ensures that the array is completely pipelined for maximum throughput. The setting of the switch in a cell determines whether the cell is in a 'crossing' or in a 'bending' mode. These two modes of a cell are depicted in Fig 3.4. Each shaded oval box in the diagram represents a single delay element. These

delay elements ensure the integrity of the wave-front at any instance of time. Kautz has suggested other realizations of interconnection arrays but we have omitted those designs since they all have identical asymptotic values of area time metric. In our discussions, we will refer to this array as the K-array. In order to realize any given permutation, the setting of each individual 2X2 switch has to be determined externally, as we did in the case of the high wire interconnection networks.

We now determine the asymptotic bounds for the area, latency time and pipeline period of this array in order to compare different performance metric of the K-array with those of interconnection networks, with high wire organization, that were discussed in Theorem 3.1.

# Theorem 3.2:

The K-array with 'n' inputs requires

i. Area (A) of the network is  $O(n^2)$

ii. Time (T) required for routing is O(n)

iii. The pipelined period (P) of this network is O(1).

# Proof:

The array contains  $(n^2 - n)/2$  cells and the area per cell is constant. Each cell is connected to neighboring cells alone, therefore the area for interconnections per cell is constant. The area of the array is  $(n^2 - n) A_{cell}/2$  where  $A_{cell}$  is the area of a single cell along with the area for its interconnections to neighboring cells. Each cell has a switch which can be set into a crossing or bending operation in a constant time O(1). The array requires n clock cycles to produce the output corresponding to a given set of inputs. Each cell is connected only to four of its nearest neighbors and hence uses a constant wire length for communication. Thus the pipeline period is O(1).

Figure 3.4. Triangular array for permutation  $\begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 \\ 7 & 4 & 6 & 3 & 5 & 0 & 2 & 1 \end{pmatrix}$ .

Table 3.2 (see the end of this chapter) shows the performance metric AT,  $AT^2$ , AP and APT of the butterfly network, the shuffle exchange network, the cube connected cycle, the Benes network and the Clos network together with the performance of the K-array. It is interesting to note that the cube connected cycle (CCC) is a very efficient structure when we use the metric of AT. The CCC, in a sense, tries to compromise between a locally connected structure and a high wire organization. As a result, the VLSI area for the CCC is very low. As pointed out in [35], the evaluation of a systolic array is quite dependent on what the user wants.

It is important to note that the k-array outperforms the others in the metric AP and APT. The Clos network also provides low values in the metrics AT,  $AT^2$ , but higher values in the AP and APT metrics.

# 3.4 SORTING NETWORKS FOR SELF ROUTING

A major problem in using a nonblocking interconnection network is to determine the switch settings for arbitrary permutations. It has been shown [50] that this is non trivial and takes significant time if we use a single processor. It is also shown that an SIMD machine may be used to determine the switch settings. In a mesh connected machine with  $\sqrt{N} \times \sqrt{N}$  processors, it is possible to determine the switch settings in time  $O(\sqrt{N})$ . To avoid the additional overhead associated with this computation, "self routing" MINs have been suggested [50]. It is important to note that self setting MINs suggested in the literature only allow specific, rather than general, routing.

As mentioned above, we will discuss a straight forward method for implementing nonblocking interconnection networks using sorting networks. This approach allows us to realize a self-routing interconnection network where the comparators in the sorting array determine the switch settings in individual cells of the routing array itself.

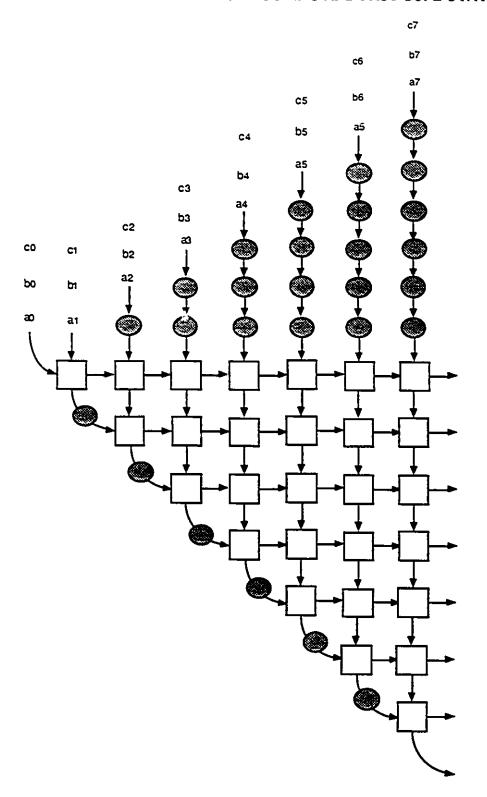

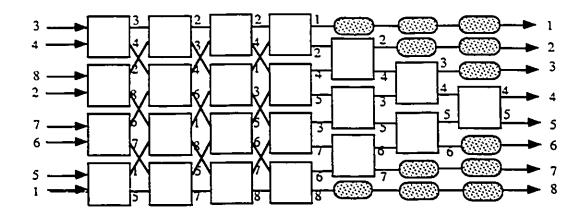

In this approach, we attach destination tags to each signal that we wish to communicate. An example is shown in Fig 3.5. To obtain the permutation  $\begin{pmatrix} 0 & 1 & 2 & 3 \\ 3 & 2 & 0 & 1 \end{pmatrix}$ , input<sub>0</sub> has to be  $3x_0$  where  $x_0$  is the bit to be communicated to output3 and so on. As shown in Fig 3.5, the sorting network generates outputs so that  $x_2$  is obtained from output<sub>0</sub>,  $x_3$  is obtained from output1 etc.

Fig 3.5 Sorting network for self routing.

A number of schemes for sorting have been proposed for implementation in VLSI technologies [14][69][78][82]. Each cell in these sorting arrays has a comparator and a switch. Thus each cell in any of these schemes is identical to the cell used in Fig 3.4 except that there is a comparator in each cell that compares the two inputs to the cell. If we use the convention followed in Figure 3.4 and, for a given cell at a particular instance of time, the input to the cell from the left is less than (greater than or equal to) the input from the top, the switch in the cell is set in the bending (crossing) mode.

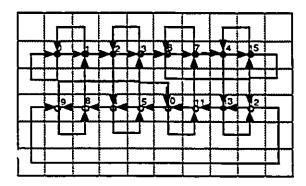

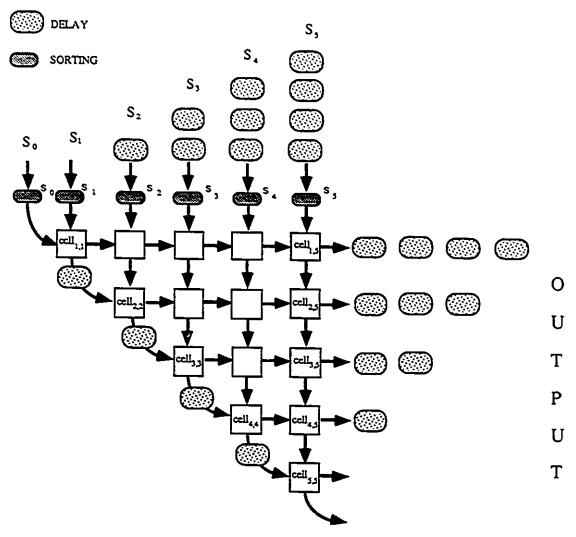

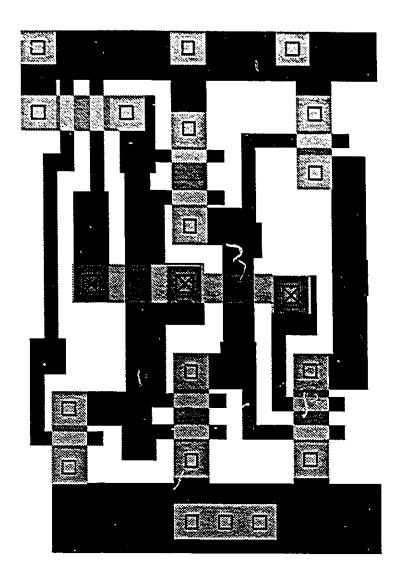

The architecture we investigate is adopted from [69] and is shown in Fig 3.6. We will term this the *S-array*. Each cell in the array receives two inputs - one vertical (or from the top) and one horizontal (i.e., from the left). Each cell compares the horizontal and the vertical inputs and routes the larger (smaller) input to a latch associated with the vertical (horizontal) output. It is important to note the similarity of this array to that described in 3.3.

# Theorem 3.3:

In an S-array for sorting n elements,

- i. Area (A) of the network is  $O(n^2 \log n)$

- ii. Time (T) required for computation is  $O(n \log n)$

- iii. The pipelined period (P) of this network is  $O(\log n)$

# Proof:

The array contains  $(n^2 - n)/2$  cells (same as the K-array). Each cell has to compare two numbers each containing log n bits. Thus the size of each cell is  $O(\log n)$  bits. The array requires n clock cycles (same as the K-array). Each clock should be long enough to compare 2 numbers each containing log n bits. Thus the pipelined period is  $O(\log n)$ .

As discussed by Nassimi [50], the computational complexity in setting the switches in a multistage interconnection network is very high. To our knowledge, there is no analysis of the VLSI area required to communicate the switch settings to individual switches. Intuitively, this area is likely to be considerable. Our solution, using a sorting network to determine the switch settings, completely avoids this problem. It is interesting to note that the S-array, for the metric AP and ATP, outperforms standard arrays. For the metric AT and  $AT^2$ , the S-array has complexity measures comparable to those of the  $\Omega$  network, the butterfly network and the Benes network. The S-array is superior, so far as the asymptotic bounds are concerned, to existing sorting networks (e.g., the bitonic sorting network) [5][31]. The self routing property of the S-array, therefore, is not "costly" in terms of performance metric. A comparison between Batchers sorting network with a S-array is shown in Table 3.3.

It is important to remember, however, that each cell in the S-array contains a comparator which compares (log N) bit numbers. Therefore, the cells are larger than those used in networks where no facility for self routing exists. This means that the superior performance of the S-array will be evident only for larger values of N compared to the value of N for which the K-array becomes superior to structures involving high wire organizations.

Fig. 3.6. Triangular array for sorting. Shaded areas represent delay elements.

# ULSI SYSTOLIC ARRAYS FOR ROUTING AND FAST COMPUTATIONS

Table 3.2a: Area & Time Complexities of interconnection networks.

|                     | Spa                  | ace/area Compl                       | Time complexity                      |          |          |            |

|---------------------|----------------------|--------------------------------------|--------------------------------------|----------|----------|------------|

| Topology            | LSI                  | VLSI                                 | ÜLSI                                 | LSI      | VLSI     | ULSI       |

| Buttertly           | O(n log n)           | O(n <sup>2</sup> )                   | O(n <sup>2</sup> )                   | O(log n) | O(log n) | O(n log n) |

| Shuffle exchange    | O(n log n)           | O(n <sup>2</sup> )                   | O(n <sup>2</sup> )                   | O(log n) | O(log n) | O(n log n) |

| CCC                 | O(n)                 | $O\left(\frac{n^2}{\log^2 n}\right)$ | $O\left(\frac{n^2}{\log^2 n}\right)$ | O(logn)  | O(log n) | O(n log n) |

| Benes<br>network    | O(n log n)           | O(n <sup>2</sup> )                   | O(n <sup>2</sup> )                   | O(log n) | O(log n) | O(n log n) |

| Clos<br>Network     | O(n <sup>1.5</sup> ) | O(n <sup>2</sup> )                   | O(n <sup>2</sup> )                   | O(1)     | O(n)     | O(n)       |

| Systolic<br>k-array | O(n <sup>2</sup> )   | O(n <sup>2</sup> )                   | O(n <sup>2</sup> )                   | O(n)     | O(n)     | O(n)       |

Table 3.2b: Performance measures of interconnection networks.

| Topology            | Area A                               | Time T   | Pipeline<br>Period P | AT                                 | $AT^2$                               | AP                                   | ATP                                |

|---------------------|--------------------------------------|----------|----------------------|------------------------------------|--------------------------------------|--------------------------------------|------------------------------------|

| Butterfly           | O(n <sup>2</sup> )                   | O(nlogn) | O(n)                 | O(n <sup>3</sup> logn)             | O(n <sup>4</sup> log <sup>2</sup> n) | O(n <sup>3</sup> )                   | O(n <sup>4</sup> logn<br>)         |

| Shuffle exchange    | O(n <sup>2</sup> )                   | O(nlogn) | O(n)                 | O(n <sup>3</sup> logn)             | O(n <sup>4</sup> log <sup>2</sup> n) | O(n <sup>3</sup> )                   | O(n <sup>4</sup> logn              |

| ccc                 | $O\left(\frac{n^2}{\log^2 n}\right)$ | O(nlogn) | O(n)                 | $O\left(\frac{n^3}{\log n}\right)$ | O(n <sup>4</sup> )                   | $O\left(\frac{n^3}{\log^2 n}\right)$ | $O\left(\frac{n^4}{\log n}\right)$ |

| Benes<br>network    | O(n <sup>2</sup> )                   | O(nlogn) | O(n)                 | O(n <sup>3</sup> logn)             | O(n <sup>4</sup> log <sup>2</sup> n) | O(n <sup>3</sup> )                   | O(n <sup>4</sup> logn              |

| Clos<br>Network     | O(n <sup>2</sup> )                   | O(n)     | O(n)                 | O(n <sup>3</sup> )                 | O(n <sup>4</sup> )                   | O(n <sup>3</sup> )                   | O(n <sup>4</sup> )                 |

| Systolic<br>k-array | O(n <sup>2</sup> )                   | O(n)     | O(1)                 | O(n <sup>3</sup> )                 | O(n <sup>4</sup> )                   | O(n <sup>2</sup> )                   | O(n <sup>3</sup> )                 |

# ULSI SYSTOLIC ARRAYS FOR ROUTING AND FAST COMPUTATIONS

Table 3.3: Performance measures of sorting networks.

| Topology                      | Area A                               | Time T                               | Pipeline Period P                    | AT                                   |

|-------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| Batcher<br>sorting<br>network | O(n <sup>2</sup> logn)               | O(n log <sup>2</sup> n)              | O(n logn)                            | O(n <sup>3</sup> log <sup>3</sup> n) |

| Systolic<br>S-array           | O(n <sup>2</sup> log n)              | O(nlog n)                            | O(log n)                             | $O(n^3 \log^2 n)$                    |

| Topology                      | AT2                                  | AP                                   | ATP                                  |                                      |

| Batcher<br>sorting<br>network | O(n <sup>4</sup> log <sup>5</sup> n) | O(n <sup>3</sup> log <sup>2</sup> n) | O(n <sup>4</sup> log <sup>4</sup> n) |                                      |

| Systolic<br>S-array           | $O(n^4 \log^3 n)$                    | $O(n^2 \log^2 n)$                    | O(n <sup>3</sup> log <sup>3</sup> n) |                                      |

# 3.5 SUMMARY

In this chapter we have analyzed a variety of interconnection networks and sorting networks with the goal of providing a comprehensive comparison study for implementation in the ULSI medium.

A table has been generated that compares several 'area efficient' routing networks with area and time complexities using the three models: gate model, synchronous model, capacitive model. A systolic routing array, modified from an existing array, has been introduced. We have shown that this array outperforms the comparison arrays in metric AP and APT.

We have also introduced a simple technique to solve the major problem of determining switch settings for nonblocking interconnection networks. This approach has allowed us to realize a self-routing interconnection network, rather than the more usual globally controlled network. This S-array is shown to outperform existing sorting networks in a detailed comparison study.

# **CHAPTER**

4

SYSTOLIC ARCHITECTURES

WITH CELLS OF

CONTROLLABLE

COMPLEXITY

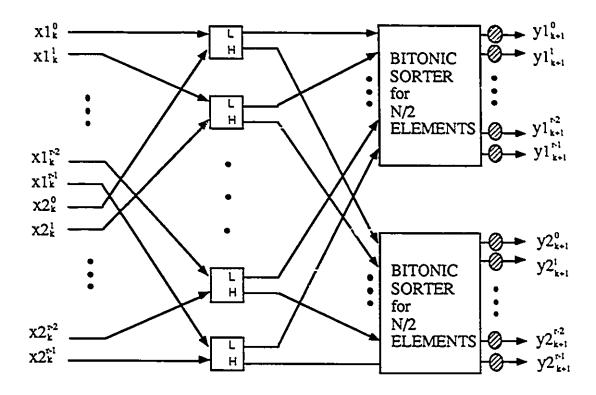

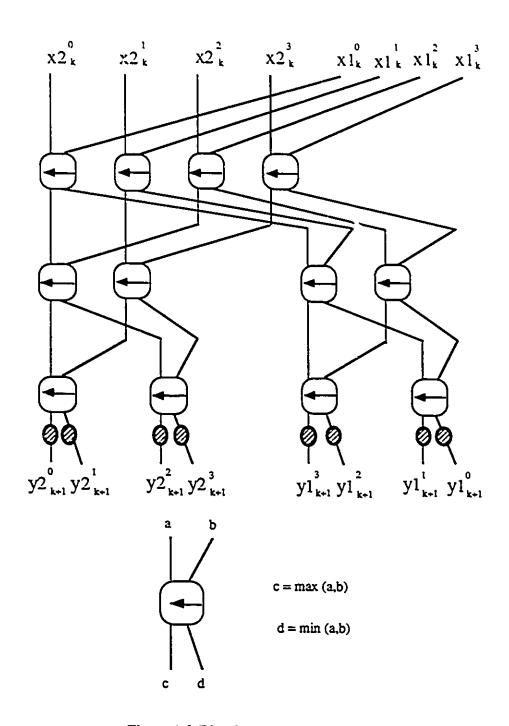

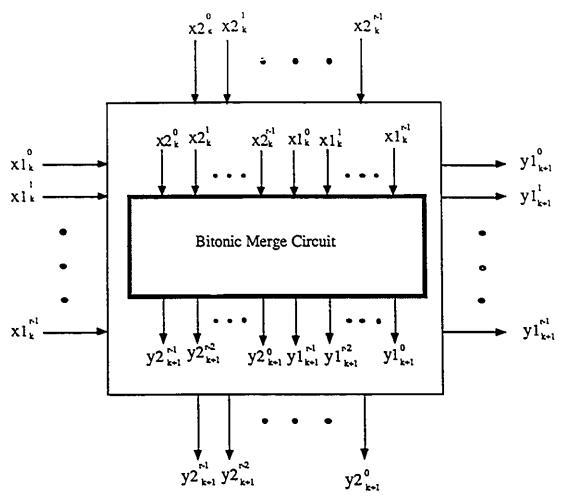

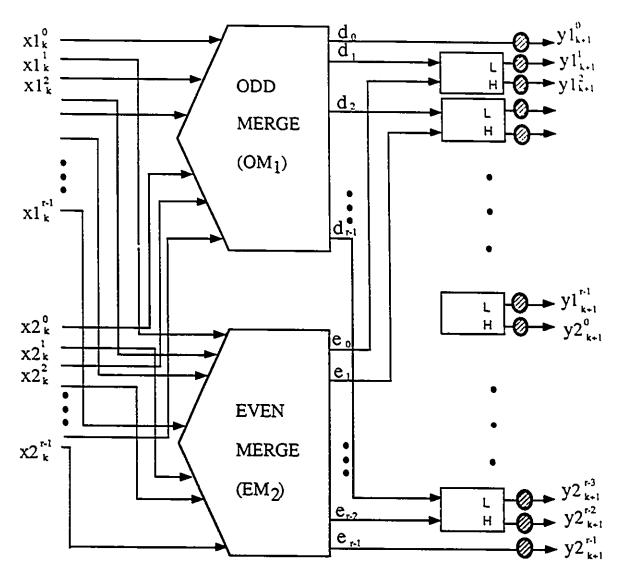

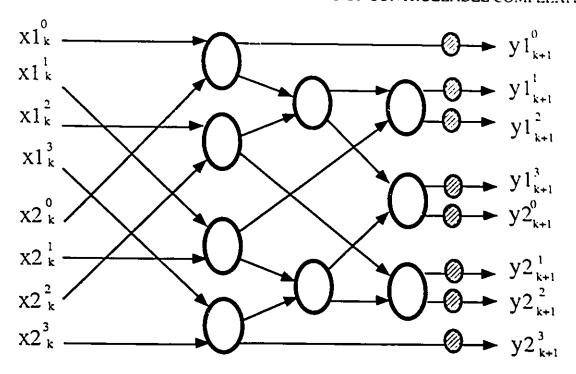

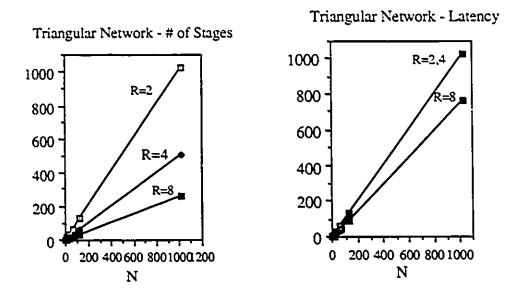

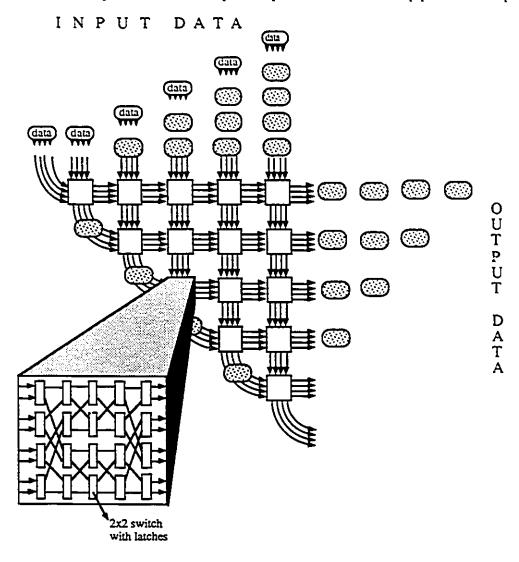

# 4.1 INTRODUCTION