# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1-1-1964

# A tunnel diode phase-locked oscillator.

Philip H. Alexander University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

# **Recommended Citation**

Alexander, Philip H., "A tunnel diode phase-locked oscillator." (1964). *Electronic Theses and Dissertations*. 6340.

https://scholar.uwindsor.ca/etd/6340

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# A TUNNEL DIODE PHASE-LOCKED OSCILLATOR

BY

# PHILIP H. ALEXANDER

# A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario

1964

# UMI Number: EC52520

# INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC52520 Copyright 2008 by ProQuest LLC. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346

Approved

Szchabok -P.A.V. Thomas Smith b.

109862

# ABSTRACT

A study of the dynamic lock characteric of the first and second order loops is presented. Conditions are derived for the maximum sinusoidal frequency deviation for which continuous locking is maintained. Verification of these conditions for a second order loop with a perfect high frequency integrator filter is carried out.

A special feature of the system is its use of solid state devices, especially the tunnel diode, in the essential loop components.

ii

#### ACKNOWLEDGEMENTS

The sincerest appreciation of the author is extended to Dr. S. N. Kalra for his generous provision of guidance and encouragement, and for the wealth of practical knowledge which he has made available to this work. Thanks are due also to Mr. Henry Ganczarczyk, without whose assistance and patience, the hardware would never have materialized.

Special thanks are directed to the National Research Council which made possible the execution of this endeavor.

iii

# TABLE OF CONTENTS

| n an | age                                    |

|------------------------------------------|----------------------------------------|

| ABSTRACT                                 | 11                                     |

| ACKNOWLEDGEMENTS                         | 111                                    |

| TABLE OF CONTENTS                        | iv                                     |

| LIST OF ILLUSTRATIONS                    | v                                      |

| Chapter<br>I. INTRODUCTION               | 1                                      |

| II. THE FIRST ORDER PHASE-LOCKED LOOP    | 5                                      |

| The General Phase-Locked Loop Equation   | 5<br>5                                 |

| III. THE SECOND ORDER PHASE-LOCKED LOOP  | 10                                     |

| Imperfect Integrator Loop Filter         | 11<br>14                               |

| IV. SYSTEM DESIGN                        | 16                                     |

| General Considerations                   | 16<br>18<br>20<br>21<br>21<br>25<br>25 |

| V. SYSTEM OPERATION                      | 27                                     |

| Preliminary Operation                    | 28<br>28                               |

| VI. CONCLUSIONS                          | 34                                     |

| REFERENCES                               | <b>3</b> 6                             |

| VITA AUCTORIS                            | 37                                     |

iv

# LIST OF ILLUSTRATIONS

| Figur | e a second de la construcción de la | Page       |

|-------|-----------------------------------------------------------------------------------------------------------------|------------|

| 1.    | Block Diagram of the Basic Phase-Locked Loop                                                                    | 2          |

| 2.    | Power Spectra of Signal and Noise                                                                               | 2          |

| 3.    | Instantaneous Spectra of Signal and Noise                                                                       | 3          |

| 4.    | Viterbi's General Phase-Locked Loop (Modified)                                                                  | 6          |

| 5.    | Phase-Plane Trajectories for a First Order Loop                                                                 | 7          |

| 6,    | Block Diagram of Actual Phase-Locked Loop                                                                       | 17         |

| 7.    | The Tunnel Diode                                                                                                | 19         |

| 8.    | The Complete VCO Circuit Schematic Diagram                                                                      | 22         |

| 9.    | Schematic Diagram of the Mixer Circuit                                                                          | 23         |

| 10.   | Schematic Diagram of the Phase Comparator Circuit                                                               | 24         |

| 11.   | Evolution of the Varicap Bias Network Equivalent Circuit                                                        | <b>2</b> 6 |

| 12.   | VCO Tuning Characteristic                                                                                       | 29         |

| 13.   | Measurement of Dynamic Lock Range Characteristic                                                                | 31         |

| 14.   | Maximum Dynamic Lock Range Characteristic                                                                       | 32         |

v

#### CHAPTER I

#### INTRODUCTION

A phase-locked oscillator is a tuneable electronic power source incorporated into a feedback loop. The system is so arranged that the oscillator signal phase is controlled by the incoming signal phase. When such phase control is evident, the system is said to be "in lock" or "synchronized". If the signal frequency is time-varying, the object of phase-locking is to obtain, at an increased power level, the information contained in the signal phase. If the signal frequency is constant, stability of the output frequency at a higher power level is usually desired.

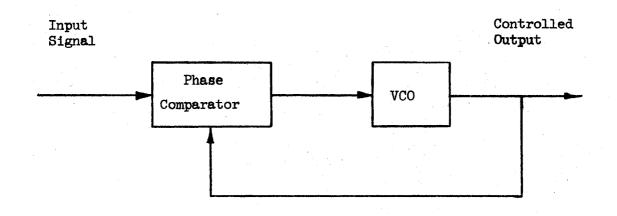

Phase-locking is accomplished by sensing the difference in phase between the signal and the variable frequency local oscillator output, and using this difference to drive the controlled phase closer to the signal phase. The variable frequency is usually voltage-tuned and is commonly referred to as a VCO (Voltage Controlled Oscillator). Its frequency of operation is dependent on a voltage at its input. A measure of the phase difference is obtained by means of a phase comparator or phase discriminator which produces an output voltage dependent on the phase difference between the inputs. These elements are arranged in the feedback loop as illustrated in Fig. 1 to accomplish the desired control.

Automatic phase control offers considerable improvement over conventional methods when applied to the problem of FM detection in the

presence of noise. The major advantage of this technique lies in the properties of the loop as a narrowband filter. As such, the phaselocked loop has a variable centre frequency which automatically tunes to coincide with the desired signal frequency.

Fig. 1 Block Diagram of the Basic Phase-Locked Loop

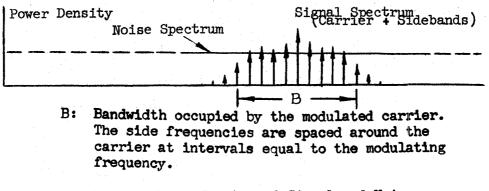

To illustrate this application of phase-locking, consider the detection of an FM signal in the presence of an appreciable amount of noise power. Assuming that in the region of the carrier frequency the noise which interferes with reception is white, the pertinent power spectral densities can be represented in graphical form as in Fig. 2.

Fig. 2 Power Spectra of Signal and Noise.

In order to receive all the significant side frequencies, and thus most of the information transmitted, a conventional FM receiver must have a bandwidth of the order of B. However, the total noise power within this bandwidth may be of the same approximate magnitude, or even greater than the signal power.

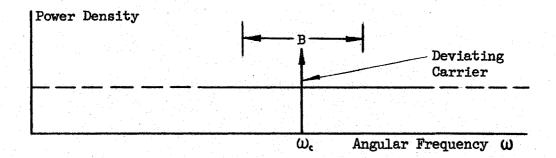

The time-varying properties of these quantities will now be considered. The noise source interfering with the signal can be regarded as a stationary, ergodic random process. The power density of this process is a constant-valued spectrum. The signal is a sinusoidal voltage whose instantaneous frequency is varying over the range B. The signal-to-noise ratio could be improved if a receiver with a narrower bandwidth and a centre frequency that would follow the carrier signal in its excursions in the frequency range B were available. These properties are the functions of the phase-locked loop.

The bandwidth of the loop is determined by the high frequency limitations of the phase comparator and VCO. If, for example, the

Fig. 3 Instantaneous Spectra of Signal and Noise. carrier is modulated at an angular frequency  $\omega_m$  which is beyond this limitation, the loop will not respond. The sideband structure of the resulting power spectrum consists of discrete frequencies spaced at intervals of  $\omega_m$ . Since the loop is not responding, the nearest side

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

frequency must be outside its bandwidth. Thus the net bandwidth of the phase comparator, VCO, and loop filter, if any, is translated to the VCO centre frequency and follows the variations in it.

There are some modifications which may be necessary or expedient in particular systems. One of these is the use of frequency translation of the information to an intermediate frequency (IF) for amplification. Another is the use of frequency multiplication or division in order to lock onto signals which are far removed in frequency from the VCO. Still another is the use of low-pass filters in order to obtain integral compensation within the loop. The first two modifications are unimportant with respect to loop behaviour, but the third determines the order of the differential equation describing the system.

The first and second order phase-locked loops are investigated. Particular concern is paid to the dynamic unlock characteristic of the second order phase-locked loop. The dynamic tracking range of a tunnel diode phase-locked oscillator is compared with the results derived. The experimental data is given for conditions of quite high signal-tonoise ratio (approximately 30 db.). This work is preparatory to a study of the statistical properties of the second order phase-locked loop under threshold conditions (low signal-to-noise ratio).

# CHAPTER II

### THE FIRST ORDER PHASE-LOCKED LOOP

#### The General Phase-Locked Loop Equation

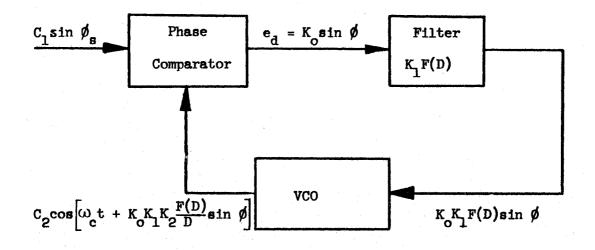

The general block diagram of a phase-locked loop as given by Viterbi<sup>(1)</sup> is repeated in a slightly modified form in Fig. 4.

The VCO frequency shift from  $\omega_c$  is proportional to the input voltage. However, the output quantity of interest is the phase or integral of frequency. Therefore, the output phase is proportional to the integral of the input voltage. This accounts for the factor  $\frac{1}{D}$ which appears in the VCO output phase. The phase comparator output is proportional to  $\sin(\phi_s - \phi_c) = \sin(\phi)$ , i.e.,

$$e_{d} = K_{o} \sin(\phi) = K_{o} \sin[\phi(t) - \omega_{c}t - K \frac{F(D)}{D} \sin\phi]$$

(1)

where  $K = K_{o} K_{1} K_{2}$ .

Differentiating the argument of both sides of equation (1) yields

$$\frac{d\phi}{dt} = \frac{d\phi_s}{dt} - \omega_c - K F(D) \sin\phi_c$$

or

$$\frac{d\phi}{dt} + KF(D)\sin\phi = \frac{d\phi_s}{dt} - \omega_c.$$

(2)

#### The First Order Loop

It is seen from equation (2) that a first order loop will be obtained if F(D) = 1. This is the only one of practical interest although other forms of F(D) would yield a first order equation. If the input frequency is constant equation (2) becomes

$$\frac{d\phi}{dt} + K \sin\phi = \omega_{\rm s} - \omega_{\rm c} = \Omega$$

(3)

| ° <sub>1</sub> : | input signal amplitude (volts)                                                       |

|------------------|--------------------------------------------------------------------------------------|

| ø <sub>s</sub> : | " " phase (radians)                                                                  |

| e <sub>d</sub> : | phase comparator output voltage (volts)                                              |

| к <sub>о</sub> : | phase comparator gain (volts/radian)                                                 |

| ø :              | phase difference between signal and VCO (radians)                                    |

| к <sub>1</sub> : | loop filter gain constant                                                            |

| F(D):            | loop filter transfer function in differential operator notation $(D = \frac{d}{dt})$ |

| к <sub>2</sub> : | VCO gain (radians/sec/volt)                                                          |

| °2 :             | VCO output amplitude (volts)                                                         |

| ω <sub>c</sub> : | centre angular frequency of VCO (radians/sec.)                                       |

|                  | Fig. 4 Viterbi's General Phase-Locked Loop (Modified)                                |

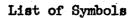

where  $\Omega = \omega_s - \omega_c$  is the tuning error between the VCO centre frequency and the signal frequency. Phase-plane graphs of equation (3) plot as a family of sine curves.

A different curve is obtained for each value of  $\Omega$ . The intersections of a trajectory with the  $\dot{\phi} = 0$  axis are singular points. These points are stable if the trajectories are directed toward them, and unstable if directed away. The direction of phase-plane trajectories is determined by noting that if  $\dot{\phi}$ , the rate of change of  $\phi$  is positive,  $\phi$  must be increasing, and if  $\dot{\phi} < 0$ ,  $\phi$  must be decreasing. This information indicates that stable points a, a', . . . alternate on the  $\phi$  axis with unstable points b, b', . . . (See Fig. 5). Note that the lock points correspond to

$$\phi = \operatorname{Arcsin} \frac{\Omega}{K} + 2n\pi$$

and that no solutions exist for  $\Omega > K$ . Although the loop is not synchronized for  $\Omega > K$ , the average frequency error is not  $\Omega$  but something smaller. This fact is ascertained by inspecting the expression for time interval in the phase-plane

Fig. 5 Phase-Plane Trajectories for a First Order Loop with a Constant Frequency Input

Consider the trajectory resulting from an initial tuning error of  $\Omega_{i}$  (Fig. 5) For the portion of this curve directed from c to d,  $\phi$  is always smaller than on the portion d - e. Therefore, the above integrand is larger on d - e than on c - d. Since  $\phi$  does not change sign anywhere on this trajectory, the integral on c - d is greater than that on d - e. Therefore, the VCO spends more time at frequency errors less than  $\Omega_{1}$  than it does at errors greater than  $\Omega_{1}$ . In other words the time average frequency error is less than  $\Omega_{1}$ .

It is more interesting to investigate the nature of the phase-plane singularities when the input is a sinusoidally modulated FM signal. Define

$\dot{\phi}_{s} = \omega_{c} + \Delta \omega_{cos} \omega_{m}^{t}$

where  $\omega_{\rm m}$  is the frequency of the frequency modulating signal and  $\Delta\omega$  is the frequency deviation of the carrier.

For simplicity, the carrier centre frequency is chosen to be  $\omega_c$ , which corresponds to zero static tuning error.

In this case, equation (3) becomes

$\frac{d\phi}{dt} + K \sin\phi = \Delta\omega\cos\omega_{m}t$ and the lock points are given by

$\phi = \operatorname{Arcsin} \frac{\Delta \omega}{K} \cos \omega_{m} t + 2n\pi \qquad (4)$

It is apparent that time variation of signal frequency corresponds to vertical displacement of the phase-plane trajectories and a corresponding horizontal displacement of the lock points. Equation (4) shows that the loop operates synchronously as long as

$\frac{\Delta\omega}{K}\cos\omega_{\rm mt} \leq 1.$

If  $\frac{\Delta \omega}{K} > 1$ , the above inequality is maintained only during those portions of a modulating cycle in which

# $\cos \omega \mathrm{mt} \leqslant \frac{\mathrm{K}}{\Delta \omega}$

Therefore, the condition for continuous tracking is that

# $\frac{\Delta\omega}{K} \leq 1$

Since this requirement is independent of  $\omega_m$ , for any modulating frequency at which the loop can be described by equation (3), phase-locking can be achieved.

## CHAPTER III

# THE SECOND ORDER PHASE-LOCKED LOOP

The general equation for the phase-locked loop will become a second order equation if the loop filter contains any integrating elements. Three filter configurations will be considered:

a) a perfect low frequency integrator with Laplace transformed transfer function

$$F_1(s) = \frac{s+a}{s}$$

which will be represented in differential operator notation as

$$F_1(D) = \frac{D+a}{D} = 1 + \frac{a}{D}$$

(5)

where a is the cut-off frequency of the filter (in rad./s.)

b) a general imperfect integrator with Laplace transformed transfer function

$$F_2(s) = \frac{s+a}{s+a}$$

which will be represented as

$$F_2(D) = \frac{D+a}{D+a}$$

(6)

where a is the lower and  $\alpha$  is the upper cut-off frequency (in rad./s)

c) a perfect high frequency integrator with Laplace transformed

transfer function

$$F_3(s) = \frac{d}{s+\alpha}$$

which will be represented as

$$F_{3}(D) = \frac{\alpha}{D+\alpha}$$

(7)

where a is the upper cut-off frequency (in rad./s)

# Imperfect Integrator Loop Filter

$F_1$  is directly obtainable from  $F_2$  by letting  $\alpha - 0$ . Substituting the expression for  $F_2(D)$  into the general loop equation (2) gives

$$\frac{d\phi}{dt} + K \frac{D+a}{D+a} \sin \phi = \frac{d\phi_s}{dt} - \omega_c$$

(8)

Again assuming a sinusoidally varying frequency input,

$$\frac{d\phi_{\rm B}}{dt} = \omega_{\rm c} + \Delta\omega\cos\omega_{\rm m}t, \qquad (9)$$

then

$$D\phi + K \frac{D+a}{D+a} \sin \phi = \Delta \omega \cos \omega_m t$$

(10)

$$D^{2}\phi + D\alpha\phi + KDsin\phi + Kasin\phi = (D+\alpha)\Delta\omega cos\omega_{m}t$$

(11)

$$\frac{d^2\phi}{dt^2} + \alpha \frac{d\phi}{dt} + K\cos\phi \frac{d\phi}{dt} + Ka\sin\phi = -\omega_m \Delta \omega \sin\omega_m t + \alpha \Delta \omega \cos\omega_m t (12)$$

Let  $K = 2\zeta \omega_n$ ,  $aK = \omega_n^2$  in order to make (12) similar in form to the general linear second order equation which has the characteristic polynomial

$$D^2 + 2\zeta \omega_n D + \omega_n^2$$

(13)

The similarity becomes evident when equation (12) is linearized by letting  $\sin \phi = \phi$ . Now

$$\frac{d^2\phi}{dt^2} + \frac{d\phi}{dt} (\alpha + 2\zeta\omega_n \cos\phi) + \omega_n^2 \sin\phi = \Delta\omega(\alpha\cos\omega_m t - \omega_m\sin\omega_m t)$$

Normalizing time by letting

$t = \frac{\gamma}{2\zeta \omega_n}$

on the left side of (13) and defining

results in

$$\phi + \frac{\alpha}{2\zeta\omega_n} + \cos\phi + \frac{\sin\phi}{4\zeta^2} = \frac{\Delta\omega}{4\zeta^2\omega_n} 2 (\alpha\cos\omega_m t - \omega_m\sin\omega_m t)$$

(14)

Put  $y = \dot{\phi}$ ,  $x = \phi$ , where x and y are the usual rectangular co-ordinates. Then  $\ddot{\phi} = \dot{y}$  and  $y = \dot{x}$ . Equation (14) becomes

$$\dot{y} + \left(\frac{\alpha}{2\varsigma\omega_{n}} + \cos x\right)y + \frac{\sin x}{4\varsigma^{2}}$$

$$= \frac{\Delta\omega}{4\varsigma^{2}\omega_{n}^{2}} \left(\alpha\cos\omega_{m}t - \omega_{m}\sin\omega_{m}t\right)$$

(15)

Noting that

$$\frac{\dot{y}}{y} = \frac{\dot{y}}{\dot{x}} = \frac{\frac{dy}{d\tau}}{\frac{dx}{d\tau}} = \frac{dy}{dx}$$

and putting (15) into this form

$$\frac{dy}{dx} = -\left(\cos x + \frac{\alpha}{2\zeta\omega_{n}}\right) + \frac{1}{4\zeta^{2}y} \left[\frac{\Delta\omega}{\omega_{n}^{2}}\left(\alpha\cos\omega_{m}t - \omega_{m}\sin\omega_{m}t\right) - \sin x\right] (16)$$

$$= -\left(\cos x + \frac{\alpha}{2\zeta\omega_{n}}\right) + \frac{1}{4\zeta^{2}y} \left[\frac{\Delta\omega}{\omega_{n}^{2}}\sqrt{\alpha^{2} + \omega_{m}^{2}}\cos(\omega_{m}t - \arctan\frac{\omega_{m}}{\alpha}) - \sin x\right]$$

$$-\sin x$$

Since singular points correspond to an indeterminate trajectory slope, they occur for

$$y = 0, x = \operatorname{Arcsin}\left[\frac{\Delta \omega}{\omega_{n}^{2}}\sqrt{\alpha^{2} + \omega_{m}^{2}} \cos(\omega_{m}t - \operatorname{Arctan}\frac{\omega_{m}}{\alpha})\right] \pm 2n\pi$$

or

$$(17)$$

and for

y = 0, x =

$$\pi$$

- Arcsin  $\left[\frac{\Delta \omega}{\omega_n^2}\sqrt{\alpha^2 + \omega_m^2} \cos(\omega_m t - \arctan \frac{\omega_m}{\alpha})\right]^+ 2n\pi$

A suitable transformation of co-ordinates or analogue computer produced phase-plane graphs will indicate which of these sets of points is stable. By extension of the results of the first order loop analysis, it would be expected that one of these sets of points (that including the singular point closest to the origin) would be stable, and the other set unstable. This has been verified for static and linearly

time varying signal frequencies by analogue methods (1,4).

Since the Arcsin does not exist for arguments greater than one, equations (17) indicate that the singular points, and thus loop locking, occur only intermittently for

$$\frac{\Delta\omega}{\omega_{n}^{2}}\sqrt{\alpha^{2}+\omega_{m}^{2}} > 1.$$

(18)

The argument in (17) varies sinusoidally and is less than unity during portions of a modulating cycle as discussed in Chapter 2.

Thus, the criterion for continuous tracking of a sinusoidally varying carrier is that

$$\Delta \omega \leqslant \frac{\omega_{n}^{2}}{\sqrt{\alpha^{2} + \omega_{m}^{2}}} = \frac{\kappa_{a}}{\sqrt{\alpha^{2} + \omega_{m}^{2}}}$$

(19)

By letting  $\alpha \rightarrow 0$ , the criterion for continuous lock is obtained for the loop filter described by

$$F_1(D) = 1 + \frac{a}{D}$$

In this case, continuous tracking is possible if

$$\Delta \omega \leqslant \frac{Ka}{\omega_{m}}$$

(20)

For the condition expressed in (18) it may be possible for the loop to be locked onto the incoming signal for an appreciable part of the period of the modulating frequency if the acquisition or lock-in time is much less than one cycle of the modulating frequency. As the fractional locked time becomes smaller, it is more difficult to find the correlation of the loop output with the set of expected signals in order to extract the information from the signal.

# Perfect High Frequency Loop Filter

The simplest passive integrating filter is one with a transfer function of the form given in equation (7). For this filter, the general equation becomes

$$D\phi + K \frac{\alpha}{D + \alpha} \sin \phi = D\phi_{s} - \omega_{c}$$

(21)

As before, consider an input which has a sinusoidally varying frequency as given in (9) so that

$$D\phi + K \frac{\alpha}{D + \alpha} \sin \phi = \Delta \omega \cos \omega_{\rm m}^{\rm t}$$

(22)

Applying the operator  $D + \alpha$  throughout,

$$D^{2}\phi + \alpha D\phi + K\alpha \sin \phi = (D + \alpha) \Delta \omega \cos \omega_{m} t \qquad (23)$$

$$\frac{d^2\phi}{dt^2} + \alpha \frac{d\phi}{dt} + K \alpha \sin \phi = \Delta \omega \left[ \sqrt{a^2 + \omega_m^2} \cos \left( \omega_m t - \arctan \frac{\omega_m}{\alpha} \right) \right]$$

(24)

This equation is put into standard form by defining

$$\alpha = 2\zeta \omega_n \qquad K\alpha = \omega_n^2$$

The equation is now written as

$$\frac{d^2\phi}{dt} + 2\zeta\omega_n\frac{d\phi}{dt} + \omega_n^2 \sin\phi = \Delta\omega\sqrt{a^2 + \omega_m^2}\cos(\omega_m t - \arctan\frac{\omega_m}{a}) \quad (25)$$

Normalizing as before,

$$4\zeta^{2}\omega_{n}^{2} \overset{2}{\phi} + 4\zeta^{2}\omega_{n}^{2} \overset{2}{\phi} + \omega_{n}^{2} \sin \phi = \Delta \omega \sqrt{\alpha} + \omega_{m}^{2} \cos(\omega_{m}t - \arctan\frac{\omega_{m}}{\alpha}) (26)$$

$$\dot{\phi} = \frac{\Delta \omega \sqrt{\alpha^2 + \omega_m^2} \cos(\omega_m t - \arctan \frac{\omega_m}{\alpha}) - \omega_n^2 \sin \phi}{4\zeta^2 \omega_n^2} - \dot{\phi}$$

(27)

15

Changing to x and y co-ordinates yields in like fashion to the previous case

$$\frac{dy}{dx} = \frac{\frac{\Delta \omega}{\omega_n^2} \sqrt{\alpha^2 + \omega_m^2 \cos(\omega_m t - \arctan\frac{\omega_m}{\alpha}) - \sin x} - 1}{4\zeta_y^2}$$

(28)

Since the singular points are defined in terms of the quantity

Arcsin

$$\left[\frac{\Delta \omega}{\omega_n^2} \sqrt{\frac{2}{\alpha} + \omega_m^2} \cos \left(\omega_m t - \arctan \frac{\omega_m}{\alpha}\right)\right]$$

they exist and the system is continuously in lock for

$$\Delta \omega \leq \frac{\omega_n^2}{\sqrt{\alpha^2 + \omega_m^2}} = \frac{\kappa \alpha}{\sqrt{\alpha^2 + \omega_m^2}}$$

(29)

This result is quite similar to that recorded in expression (19) and the remarks made previously hold for this case as well.

If  $\omega_{m}$  is allowed to approach zero, the static tracking range of the loop is obtained. Thus equation (29) would yield

$\Delta \omega_{\rm dc} = K$

where  $\Delta \omega_{\rm dc}$  is the static tracking range of the phase-locked loop. This equation expresses a design criterion for the loop parameters in terms of the overall loop gain.

# CHAPTER IV SYSTEM DESIGN

## General Considerations

It was decided primarily for convenience that semiconductor devices be used wherever possible in the essential loop circuitry. In general either readily available or easily constructed components were used. The signal frequency was thus chosen to be 100 Mc/s. For frequencies of this order of magnitude inductors generally consist of a few turns of wire which can be mechanically self-supporting. It was felt that the advantages of using components of this simplicity outweigh the disadvantages resulting from such a high frequency of operation.

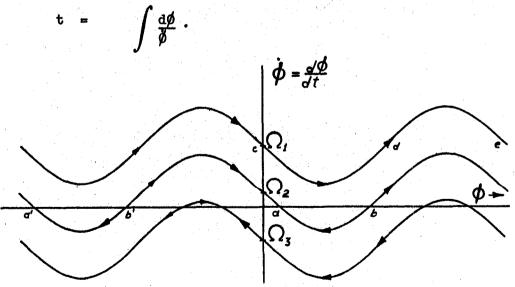

To provide adequate loop gain it was felt that a commercial high gain amplifier should be employed at a convenient intermediate frequency. This intermediate frequency was 30 Mc/s. This unit was purchased in order to reduce the time required to construct the system. The VCO frequency then had to differ from the signal frequency by 30 Mc/s. By introducing an intermediate frequency the basic loop has necessarily been complicated with three more components. These additional devices are a mixer, which is used in the translation of the information from the signal to the intermediate frequency, the IF amplifier, and a 30 Mc/s. oscillator which is used as the reference to which the phase of the IF signal is compared. The resulting phaselocked loop is illustrated in Fig. 6.

The nature of loop operation can be described qualitatively

K<sub>K</sub>F(D)sin Ø

Fig. 6 Block Diagram of Actual Phase-Locked Loop.

by considering the effect on the system of a small perturbation of the signal frequency. Assume that the loop is initially in lock with zero phase and frequency error as measured at the phase comparator output. If the frequency of the input signal is increased slightly the intermediate frequency would increase the same amount. The increase in frequency at the input is detected as an increase in phase difference between the IF signal and the IF reference. This phase error is increasing as the time integral of the change in frequency. If the rate of increase of phase difference is slow enough the phase comparator output voltage is passed with little attenuation by the loop filter. The VCO frequency is driven in such a direction as to minimize this phase difference. As the rate of phase change becomes greater the filter attenuates  $e_d$  to a greater degree. This necessitates a larger phase error in order to produce the same correcting voltage at the VCO

input. The output of the phase detector is a monotonic function of  $\phi$ for  $-\frac{\pi}{2} < \phi < \frac{\pi}{2}$ . If the phase comparator output voltage required to maintain tracking exceeds  $K_0$  the loop becomes asynchronous. A more detailed discussion of the loop components follows.

## The Tunnel Diode Oscillator

One of the main components in the phase-locked loop is the VCO. This device produces a sinusoidal output voltage which can be adjusted in frequency by means of a DC or low frequency voltage. The tunnel diode can be used in VCO circuits.

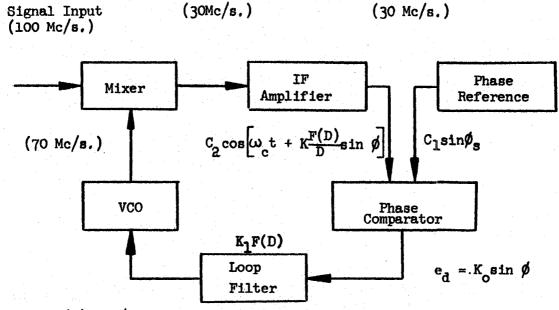

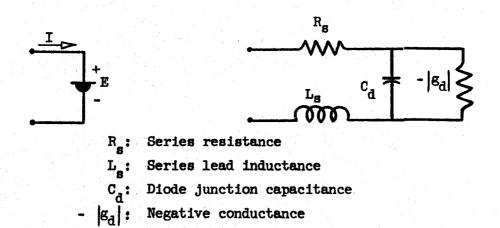

The tunnel diode is a semiconductor device which makes use of the quantum mechanical tunneling effect to produce a net volt-ampere characteristic that includes a negative conductance region. Such a conductance implies that the element can deliver energy to the circuit to which it is connected. The parameters of the circuit are tuned so that the energy is provided at the resonant frequency.

In addition to a negative conductance, the tunnel diode also exhibits an internal capacitance due to the p-n junction. The corresponding incremental parameters vary in magnitude with the position of the operating-point on the volt-ampere characteristic. A series resistance and inductance are included in the equivalent circuit. These quantities are due mainly to the resistivity of the semiconductor material and the lead wires. The internal resistance and inductance can usually be neglected in comparison with the external circuit components. However, since the negative conductance and diode capacitance vary with the operating point, voltage tuning of a tunnel diode oscillator can be achieved by adjusting the bias voltage. This was demonstrated by Gottlieb<sup>(5)</sup>. However, the amplitude of the output signal is also

- E: voltage across the tunnel diode

- I: tunnel diode current

(a) The Tunnel Diode Volt - Ampere Characteristic

(b) The Tunnel Diode Circuit Symbol and (c) Small Signal Equivalent Circuit

Fig. 7 The Tunnel Diode

dependent on its operating point. Thus a better method of tuning would be to varying a reactance in the oscillator circuit. Gottlieb and Giorgis<sup>(6)</sup> have given several examples of voltage tuned tunnel diode oscillators which utilize a reverse biased semiconductor diode called a varicap. The name comes from the use of this element as a variable capacitance. Its operation depends on the variation with bias voltage of the width of the depletion region at a p-n junction. As the reverse bias on a p-n junction increases, the depletion region increases in extent. This has the effect of increasing the width of the junction and thereby decreasing the junction capacitance. A solid state voltage variable reactance for use in the VCO is then available.

A varicap-tuned tunnel diode oscillator was designed and constructed. The design was checked by operating a prototype and the final circuit was followed by a two stage amplifier, both mounted on a single chassis.

# Transistorized 70 Mc/s. Amplifier

The power output capability of a tunnel diode is not great enough for our application. Fig. 6 indicates that the VCO is the local oscillator in the frequency translation process, and therefore, requires an output of a few milliwatts. An amplifier is required which is capable of delivering the required power when driven by the tunnel diode oscillator.

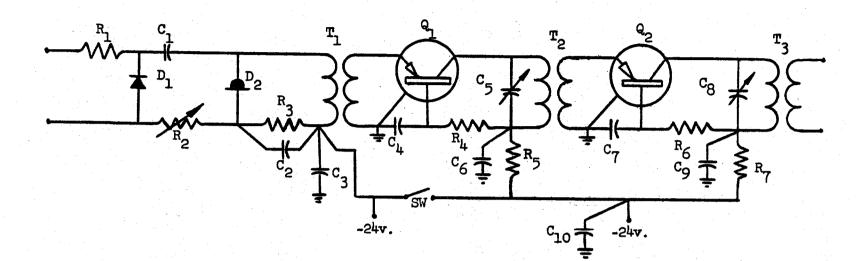

A two-stage transistor amplifier can meet these requirements. The common base circuit configuration was employed in order to avoid internal feedback problems. The stages were single tuned and transformer-coupled. Since there was no stringent bandwidth requirement, the overall amplifier was not broadbanded. The transistors used were readily available and

inexpensive. The final circuit of the oscillator-amplifier is given in Fig. 8.

#### The Mixer

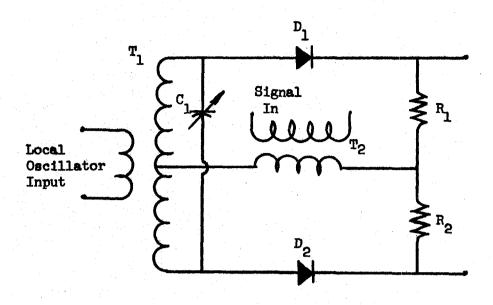

This device depends for its operation on the non-linearity of some circuit element. Components of the output signal which are proportional to the product of two input signals are thereby produced. Such a device is called a multiplier. A product of two sinusoids gives rise to two sinusoids whose arguments are the sum and difference of the originals. Therefore, by filtering the output of such a device to obtain the desired component, frequency translation to the difference between the input and local oscillator frequencies is achieved. The filtering is accomplished by the amplifier following the mixer. A nonlinear device commonly used for multiplication is the diode.

The IF preamplifier has input connections which provide for a balanced mixer in the frequency converter. A balanced mixer, being more sensitive than a conventional mixer was therefore used. The circuit diagram is given in Fig. 9.

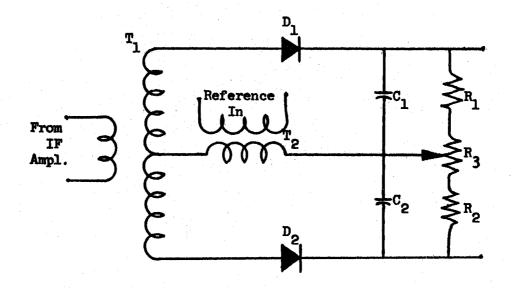

## The Phase Comparator

The phase comparator is another multiplier element. In this case, the input signals are at the same frequency, and the output is then a sine function of the phase difference between the inputs. The circuit is given in Fig. 10. The similarity between this circuit and that of the mixer is evident. The capacitors  $C_1$  and  $C_2$  are added to insure the elimination of the high frequency component of output voltage. They comprise, therefore, a portion of the loop filter which will be discussed in the next section. The output of the phase comparator is proportional to the product of the amplitudes of the inputs. Thus its

R<sub>1</sub>: 10 Kohms R<sub>2</sub>: 4.7 Kohms + 10 Kohm potentiometer R<sub>3</sub>: 47 ohms R<sub>4</sub>, R<sub>6</sub>: 470 Kohms R<sub>5</sub>, R<sub>7</sub>: 6.8 Kohms C<sub>6</sub>, C<sub>9</sub>: 1000 pf. C<sub>2</sub>, C<sub>3</sub>, C<sub>4</sub>, C<sub>7</sub>, C<sub>10</sub>: 0.01 µf. C<sub>1</sub>: 0.011 µf. C<sub>5</sub>, C<sub>8</sub>: 9 - 180 pf. D<sub>1</sub>: 1N954 Varicap Diode 14 - 88 pf. (Hughes) D<sub>2</sub>: TD-1 (1N3712) G.E. Tunnel Diode

Primary: 10 turns 18 gauge tinned copper bus - oscillator tuning inductor Secondary: 1 turn 20 gauge nyclad\* copper wire, - air core, 1/4 in. diam.

T2, T3\*Primary: 2 turns 18 gauge tinnedtrcopper busnySecondary: 6 turns 20 gauge nyclad\*wicopper wife evenly spaced over 3/4 in.- wound on 3/8 in. diam. polystyrene core.

\* - nyclad trade name for nylon insulated wire

Q1, Q2: RCA

2N1177

transistors

Fig. 8 The Complete VCO Circuit Schematic Diagram

R<sub>1</sub>, R<sub>2</sub>: 10 Kohms D<sub>1</sub>, D<sub>2</sub>: 1N82A G.E. C<sub>1</sub>: 3-60pf.

T1

Primary: 1 turn of 24 guage nyclad copper wire Secondary: 28 turns of 18 guage tinned copper bus, centre tapped evenly spaced over 1 3/8 in. of an air core, 1/4 in. in diam.

T2

Primary: 1 turn of 24 guage nyclad copper wire Secondary: 15 turns of 18 guage tinned copper bus evenly spaced over 1 in. of a polystyrene form 1/4 in. in diam.

Fig. 9 Schematic Diagram of the Mixer Circuit

C<sub>1</sub>, C<sub>2</sub>: 100 pf. D<sub>1</sub>, D<sub>2</sub>: 1N82A (G.E.) R<sub>1</sub>, R<sub>2</sub>: 4.7 Kohms R<sub>3</sub>: 1.0 Kohm potentiometer

T

Primary: 4 turns of 20 guage nyclad copper wire Secondary: 16 turns of 18 guage tinned copper bus centre tapped, evenly spaced on a 1 in. length of 1/4 in. diam. polystyrene form

т2

Primary: 3 turns of 20 guage nyclad copper wire Secondary: 10 turns of 18 guage tinned copper bus evenly spaced on a 7/16 in. length of 3/8 in. diam. polystyrene form

Fig. 10 Schematic Diagram of the Phase Comparator Circuit

gain is controlled by adjusting the amplitudes of the reference oscillator and IF amplifier.

# The Loop Filter

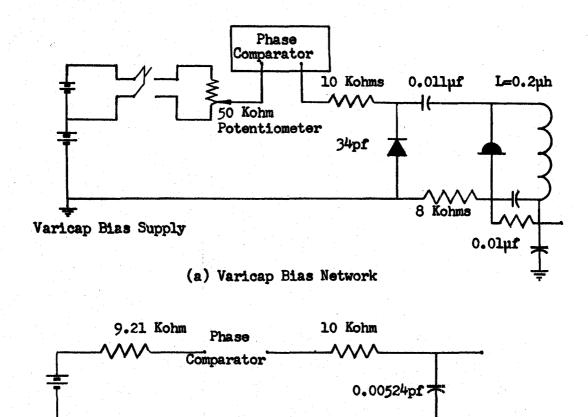

As has been mentioned, the phase comparator makes a contribution to the loop filtering. However, the 3db cut-off frequency of this component is about 300 Kc/s. The loop is intended to track FM at audio modulating frequencies. This cut-off frequency is then well above the frequencies of interest in the loop. Therefore any part of the circuit causing noticeable filtering must be elsewhere in the loop - either in a formal filter network, or inherent in one of the other loop devices. No formal filter network was constructed, so the loop components were examined for possible filtering effects. It was determined that the VCO input network was the only portion of the loop which could produce filtering at audio frequencies. An analysis of this network indicates that it has the form of a simple passive integrating circuit with a cutoff frequency of 158 Kc/s. Since no other portion of the loop has appreciable filtering properties in this frequency range, this network is essentially the loop filter. Fig. 11 shows the evolution of the low frequency equivalent circuit of the VCO input. The circuit in Fig. 11(c) is a perfect high frequency integrator. Therefore, this system is a second order automatic phase control loop.

#### Other Loop Components

The remaining devices in the loop are not especially significant with regard to loop behaviour. However to complete the description of the loop these items are listed. The IF amplifier is an EHG Electronics Laboratory Model F30VAR preamplifier followed by the Model E-3010 amplifier. It can provide a maximum gain of 95 db and has a

109882

# UNIVERSITY OF WINDSOR LIBRARY

(b) Equivalent circuit after eliminating components negligible at audio frequencies.

(c) Simplified Equivalent Circuit

$V_i$ : Voltage input to filter - output of phase comparator. V: Voltage applied to varicap.

Fig. 11 Evolution of the Varicap Bias Network Equivalent Circuit

bandwidth variable from 11 to 1 Mc/s. The amplifier saturates at an output power level of +13 dbm. A General Radio Type 1211-b unit oscillator was used to provide the 30 Mc/s. reference signal. a Marconi FM/AM Signal Generator, Type TF995 A/2M provided the signal.

### CHAPTER V

#### SYSTEM OPERATION

### Preliminary Operation

Initially, electronically regulated DC supplies were used for all power sources. However, voltage spikes and ripple in the outputs of the tunnel diode and varicap bias supplies resulted in incidental frequency modulation of the VCO output. It was therefore decided to use batteries for these power sources. As a matter of convenience, the 70 Mc/s amplifier was powered by the tunnel diode battery supply.

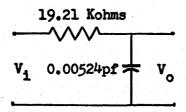

The tuning characteristic of the VCO was measured and is shown in Fig. 12. Much of the information required about the VCO is obtainable from this graph. Although no attempt was made to find the maximum tuning range, the frequency was easily varied from 60 to 80 Mc/s. This range is very large compared to 75 Kc/s - a typical value of frequency deviation. Therefore, the system tracking range is not limited by the VCO. This fact is implicitly assumed in phase-locked loop analysis (1,2,3,4), and is realized in our system largely because of the frequency versatility of the tunnel diode. This curve also reveals the range over which the oscillator can be used with approximately linear control over its output frequency. The tuning sensitivity of the oscillator at 70 Mc/s is 1.153 Mc/s/volt. This value is the slope of the curve at the operating point.

### Dynamic Loop Operation

The tunnel diode automatic phase control system described above is

Fig. 12 VCO Tuning Characteristic

a second order loop with a perfect high frequency integrator filter. Thus, the criterion for maximum dynamic tracking is

$$\Delta \omega_{\text{max}} = \frac{\kappa \alpha}{\sqrt{\alpha^2 + \omega_{\text{m}}^2}}, \qquad (30)$$

where  $\Delta \omega_{\max}$  is the maximum angular frequency deviation at which synchronization is maintained. It was determined that  $\alpha$  corresponds to 1.58 Kc/s.

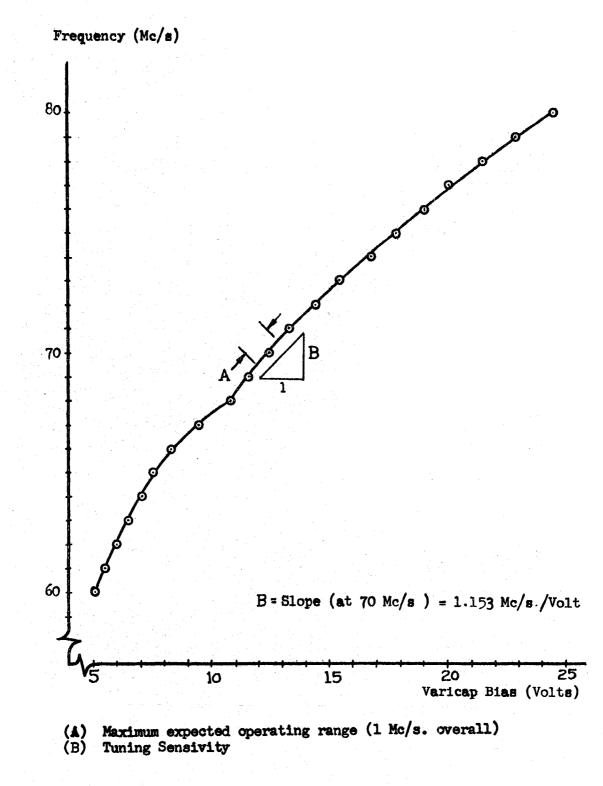

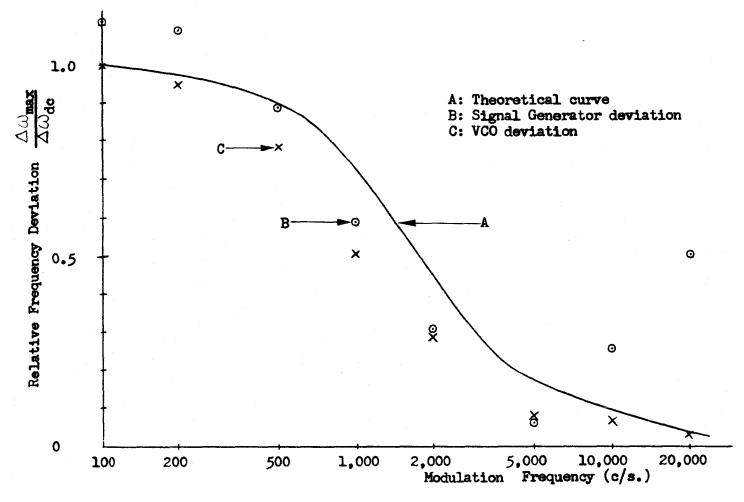

A direct measurement was made of the input impedance of the VCO with the varicap properly biased. From the values of resistance and capacitance obtained, the cut-off frequency was calculated and found to be 1.03 Kc/s. This value is used in plotting equation (30) in Fig. 14 (Curve A). Also indicated in this drawing are the results of an experimental determination of  $\Delta \omega$ max over the audio frequency range. A block diagram of the experimental measuring arrangement is shown in Fig. 13.

Curve B is the maximum relative frequency deviation indicated by the signal generator deviation meter. The static value required for normalization was obtained using the incremental frequency control since the metering and modulating circuits are only useable down to 50 c/s. The deviation meter readings were larger by 10% at 100 and 200 c/s. than the value obtained for static deviation. This fact implies that the possible uncertainty in the frequency deviation measurement is at least 10%.

An FM receiver was used to obtain the data for curve C. Its audio output is used to measure the frequency deviation at the VCO output. It was calibrated against the signal generator monitoring system. However, no standardization of the original generator was executed.

The results of two methods of measuring the frequency deviation

Fig. 14 Maximum Dynamic Lock Range Characteristic

are presented in order to provide a graphical indication of the resolution capability of the instrumentation. The spread of experimental points is within a range of 10% over most of the audio frequency band. There is a major difference between the two experimental curves which starts at about 10 Kc/s. and increases with increasing modulating frequency. The only point that is appreciably outside the 10% range occurs at 20 Kc/s. on curve B. This is largely due to the high frequency limitations on the deviation monitoring system of the signal generator. The specifications for this instrument state that 15 Kc/s. is the upper frequency limit for uniform deviation metering characteristics to within 12% (1 db).

The measurements are then seen to be within the range of expected experimental variation from the theoretical predictions.

### CHAPTER VI

### CONCLUSIONS

It has been found that a first order phase-locked loop has a maximum dynamic lock range for FM signals, of

$$\Delta \omega = K \tag{31}$$

that is independent of the modulating frequency. In addition, the average frequency error exhibited by an asynchronous phase-controlled oscillator is somewhat less than the tuning error.

The second order loop has been shown to have a dynamic lock range that depends on both the upper cut-off frequency of the loop filter, and on the modulating frequency in the manner

$$\Delta \omega_{\text{max}} = \frac{\kappa a}{\sqrt{\alpha^2 + \omega_m^2}}$$

(32)

for the loop with the imperfect integrator, and

$$\Delta \omega_{\rm max} = \frac{\kappa \alpha}{\sqrt{\alpha^2 + \omega_{\rm m}^2}}$$

(33)

for the loop with the perfect high frequency integrator. The result expressed in equation (33) was verified for a second order loop with a perfect high frequency integrator.

The use of semiconductor devices to perform all the essential operations required within the loop has been shown to be practical. The capability of the tunnel diode to provide oscillation at frequencies of a few Gc/s. means that similar phase-locked loops can be constructed to operate at microwave frequencies.

The analysis presented has made use of the examination of phaseplane singularities to arrive at conditions required for maintaining phase synchronization under dynamic conditions. The analysis proceeded on the basis that the signals were deterministic and the experimental investigation was made under conditions of high signal-to-noise ratio (30 db.). However, the foundation has been provided for the application of this technique to a consideration of the statistical properties of the phase-locked oscillator under other conditions relating the signal and noise.

# UNIVERSITY OF WINDSOR LIBRARY

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### REFERENCES

- Viterbi, A. J. "Acquisition and Tracking Behaviour of Phase-Locked Loops," <u>Proc. Symp. on Networks and Feedback Systems</u>, Polytechnic Institute of Brooklyn, N.Y., (April, 1960), 583-619.

- 2. McAleer, Harold T. "A New Look at the Phase-Locked Oscillator," Proceedings of the IRE, 47 (June, 1959), 1137-1143.

- 3. Rey, T.J. "Automatic Phase Control: Theory and Design," Proceedings of the IRE, 48 (Oct., 1960), 1760-1771.

- 4. Sanneman, R.W., and J. R. Rowbotham. "Unlock Characteristics of the Optimum Type II Phase-Locked Loop," IEEE Transactions on Aerospace and Navigational Electronics, ANE-11 (March, 1964), 15-24.

- 5. Gottlieb, Erich. "Tunnel Diode Sinewave Oscillators," Tunnel Diode Application Note 90.33 5/61, Semiconductor Product Department, General Electric Company, Syracuse, New York.

- 6. Gottlieb, Erich, and John Giorgis. "Tunnel Diode: A Four Part Series," Electronics (June 14, June 21, June 28, and July 5, 1963).

# VITA AUCTORIS

| 1941 | Born on August 8, in Windsor, Ontario.                                                                     |

|------|------------------------------------------------------------------------------------------------------------|

| 1954 | Completed elementary education at Prince Edward Public<br>School, Windsor, Ontario.                        |

| 1959 | Graduated from the Hon. J. C. Patterson C.I., Windsor, Ontario.                                            |

| 1963 | Bachelor of Applied Science Degree in Electrical Engineering from Assumption University, Windsor, Ontario. |

| 1964 | <b>Candidate</b> for the degree of M.A.Sc. in Electrical Engineering at the University of Windsor.         |