### **University of Windsor**

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1-1-2007

# A CAD tool for design space exploration of embedded CPU cores for FPGAs.

lan D. L. Anderson University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Anderson, Ian D. L., "A CAD tool for design space exploration of embedded CPU cores for FPGAs." (2007). *Electronic Theses and Dissertations*. 7120.

https://scholar.uwindsor.ca/etd/7120

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# A CAD Tool for Design Space Exploration of Embedded CPU Cores for FPGAs

by

### Ian D. L. Anderson

A Thesis

Submitted to the Faculty of Graduate Studies and Research through Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-42311-0 Our file Notre référence ISBN: 978-0-494-42311-0

### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### © 2007 Ian D. L. Anderson

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

### Abstract

In this thesis, a genetic algorithm based design space exploration technique using parameterized cores is examined. A case study was first conducted to investigate the feasibility of applying a genetic based approach to a parameterized core. Next, a computer aided design tool called SCBuild was developed which utilizes the investigated approach. This tool is capable of applying a genetic algorithm to a core's parameters, and generating hardware description language models of core variants. The tool can also compute estimates of a variant's area and critical path delay on a field programmable gate array. Using this tool, several experiments were conducted using a soft-core processor with a large design space. It was concluded from these experiments that using a genetic algorithm to explore the design space of a parameterized core can help a designer make intelligent decisions regarding the assignment of values to the parameters of an embedded hardware platform.

To Mom, Dad, Karis and Hil.

## Acknowledgments

I thank the Lord Jesus for the way in which He pulled me through this degree and gave me the determination to see it to completion. I find myself standing here at the end of this task, not entirely sure about how I got here. But here I am nonetheless, and for that I am thankful.

I would like to express my sincere thanks to Dr. Khalid for all of the advice and guidance he provided over the course of this research. His assistance to me was invaluable as I worked my way through the often-confusing world of research work. My appreciation also goes out to Dr. Kobti and Dr. Wu, for taking the time to sit on my committee and to review my thesis, and to Dr. Tepe for sitting in as the Chair of Defense.

Thanks to my family for all of their support, patience and prayers as I completed this thesis. Thanks Mom for all your love, encouragement and wise advice, from which I have always benefited immensely. I know you've been through a lot over the past year, but I still appreciate the ways that you were there for me as much as you could. Dad, I am grateful for the ways in which you helped me get through this degree; for cooking dinner, for picking me up on those late nights at the office, and just being around when I needed someone to pester when my thesis was driving me

nuts. It looks like I have officially finished my thesis before you could get yours done, so I guess you owe me a trip to Timmy's. Karis, my brilliant sister; thanks to you I never forgot that my thesis was "taking forever". But at least now it's done, so you can find something new to tease me about. Thanks for keeping me humble and giving me some good laughs along the way.

To my wonderful girlfriend, Hilary: you've always been a steadfast support to me in all my endeavours. It is always great spending time with you, eating lunch, going for a run, or just sitting around chatting and laughing about anything and everything together. Your visits were always a very welcome relief from my thesis work. Thank you also for helping me to edit my thesis and even learning what "FPGA" stands for. And to the rest of the Leslie family: thanks for the ways that you've welcomed me into your lives. Also, thank you very much for lending me your car; it was very helpful to have it these past few weeks. And thank you Brian for taking the time to read and edit my entire thesis. Your revisions were very good and helped to make this work that much better.

Finally, I would like to acknowledge my friends and fellow graduate students at the University of Windsor. Jay, thanks for always keeping us amused with your various accents and impressions. We had some great times, from our all-day "programming parties" to just hanging out day-to-day in the office. Marwan, I will always remember all of the great conversations we've had on a whole host of topics ranging from religion, ethics and philosophy to the weather, food, politics and many other things that were (thankfully) unrelated to the field of engineering. Seldom have I met anybody who can talk intelligently on as many different subjects as you. Thanks to Amir for his willingness to give generously of his time in all of the ways that he has helped me during the course of this degree, and even before that. Thanks to Frank for his assistance on many occasions; for providing parts, equipment and advice for my various projects, and for just being available to sit and chat when I needed a break.

Lastly, thanks to the rest of my engineering colleagues as well; to Ray, Omar, Aws, Junsong, Hongmei, Kevin, Matt, Andrew, Harb, Mahzad, Ashkan and everyone else who have made this time in my life more enjoyable.

## Contents

| $\mathbf{A}$ | bstra | ct      |                                                       | iv   |

|--------------|-------|---------|-------------------------------------------------------|------|

| D            | edica | tion    |                                                       | v    |

| A            | cknov | wledgn  | nents                                                 | vi   |

| Li           | st of | Figure  | es                                                    | xiii |

| Li           | st of | Tables  | 3                                                     | xvi  |

| Li           | st of | Abbre   | eviations                                             | xvii |

| Li           | st of | Symbo   | ols                                                   | xix  |

| 1            | Intr  | oducti  | on                                                    | 1    |

|              | 1.1   | Thesis  | Objectives                                            | 5    |

|              | 1.2   | Thesis  | Organization                                          | 7    |

| 2            | Bac   | kgrour  | nd and Previous Work                                  | 8    |

|              | 2.1   | Intelle | ctual Property (IP) Cores                             | 8    |

|              |       | 2.1.1   | The Digital Abstraction Hierarchy                     | 9    |

|              |       | 2.1.2   | Classes of Hardware IP Cores                          | 11   |

|              | 2.2   | Param   | eterization: Increasing the Reusability of an IP Core | 13   |

|              |       |         |                                                       |      |

|   | 2.3 | Soft-cor  | re Processors                                                | 15 |

|---|-----|-----------|--------------------------------------------------------------|----|

|   |     | 2.3.1     | Examples of Soft-core Processors                             | 15 |

|   | 2.4 | FPGA      | Technology                                                   | 16 |

|   | 2.5 | Design    | Space Exploration (DSE)                                      | 21 |

|   |     | 2.5.1     | Multi-objective Optimization                                 | 21 |

|   |     | 2.5.2     | DSE Using Parameterized Cores                                | 23 |

|   | 2.6 | Closely   | Related Work                                                 | 26 |

|   | 2.7 | Summa     | ry                                                           | 28 |

| 3 | Des | ign Spa   | ce Exploration of Embedded CPU Cores for FPGAs               | 30 |

|   | 3.1 | Problen   | n Statement                                                  | 31 |

|   | 3.2 | The Alt   | tera Nios Soft-core Processor                                | 32 |

|   |     | 3.2.1     | Target System                                                | 34 |

|   | 3.3 | The Sin   | aple Evolutionary Algorithm for Multi-Objective Optimization |    |

|   |     | (SEAM     | O)                                                           | 34 |

|   |     | 3.3.1     | Evaluation of Configurations: The Objective Functions        | 37 |

|   | 3.4 | Experin   | nental Results                                               | 40 |

|   |     | 3.4.1     | Testing of Objective Functions                               | 40 |

|   |     | 3.4.2     | Experimental Determination of Algorithm Parameters           | 40 |

|   |     | 3.4.3     | Comparison of SEAMO Results Vs. Randomly Generated Con-      |    |

|   |     | i         | figurations                                                  | 43 |

|   | 3.5 | Conclus   | sions Drawn from this Case Study                             | 44 |

|   | 3.6 | Summa     | ry                                                           | 45 |

| 4 | SCI | Build - A | A CAD Tool for the DSE of Embedded CPU Cores                 | 46 |

|   | 4.1 | Major I   | Problems Addressed by SCBuild                                | 47 |

|   |     | 4.1.1     | Representing a Parameterized Core in Software                | 47 |

|   |     | 4.1.2     | Exploring the Design Space of a Parameterized Core           | 50 |

|   |     |           |                                                              |    |

|   |     | 4.1.3  | Generating HDL Descriptions of Core Instances        | 50  |

|---|-----|--------|------------------------------------------------------|-----|

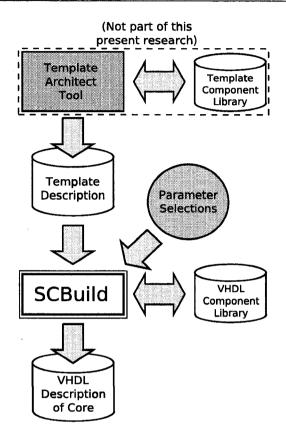

|   | 4.2 | SCBui  | ld System Environment                                | 50  |

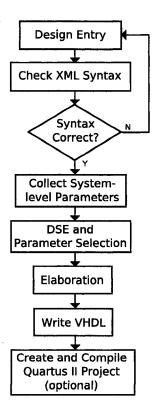

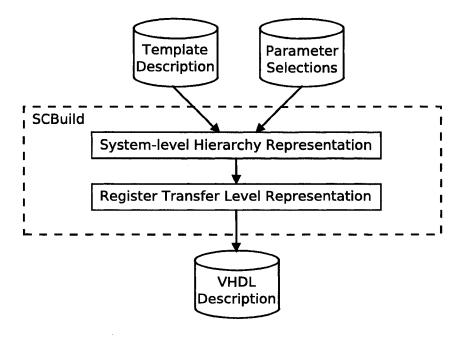

|   | 4.3 | CAD I  | Flow for SCBuild                                     | 52  |

|   |     | 4.3.1  | Design Entry and Template Description                | 52  |

|   |     | 4.3.2  | XML Syntax Checking                                  | 56  |

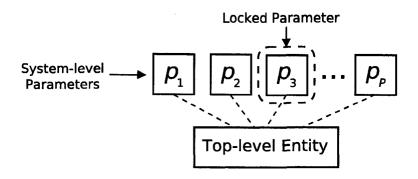

|   |     | 4.3.3  | Collect System-level Parameters                      | 57  |

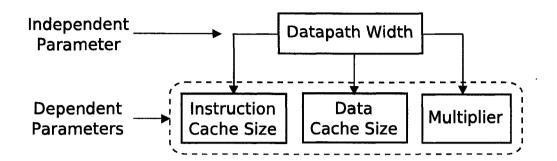

|   |     | 4.3.4  | DSE and Parameter Selection                          | 57  |

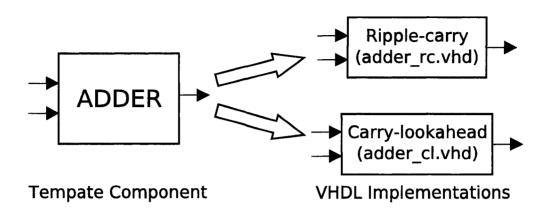

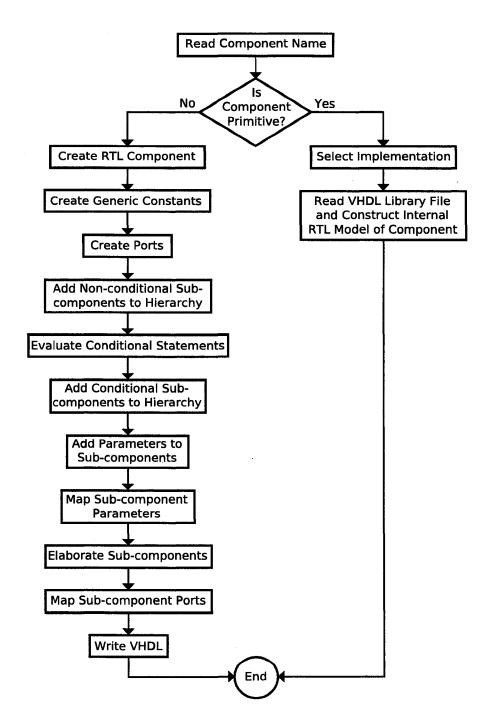

|   |     | 4.3.5  | Elaboration                                          | 63  |

|   |     | 4.3.6  | Quartus II Project Creation and Compilation          | 68  |

|   | 4.4 | The V  | HDL Component Library                                | 68  |

|   | 4.5 | Develo | opment and Implementation                            | 70  |

|   |     | 4.5.1  | General Design Priorities                            | 71  |

|   |     | 4.5.2  | SCBuild Software Development Methodology             | 72  |

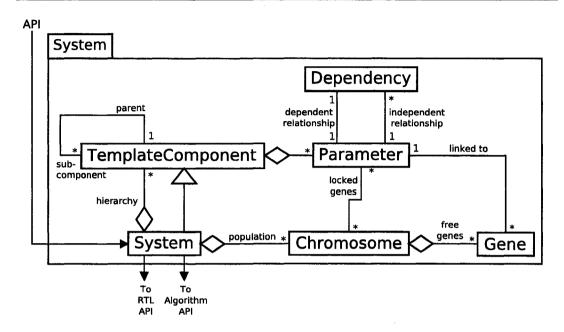

|   |     | 4.5.3  | SCBuild Software Architecture                        | 73  |

|   |     | 4.5.4  | Implementation Details                               | 80  |

|   | 4.6 | Summ   | ary                                                  | 80  |

| 5 | Exp | erime  | ntal Results                                         | 81  |

|   | 5.1 | Target | t Core                                               | 82  |

|   | 5.2 | Establ | lishing the Objective Estimation Equations           | 83  |

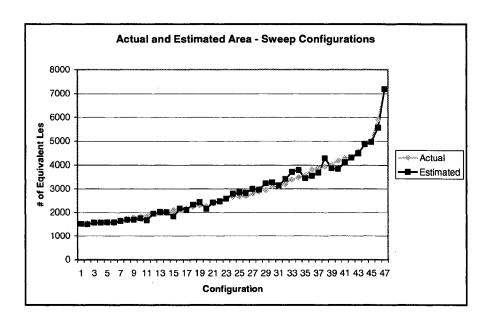

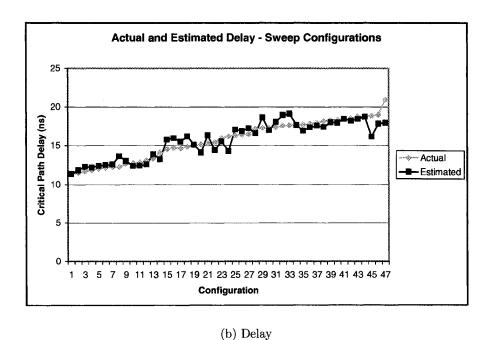

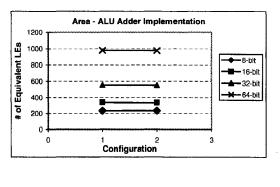

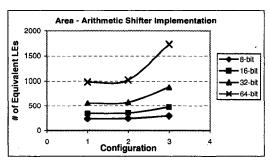

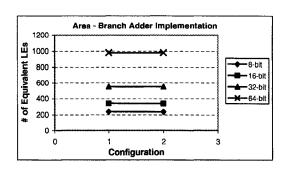

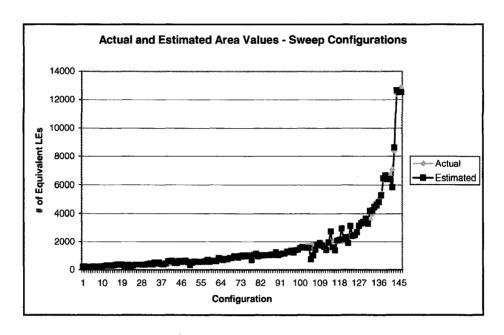

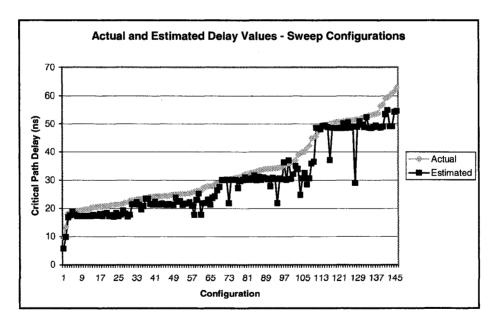

|   |     | 5.2.1  | Results of Parameter Sweep                           | 85  |

|   |     | 5.2.2  | Determining the Final Objective Estimation Equations | 93  |

|   |     | 5.2.3  | Testing the Objective Estimation Equations           | 93  |

|   | 5.3 | Design | Space Exploration                                    | 97  |

|   |     | 5.3.1  | Algorithm Parameters                                 | 97  |

|   |     | 5.3.2  | Results                                              | 98  |

|   | 5.4 | Conclu | usions Drawn From Results                            | 99  |

|   | 5.5 | Summ   | ary                                                  | 101 |

|   |     |        |                                                      |     |

| 6            | Con               | clusions and Future Work                             | 102 |  |

|--------------|-------------------|------------------------------------------------------|-----|--|

|              | 6.1               | Summary of Research Contributions                    | 103 |  |

|              | 6.2               | Future Work                                          | 104 |  |

| Aı           | ppen              | dices                                                | 107 |  |

| $\mathbf{A}$ | Det               | ails of the SCBuild Template Description File Format | 107 |  |

|              | A.1               | Primitive Template Component Descriptions            | 109 |  |

|              | A.2               | Aggregate Template Component Descriptions            | 110 |  |

|              | A.3               | The Parameter Dependencies File                      | 112 |  |

|              | A.4               | The Objectives File                                  | 114 |  |

|              | A.5               | The System File                                      | 115 |  |

| В            | Des               | cription of the RISC Processor Template              | 116 |  |

|              | B.1               | Parameters                                           | 116 |  |

|              | B.2               | Instruction Set                                      | 118 |  |

|              | B.3               | Structure                                            | 120 |  |

|              |                   | B.3.1 Datapath                                       | 121 |  |

|              |                   | B.3.2 Control Unit                                   | 124 |  |

| $\mathbf{C}$ | Syn               | thesis Results for the RISC Processor Template       | 127 |  |

|              | C.1               | Parameter Sweep Results                              | 127 |  |

|              | C.2               | Initial and Evolved Populations                      | 134 |  |

|              |                   | C.2.1 Initial Population                             | 134 |  |

|              |                   | C.2.2 Evolved Population                             | 137 |  |

| $\mathbf{R}$ | efere             | nces                                                 | 140 |  |

| V            | VITA AUCTORIS 146 |                                                      |     |  |

## List of Figures

| 1.1 | Block Diagram of an Embedded System                                 | 2  |

|-----|---------------------------------------------------------------------|----|

| 2.1 | The Three Classes of Hardware IP Cores                              | 12 |

| 2.2 | Schematic of a Generic FPGA Logic Element (LE) [42]                 | 17 |

| 2.3 | Schematic of a Lookup Table (LUT)                                   | 18 |

| 2.4 | Generic FPGA Routing Architecture (adapted from [25])               | 19 |

| 2.5 | The Concept of Pareto-optimality Illustrated (adapted from $[60]$ ) | 22 |

| 2.6 | Illustration of a 2-Dimensional Design Space                        | 23 |

| 3.1 | The Chromosome Used in the SEAMO Algorithm                          | 35 |

| 3.2 | A Population of Chromosomes                                         | 36 |

| 3.3 | The Crossover and Mutation Operators                                | 37 |

| 3.4 | Actual and Estimated Values for Nios Sweep Configurations           | 41 |

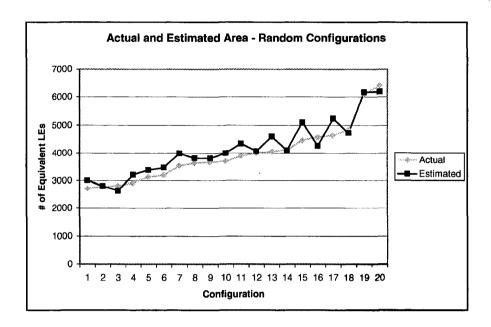

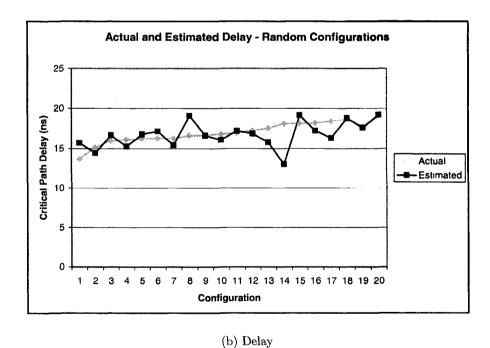

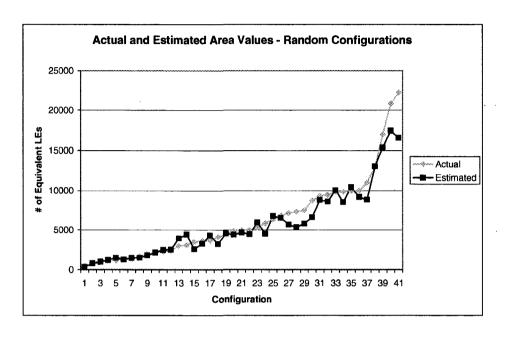

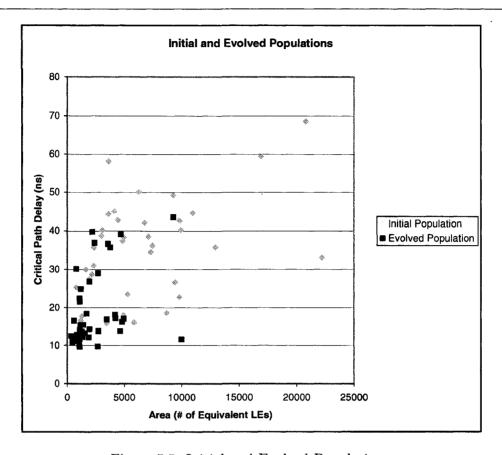

| 3.5 | Actual and Estimated Values for Nios Random Configurations          | 42 |

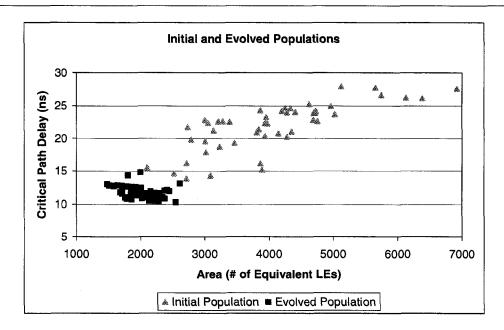

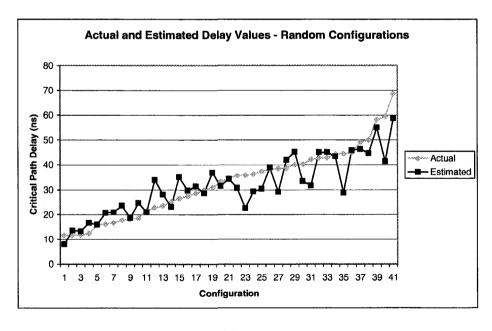

| 3.6 | Initial and Evolved Populations (Using Estimated Values)            | 43 |

| 4.1 | The SCBuild System Environment                                      | 51 |

| 4.2 | The SCBuild CAD Flow                                                | 53 |

| 4.3 | A Primitive Template Component with Multiple VHDL Implementations   | 55 |

| 4.4 | Top-level Entity with System-level Parameters                       | 57 |

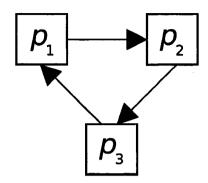

| 4.5 | Interdependency Relationships Between System-level Parameters       | 59 |

|     |                                                                     |    |

| 4.6  | Cyclic Dependency Loop                                                          | 60  |

|------|---------------------------------------------------------------------------------|-----|

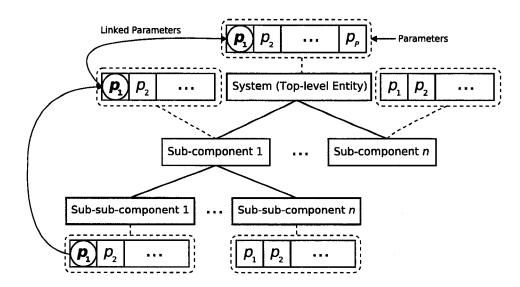

| 4.7  | System-level Description: Elaboration Hierarchy                                 | 64  |

| 4.8  | Translation of Representations                                                  | 65  |

| 4.9  | Flowchart for the SCBuild Elaboration Algorithm                                 | 67  |

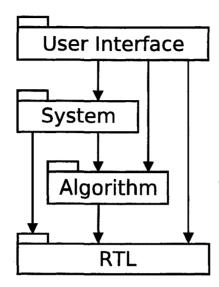

| 4.10 | UML Package Diagram for the SCB<br>uild Software Architecture $\ . \ . \ . \ .$ | 74  |

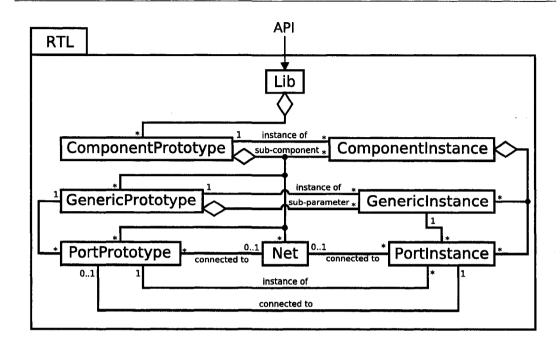

| 4.11 | Class Model for the RTL Layer                                                   | 75  |

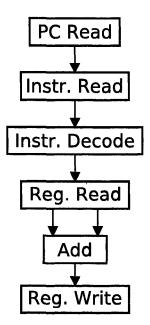

| 4.12 | Data Dependence Graph for a Generic Add Instruction                             | 77  |

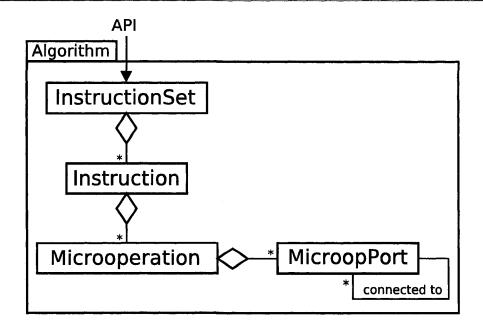

| 4.13 | Class Diagram for the Algorithm layer                                           | 78  |

| 4.14 | Class Diagram for the System layer                                              | 79  |

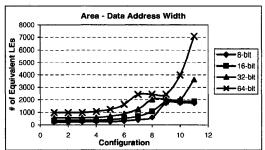

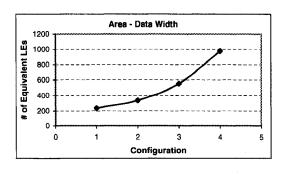

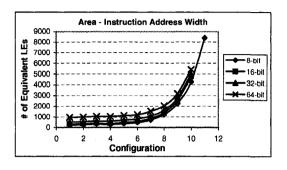

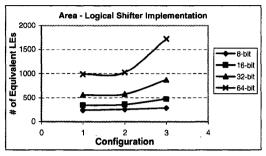

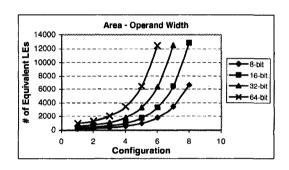

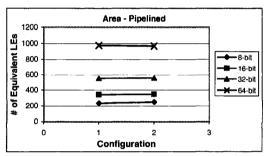

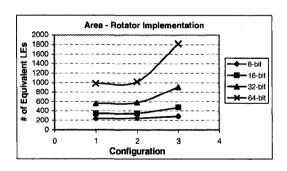

| 5.1  | Parameter Sweep Results – Area                                                  | 87  |

| 5.1  | Parameter Sweep Results – Area (Cont'd)                                         | 88  |

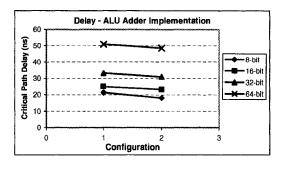

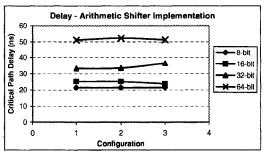

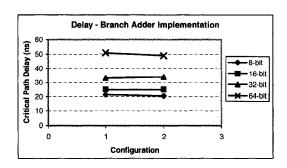

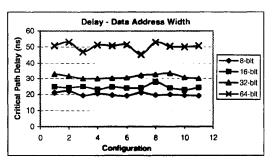

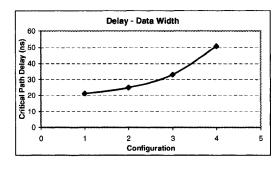

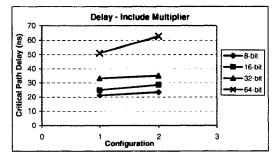

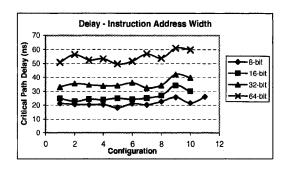

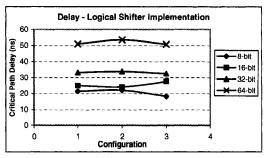

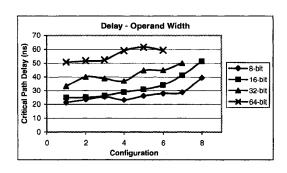

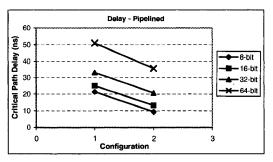

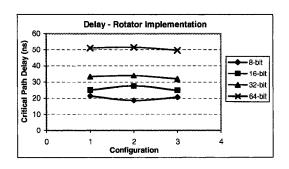

| 5.2  | Parameter Sweep Results – Delay                                                 | 91  |

| 5.2  | Parameter Sweep Results – Delay (Cont'd)                                        | 92  |

| 5.3  | Actual and Estimated Values for Sweep Configurations                            | 95  |

| 5.4  | Actual and Estimated Values for Random Configurations                           | 96  |

| 5.5  | Initial and Evolved Populations                                                 | 98  |

| A.1  | Aggregate XML Template Component Descriptions                                   | 108 |

| A.2  | Primitive XML Template Component Descriptions                                   | 108 |

| A.3  | An Example Parameter Declaration                                                | 108 |

| A.4  | An Example Implementation Declaration                                           | 110 |

| A.5  | An Example Port Declaration                                                     | 110 |

| A.6  | An Example of a Sub-Components Section                                          | 111 |

| A.7  | Example of a Dependency Relationship Definition                                 | 113 |

| A.8  | An Example of an Objective Estimation Equation Definition in the                |     |

|      | Objectives File                                                                 | 114 |

| A.9  | An Example of an System File Listing                                            | 115 |

### LIST OF FIGURES

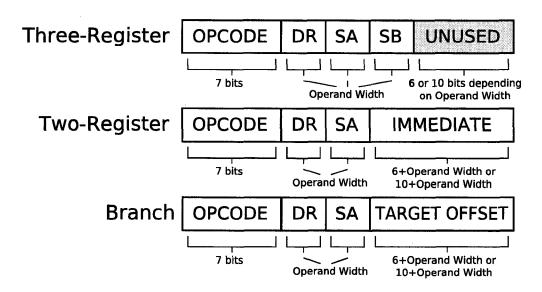

| B.1 | Instruction Formats for the RISC Processor | 118 |

|-----|--------------------------------------------|-----|

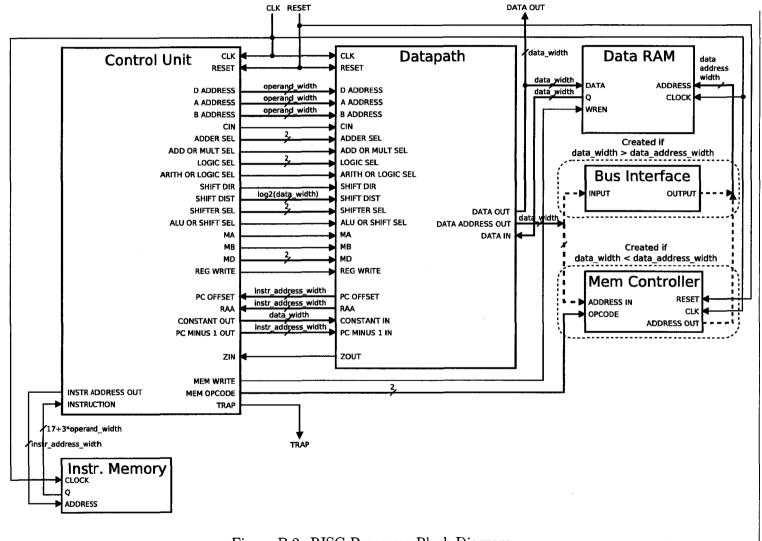

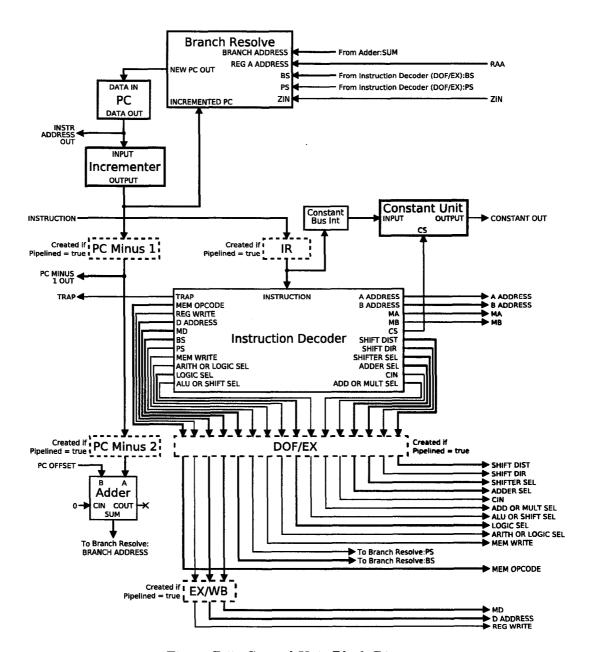

| B.2 | RISC Processor Block Diagram               | 122 |

| B.3 | Datapath Block Diagram                     | 123 |

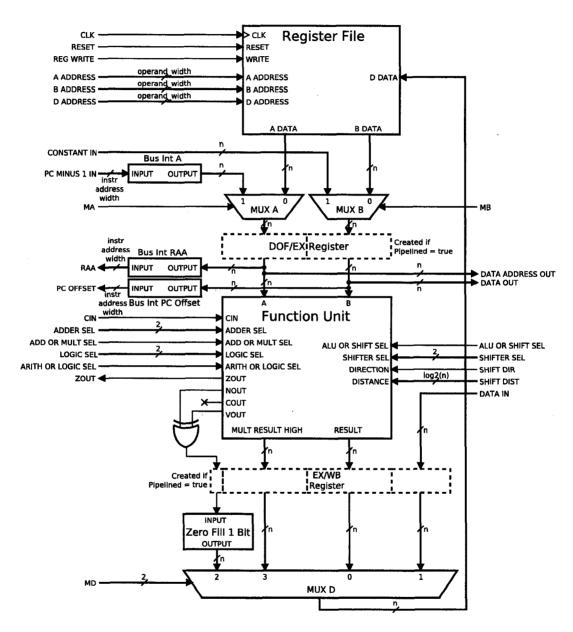

| B.4 | Function Unit Block Diagram                | 124 |

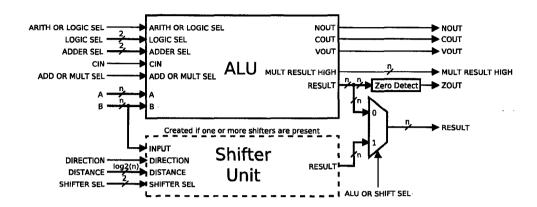

| B.5 | Control Unit Block Diagram                 | 126 |

## List of Tables

| 2.1 | The Digital Design Hierarchy [11, 50, 65, 61]                     | 10  |  |

|-----|-------------------------------------------------------------------|-----|--|

| 3.1 | Altera Nios Hardware Parameters                                   | 33  |  |

| 3.2 | Relative Sizes of Stratix Components (from [75])                  | 39  |  |

| 3.3 | Regression Coefficients – Nios Processor                          | 39  |  |

| 4.1 | An Example of a Dependency Table                                  | 61  |  |

| 4.2 | Components in the VHDL Component Library                          | 69  |  |

| 5.1 | RISC Processor Hardware Parameters                                | 84  |  |

| 5.2 | Summary of Parameter Sweep Results                                | 85  |  |

| 5.3 | Regression Coefficients for RISC CPU                              | 93  |  |

| 5.4 | Number of Occurrences of Each Parameter Value in the Evolved Pop- |     |  |

|     | ulation                                                           | 99  |  |

| A.1 | Dependency Lookup Tables for Data Width and Multiplier Parameters | 113 |  |

| B.1 | RISC Processor Hardware Parameters                                | 117 |  |

| B.2 | RISC Processor Instructions                                       | 119 |  |

| C.1 | Parameter Sweep Data                                              | 127 |  |

| C.2 | Data for Initial Population                                       | 134 |  |

| C.3 | Data for Evolved Population                                       | 137 |  |

## List of Abbreviations

| Abbreviation           | Definition                                        |

|------------------------|---------------------------------------------------|

| ADL                    | Architecture Description Language                 |

| $\operatorname{ALU}$   | Arithmetic Logic Unit                             |

| API                    | Application Programming Interface                 |

| ASIC                   | Application-Specific Integrated Circuit           |

| ASIP                   | Application-Specific Instruction-set Processor    |

| CAD                    | Computer Aided Design                             |

| CPU                    | Central Processing Unit                           |

| DOF                    | Decode and Operand Fetch                          |

| DSE                    | Design Space Exploration                          |

| DSP                    | Digital Signal Processing                         |

| $\mathbf{E}\mathbf{A}$ | Evolutionary Algorithm                            |

| EX                     | Execute                                           |

| $\mathbf{FF}$          | Flip-Flop                                         |

| FPGA                   | Field Programmable Gate Array                     |

| GA                     | Genetic Algorithm                                 |

| GUI                    | Graphical User Interface                          |

| $\operatorname{HDL}$   | Hardware Description Language                     |

| $\mathbf{IEEE}$        | Institute of Electrical and Electronics Engineers |

| I/O                    | Input/Output                                      |

| IC                     | Integrated Circuit                                |

| $\operatorname{IF}$    | Instruction Fetch                                 |

| IOE                    | Input/Output Element                              |

| IP                     | Intellectual Property                             |

| LAB                    | Logic Array Block                                 |

| ${ m LE}$              | Logic Element                                     |

|                        |                                                   |

| LUT                  | Lookup Table                                                   |

|----------------------|----------------------------------------------------------------|

| MUX                  | Multiplexer                                                    |

| PLD                  | Programmable Logic Device                                      |

| RAM                  | Random Access Memory                                           |

| RISC                 | Reduced Instruction Set Computer                               |

| ROM                  | Read Only Memory                                               |

| SEAMO                | Simple Evolutionary Algorithm for Multi-objective Optimization |

| $\operatorname{SoC}$ | System on a Chip                                               |

| SOPC                 | System on a Programmable Chip                                  |

| $\mathbf{UART}$      | Universal Asynchronous Receiver/Transmitter                    |

| UML                  | Unified Modeling Language                                      |

| VHDL                 | Very High Speed Integrated Circuit Hardware Description        |

|                      | Language                                                       |

| WB                   | Write Back                                                     |

| XML                  | Extensible Markup Language                                     |

## List of Symbols

| Symbol                                   | Definition                                                               |

|------------------------------------------|--------------------------------------------------------------------------|

|                                          | Definition                                                               |

| P                                        | Total number of parameters.                                              |

| $p_i$                                    | The $i^{th}$ parameter.                                                  |

| i                                        | Parameter index.                                                         |

| $V_{i}$                                  | Set of possible values for the $i_{th}$ parameter.                       |

| D                                        | Design space.                                                            |

| -                                        | Cardinality operator.                                                    |

| N                                        | Size of genetic population.                                              |

| G                                        | Number of generations.                                                   |

| $r_c$                                    | Crossover rate.                                                          |

| $r_m$                                    | Mutation rate.                                                           |

| K                                        | Total number of objectives.                                              |

| k                                        | Objective index.                                                         |

| $F_{\boldsymbol{k}}(p_1,p_2,\ldots,p_P)$ | The $k^{th}$ objective function.                                         |

| $f_{i,k}(p_i)$                           | The functional form of $i^{th}$ term of the $k^{th}$ objective function. |

| $a_{i,k}$                                | The $i^{th}$ regression coefficient for the $k^{th}$ objective function. |

## Chapter 1

### Introduction

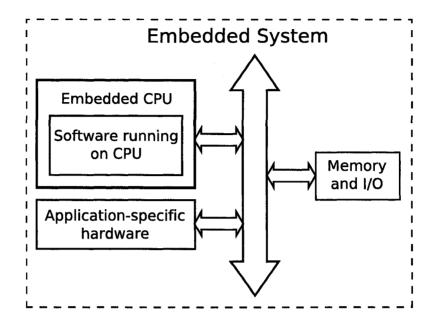

In our modern digital age, devices utilizing embedded systems have become very common and enjoy widespread use in our daily lives. Examples of these systems are abundant and include cellular phones, digital cameras, appliances, automobiles, airplanes, and manufacturing systems. All of these rely on embedded electronic systems to carry out the task for which they were designed. Essentially, an embedded system is an electronic sub-system that utilizes computational hardware to perform a small set of tasks that are specific to a particular application [45]. They can be logically broken down into two major components: the embedded software (sometimes referred to as firmware) and the digital hardware, as shown in Figure 1.1 below.

The hardware component usually consists of one or more embedded central processing units (CPUs) and their associated application-specific hardware. These components communicate with one another and with embedded memory and Input/Output (I/O) components over a common bus. The software component is a program written and compiled specifically to run on the embedded processors. In contrast

Figure 1.1: Block Diagram of an Embedded System

with general-purpose personal computer systems, which are designed to run a virtually infinite variety of different software programs, an embedded processor is only required to execute one piece of software continuously. Therefore, the processor can be optimized to run that piece of software as efficiently as possible; resulting in what is known as an Application Specific Instruction-Set Processor (ASIP). Since embedded systems are utilized in an extremely wide array of applications, it is no surprise that the market for embedded systems today is far larger than that of general-purpose personal computer systems. Therefore, it is quite clear that the field of embedded system design is an important and substantial area of study.

With the continual improvement of integrated circuit (IC) process technology, complete embedded systems can be built onto a single chip. This trend has come to be known as the "system-on-a-chip" (SoC) paradigm. As a result, ever more complex circuits can be designed and implemented on a single IC chip. The widespread use and growing complexity of embedded system designs has led to many important

innovations, but has also introduced many major design challenges. Most importantly, the challenge of developing a complex system within the constraints of a reasonable budget and time-frame is a constant consideration for all embedded systems engineers.

When designing an embedded system, there are several major approaches that have been taken. The traditional approach [27, 23] involves first designing the hardware portion of the embedded system, including the microprocessor and associated application-specific circuitry and then writing the software to run on the microprocessor after the hardware design phase has been completed. However, it was observed by many designers that by using this approach they often missed out on many potential optimizations that could be exploited if the design of the hardware and software portions of the system were considered together. Therefore, a second approach, known as the hardware/software co-design approach [52, 33, 24, 23], took shape. In this approach, the design of the hardware and software parts of the system are designed concurrently, allowing the designer to explore the tradeoffs between hardware and software implementations of the various system tasks.

As the complexity of embedded systems designs increased over time, designing each and every hardware component of the system from scratch soon became far too impractical and expensive for many designers. Therefore, a third approach, known as the platform-based design approach [13, 49, 61], emerged. Platform-based design entails the the idea of using pre-designed and pre-tested hardware components known as intellectual property (IP) cores as a platform upon which to build complete systems. This approach heavily emphasizes design reuse. Using IP cores, a designer can be confident that the building blocks he or she is using in the design will function as expected. As a result, the designer is subsequently freed from designing the components from scratch, which naturally leads to a much shorter design cycle.

Soft-cores are a particular class of hardware IP cores that are often used by designers to build their systems. Essentially soft-cores are hardware components that

are described using a hardware description language (HDL). In order to increase the reusability of soft IP cores across a wider range of application domains, many of them are *parameterized*, meaning that the core's architecture features a number of configurable options or *parameters* that can be set by the engineer at design-time. These options are built into the core's architecture by its creators and allow the designer of an embedded system to tailor the core to closely match the requirements of the system's intended application.

The recent development of field programmable gate arrays (FPGAs) and other programmable logic devices (PLDs) has introduced designers to a new type of flexible prototyping and implementation medium for embedded systems designs that utilize soft-core components. FPGAs are programmable IC chips that can be configured to function like virtually any digital circuit that can be conceived, subject to the limitations imposed by the logic capacity of the device. Soft-core descriptions of hardware components can be translated into a logic circuit which can then be mapped directly onto the programmable fabric of an FPGA. This allows a designer to test the functionality of a logic circuit in real-time without having to fabricate a custom chip. Using FPGAs, different design tradeoffs can be rapidly explored, allowing better design decisions to be made and reducing the overall development time of a system.

When designing an embedded system for any application, it is important that designers come up with a hardware platform that is well suited for their purposes. If this is not done well, the result may be a system that is over-designed or sub-optimal for the intended application, which would almost certainly incur the unnecessary expenditure of additional time and financial resources. Therefore, it is crucial that a good hardware design be selected early in the design process. This endeavour is complicated by the fact that there almost always exists a very large set of possible hardware designs to choose from. This set of all possible hardware design configurations is known as the design space, and the task of selecting the best design from that

set is commonly referred to as design space exploration (DSE) [32].

As the complexity of the system being designed increases and the number of parameters rises, the design space for that system expands. As a result, exploring the design space in search of the best system configuration for a given application can be a difficult and tedious task. An exhaustive exploration approach [31] is often infeasible, therefore many designers rely on past experience to narrow down the number of possible design configurations. Although designer experience is always a very valuable asset to any design project, this approach is considered by some to be too ad hoc [32], and may sometimes yield sub-optimal designs. Therefore, much research has been conducted into automating the process of design space exploration.

This thesis is primarily concerned with the question of how to derive a "good" hardware platform for a given embedded system constructed from a set of parameterized soft-core components. The emphasis of this research is on the design of embedded microprocessors targeted for implementation on FPGAs specifically, since FPGAs are a relatively new technology, and as such, microprocessor design targeting these devices is not yet well understood. In this work, the results of a preliminary investigation into an automated DSE approach involving parameterized cores [9] are presented, the design of a software-based Computer Aided Design (CAD) tool that utilizes this approach is described, and the results obtained from experimentation with this CAD tool are discussed.

### 1.1 Thesis Objectives

The main goal of this research is to contribute toward the enhancement of the collective understanding of how embedded microprocessor design targeting FPGAs is unique in terms of processor architectures, CAD tools, and design techniques and methodologies. In order to achieve this goal, an exploration of the design space of soft-core processors targeting FPGAs should be conducted. To this end, this research

has several major objectives:

- 1. Investigate the feasibility of applying an automated design space exploration algorithm to a parameterized soft-core with a sizable design space.

- 2. Develop a software-based "processor builder" CAD tool that is capable of exploring the design space of a parameterized soft-core using an automated DSE approach. This tool should also be able to generate HDL descriptions for "variants" of a core, given a set of parameter values.

- 3. Perform an exploration of the design space of a parameterized soft-core processor using the processor builder tool, use the tool to generate a set of variant cores, and evaluate the variants in terms of performance and area utilization on an FPGA.

To address the first objective, a preliminary case study was conducted in which an automated DSE approach was applied to the Altera Nios [17] parameterized soft-core processor. In this study, the design space of the Nios core was explored using the Simple Evolutionary Algorithm for Multi-objective Optimization (SEAMO) [69], a genetic algorithm (GA) based approach. For the second thesis objective, a software-based CAD tool called *SCBuild* ("Soft-Core Build") was developed which utilizes the SEAMO algorithm to explore the design space of a user-supplied parameterized core. SCBuild is also capable of estimating a core's area utilization and performance on an FPGA, and can generate structural Very High Speed Integrated Circuit Hardware Description Language (VHDL) [54] descriptions of a core given a specific set of parameter values and a library of soft-core building-block components. Finally, to satisfy the third objective, several design space exploration experiments were conducted using SCBuild and a simple parameterized Reduced Instruction Set Computer (RISC) soft-core microprocessor [48].

### 1.2 Thesis Organization

The outline of this thesis is as follows. Chapter 2 introduces the reader to the greater context of this research by providing the relevant background information and a summary of some of the previous work that has been done by other researchers in this area of study. Chapter 3 discusses a preliminary case study involving the design space exploration of the Altera Nios soft-core processor using the SEAMO algorithm, which was carried out in order to lead directly into the core of this research. In Chapter 4, the design and implementation of SCBuild are discussed in detail. Chapter 5 presents the results obtained through experimentation using SCBuild and a simple parameterized RISC processor. Finally, Chapter 6 concludes this thesis and discusses possible future work in this area.

## Chapter 2

## Background and Previous Work

In this chapter the background material that is relevant to this research is presented, followed by a brief summary of previous work that has been done in this area. This chapter begins with a discussion of the different classes of intellectual property cores that exist at the various levels of abstraction. Then the parameterization of IP cores is defined, followed by a discussion of several prominent examples of parameterized soft-core processors from the industrial and open-source communities. Next, the basic concepts of FPGA technology are briefly explained, followed by an introduction to design space exploration and multi-objective optimization. Finally, this chapter concludes with a presentation of previous work that is closely related to this research.

### 2.1 Intellectual Property (IP) Cores

The definition of the term "intellectual property" is a broad one and covers a wide range of products and ideas across numerous fields of research. However, in the context of this research, the term refers to reusable hardware or software building blocks that have been pre-designed and pre-tested prior to deployment in a design [64, 34]. These building blocks are usually the property of a particular individual or organization who licenses designers to use their hardware and software blocks. This idea of reuse is certainly not a new one; relying on past knowledge and experience has led to virtually all of the great discoveries and advancements over the course of history. For example, in the area of software development, programmers and software engineers have been collecting useful functions together into libraries for a long time. In the context of hardware design for embedded systems, the term "IP core" refers to reusable hardware components that are ready to be placed into a design with little or no modification made to them. Hardware IP cores can be any of a number of different types of digital components, including full microprocessors. These cores can come in the form of descriptions of hardware at the various levels of abstraction in the digital abstraction hierarchy, as will be discussed in the next section.

### 2.1.1 The Digital Abstraction Hierarchy

Any digital system can be described at different levels or layers of abstraction. Bell and Newell [11] were some of the first writers to formally discuss the hierarchy of abstraction levels in the context of digital system design. This hierarchy also appears in updated form in later literature [50, 65, 61]. The hierarchy includes the five major levels of abstraction shown in Table 2.1, and each level is characterized by a distinct class of languages that are used to represent the behaviour and structure of the system. Behaviour refers to the way that the system or its components interact with their environment, while structure refers to the set of interconnected components that make up the system. A description of the behaviour and structure of the system can be made at any one of these abstraction levels, and the process of translating a higher-level description to a lower-level description is generally known as synthesis

Table 2.1: The Digital Design Hierarchy [11, 50, 65, 61]

| Level                   | Behaviour               | Structure                  |

|-------------------------|-------------------------|----------------------------|

| System (Architecture)   | Communicating Processes | Processors, Memories .     |

| Algorithm (Program)     | Programming Languages   | Data Structures            |

| Register Transfer (RTL) | Register Transfers      | Registers, ALUs, MUXes     |

| Logic (Gate)            | Boolean Equations       | Logic gates, Flip-flops    |

| Circuit (Layout)        | Circuit Equations       | Interconnected Transistors |

[50].

Starting from the highest, the five levels of system abstraction are the System level (also known as the Architecture level), the Algorithm (or Program) level, the Register Transfer level (RTL), the Logic (Gate) level, and the Circuit (or Layout) level.

At the Circuit Level, the system is viewed as a circuit consisting of a collection of interconnected transistors and their physical layout on an IC chip. All signals in the system at this level are continuously varying quantities, so the behaviour of the system can be described using the fundamental equations of circuit analysis. The system's structure may be described symbolically using a schematic or layout diagram.

At the Logic Level, it is assumed that all signals in the system are discrete variables that can take on one of two values: 1 or 0 (or alternatively, high or low). This allows the system to be described in terms of its logical behaviour using Boolean equations. The structure of the system is described as a combinational or sequential circuit consisting of primitive logic components such as gates and flip-flops and their associated set of interconnections.

As its name implies, at the Register Transfer Level the behaviour of the system is expressed as a set of data transfers between storage registers. The system performs a set of discrete *micro-operations*, in which the data stored in the registers

are manipulated or combined with other data and then stored in another register. Structurally, the system consists of any number of registers and functional units such as arithmetic logic units (ALUs) connected together by buses. In general, hardware description languages such as VHDL, Verilog [55] and others can be used to describe the structure and behaviour of digital hardware components at this level.

When viewed at the Algorithm Level, the system is seen as a collection of data structures such as variables stored within a memory block and the instructions that operate on those variables. Instructions are formed when micro-operations at the Register Transfer Level are combined to form complete operations, such as the addition of two numbers or the transfer of data to and from memory. A collection of these instructions form a complete *instruction set*, which is the base language for describing system behaviour at this level. The instructions are executed sequentially, which is unique to this level, since at all levels below the Algorithm level, the behaviour of the system is expressed as a set of events occurring in parallel. Within this level, there is a sub-hierarchy of languages that are used to express the functionality of a program. High-level languages such as C/C++ [43], Visual Basic [21], etc. are translated down to assembly language by a compiler, which is, in turn, translated to machine code by an assembler.

Finally, at the System Level, the structure of the system is depicted as a set of abstract processing elements interacting with one another and the external environment. At this level, a designer would be concerned with overall system architecture and information flow between the processors, the memory and their interface to the surrounding environment (i.e. I/O).

#### 2.1.2 Classes of Hardware IP Cores

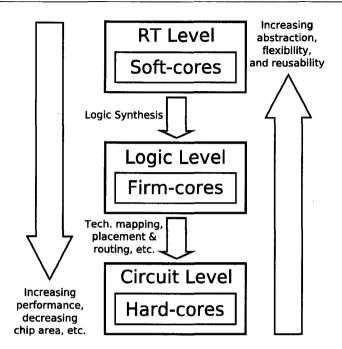

In general, there are three major classes of hardware IP cores available: hard-cores, firm-cores and soft-cores [64, 34]. These different classes represent descriptions of

Figure 2.1: The Three Classes of Hardware IP Cores

hardware components at different levels of abstraction. Hard-cores are Circuit-level descriptions of components and are optimized for a particular target IC technology and include information regarding the physical layout of the core on a chip. Firm-cores are pre-synthesized Logic-level netlist descriptions of digital components that are ready for technology mapping, placement and routing on a given target IC process. Finally, soft-cores are components that are described at the Register Transfer Level using a synthesizable subset of a hardware description language. A soft-core description of a component can translated into a firm-core using a hardware synthesis tool such as Synopsys Design Compiler [39], Altera's Quartus II software [18], Xilinx Synthesis Technology (XST) [41], or the like. Subsequently, a firm-core description can then be translated into a hard-core through the process of technology mapping, which maps generic logic primitives such as gates and flip-flops onto particular physical implementations of those primitives. This process of translating a higher-level

description to a lower level description is illustrated in Figure 2.1.

This research focuses exclusively on the development of soft-core hardware components. Using soft-core components in designs holds a number of distinctive advantages to the designer. First, soft-cores are flexible and can be customized for a specific application with relative ease. Second, they are technology independent in that they can be synthesized for virtually any desired Application Specific Integrated Circuit (ASIC) or FPGA technology. Third, due to their technology independence, they are more immune to becoming obsolete as technology changes when compared with Circuit- or Logic-level descriptions of a component. Fourth, since a soft-core's structure and behaviour are described at a higher abstraction level using an HDL, it becomes much easier to understand the overall design of the component. Fifth, since they are written using an HDL, designing them often resembles the process of software development. Also, as an added benefit, software tools can be created to automatically generate the HDL code of a soft-core component. Finally, due to their flexibility, they can be easily parameterized, thus greatly enhancing their reusability and applicability across a wider range of designs and applications.

# 2.2 Parameterization: Increasing the Reusability of an IP Core

A parameterized core is a hardware component whose architectural features can be varied to a certain extent. A parameter is a particular feature or aspect of the component's architecture that can be changed and assigned particular values from a finite set by the embedded system designer [76, 29]. Examples of parameters include variable bus widths, functional unit implementations, hardware algorithms, memory sizes, pipeline depth, etc. Assigning values to all of the parameters of a component produces one configuration. Parameterizing a core greatly expands its versatility and

usefulness in a wider range of applications.

There are two different types of parameters: static parameters and dynamic parameters [29]. Static parameters must be set prior to the fabrication of the chip and often take the form of "generic" or statements within a VHDL description [54] of a soft-core component, or "parameter" statements in Verilog [55]. In contrast, dynamic parameters are those that can be set after the chip is fabricated, provided the chip has the facilities for supporting various parameter settings. Dynamic parameters are especially useful for parameterizing hard and firm-core components. For this research only static parameters of soft-core components will be considered.

Many of the parameters of a core often share interdependencies with one another. Assigning a value to one parameter will affect the choice of value assignments for other parameters, therefore the value assignments of interdependent parameters should be considered simultaneously. These interdependencies can either be *soft* or *hard* dependencies [29]. Soft interdependencies dictate that the value assignments of dependent parameters should be done at the same time in order to achieve optimal system performance, power consumption and IC area utilization. On the other hand, hard interdependencies require simultaneous parameter assignments if a valid and feasible design configuration is to be chosen.

Parameters of a soft-core hardware component are especially valuable to an embedded systems designer, since they give them the flexibility to customize the core as they desire in order to better fit the target application without having to manually rewrite large portions of the core's underlying HDL source code. Often, if the parameters of a core significantly affect its underlying structure, then it may be necessary to use a software-based HDL code generator program to customize the code automatically.

### 2.3 Soft-core Processors

A soft-core can be a description of virtually any digital hardware component, including a full microprocessor. For many of the reasons mentioned above, soft-core processors are a popular choice for embedded systems designers. Several examples of commercial and open-source soft-core processors will be discussed below [67].

### 2.3.1 Examples of Soft-core Processors

Altera Corporation [70] is an industry leader in programmable logic technology, specializing in FPGAs and other programmable logic devices. They are the makers of the Stratix and Cyclone Series of FPGAs [22]. They also provide numerous soft IP cores that are specifically designed to target their devices. Their flagship IP core is the Nios II soft-core processor [71], which is a general-purpose RISC processor that is optimized for embedded applications. This core consists of three processor variants that can be selected based on a designer's specific needs: the Nios II/f fast core, which is designed for maximum performance, the Nios II/e economy core, which is the smallest processor core, and the Nios II/s standard core, which is a tradeoff between the fast core and the economy core. These cores each feature their own set of configurable options, and all of them provide support for up to 256 custom instructions and interfacing to peripheral devices using the automatically-generated Avalon bus [3]. The Nios II processor is the successor to the original Nios [17], and features improvements over the original design that are aimed at providing better performance and FPGA area utilization. Designers working with the Nios II processor can use the Quartus II CAD tool suite [7] with System on a Programmable Chip (SOPC) Builder [19] to instantiate one or more processor cores into an embedded system design and connect them to other peripheral components, such as timers, universal asynchronous receiver/transmitters (UARTs) and memories.

MicroBlaze [73] is a 32-bit parameterized soft-core RISC processor provided by Xilinx Incorporated [40] that is targeted for Xilinx FPGAs and optimized for embedded applications. Its fixed features include 32-bit instructions, a 5-stage single-issue pipeline, a thirty-two general-purpose registers and a 32-bit address bus for data and instruction memories. The latest version of MicroBlaze (v5.00a at the time of this writing) also includes a large number of parameters, including an optional hardware barrel shifter, multiplier, divider, floating point unit (FPU), and others. Memory can reside on-chip or as an external peripheral. On-chip memory can be accessed by MicroBlaze using a Local Memory Bus (LMB), which provides single-cycle access to the memory. Also, the a general purpose interface known as the On-chip Peripheral Bus (OPB) can be used to interface MicroBlaze with memories and other peripheral components.

In addition to commercially available soft-core processors, there are numerous cores available from various open-source communities on the internet. Many of these cores can be downloaded, modified, and used in designs free of charge. Opencores.org [56] contains a large number of soft-core hardware components that have been developed by people all across the world. A number of open-source microprocessors are available, including the OpenRISC 1200 processor [2], which is a 32-bit RISC processor with a 5-stage pipeline and basic digital signal processing (DSP) functionality. Other examples of open-source soft-core processors include Qrisc [62], and the LEON3 processor by Gaisler Research [63].

### 2.4 FPGA Technology

Field programmable gate arrays are a specific class of programmable logic device that are designed to be programmed and reprogrammed to act like virtually any digital circuit that can be conceived, subject to logic capacity limitations. They are becoming an increasingly popular choice for embedded systems designers who want a

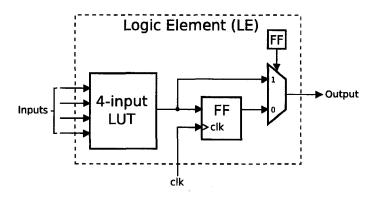

Figure 2.2: Schematic of a Generic FPGA Logic Element (LE) [42]

medium for prototyping and implementing soft-core hardware components. Soft-cores and FPGAs often go hand-in-hand. In fact, it is quite common for companies who manufacture FPGAs to also provide their own soft-cores that target their devices as well, with Altera Corporation [70] and Xilinx Incorporated [40] being the two largest and best-known examples.

The design of an FPGA differs between various manufacturers and also between different device families. However, in general, an FPGA is an IC chip that consists of an array of programmable blocks, often referred to as Logic Elements (LEs), which are connected to each other by a programmable interconnection network. A basic schematic diagram of an idealized LE is depicted in Figure 2.2 [42]. Although the LEs in the current generation of devices are much more sophisticated, this idealized LE does serve to illustrate the basic idea of how an FPGA works.

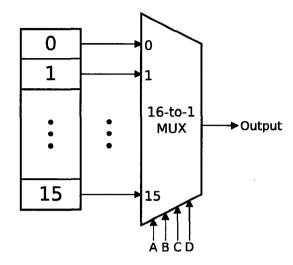

At the core of each LE is a block of programmable memory called a Lookup Table (LUT). The diagram in Figure 2.3 illustrates the essential functionality of an LUT. The LUT consists of an array of 1-bit memories connected to a multiplexed output pin. If the LUT has n inputs, then the memory array will have  $2^n$  bits. This array can be programmed with the truth table of any possible n-input Boolean logic function, and the n multiplexer (MUX) select inputs decide which of the  $2^n$  memory array bits appears at the LUT output. For example, to implement the logic function of a

Figure 2.3: Schematic of a Lookup Table (LUT)

4-input "AND" gate, bits 0 to 14 are programmed with 0's and bit 15 is set to 1. Using this memory array, a total of  $2^{2^n}$  logic functions can be implemented using an n-input LUT.

In order to make the creation of sequential logic circuits possible, the output of an LUT in a Logic Element is connected to a flip-flop (FF). Then the registered and unregistered outputs of the LE are both made available through a 2-to-1 MUX whose select line value is determined by the value stored in a second flip-flop, which is set by a bit-stream when the FPGA device is configured.

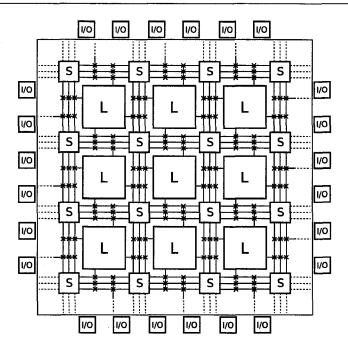

On an FPGA, a large number of LEs are connected together using a network of programmable interconnects, also known as "routing". There are many different types of routing architectures available, but they all have one thing in common: programmability. As depicted in Figure 2.4 [25], the LEs are grouped together into clusters called Logic Blocks (L in the figure) which are surrounded by horizontal and vertical wires on all sides, and special I/O blocks are arranged around the perimeter of the FPGA chip. The output of each Logic Block can be programmed to connect to a set of horizontal and vertical wire segments, and each wire segment can be

Figure 2.4: Generic FPGA Routing Architecture (adapted from [25])

programmed to connect to other wire segments through a Switch Block (S).

By programming both the contents of the Logic Blocks on the FPGA as well as the routing connecting the blocks together, a designer can implement a virtually limitless number of digital hardware circuits. Using an FPGA as an implementation medium offers the distinct advantage of flexibility—if the designer needs to change the circuit on the FPGA, it is merely a matter of reprogramming it. However, this flexibility does come with a cost. Circuits that are implemented on an FPGA will generally take up more chip area, consume more power, and run slower than they would if they were implemented using an ASIC technology. Nevertheless, since FPGAs are a relatively new technology, research is being conducted that aims at closing the performance gap between FPGA and ASIC technologies.

The first FPGAs that were introduced featured relatively small logic capacities and offered only a few basic features. However, as the technology improved, the devices were able to hold increasingly larger circuits and began including a number of more advanced features. Currently, on top of an ever-increasing number of LEs and I/O pins, the latest cutting-edge devices also feature large amounts of on-chip memory and other special-purpose blocks such as dedicated multipliers. In addition to having configurable elements, some FPGAs also feature one or more hard-core processors built right into the device. For instance, the Xilinx Virtex-4 family of FPGAs [57] features two built-in hard-core embedded IBM PowerPC<sup>TM</sup> 405 processors [16], which can be used in any number of embedded applications. These new features serve to substantially improve the performance, area utilization, and power consumption of systems implemented on FPGAs.

The Altera Stratix EP1S40F780C5 FPGA has been selected as the target device used for this research, therefore a brief description of the Stratix architecture [8] is necessary. All of the devices in the Stratix family contain six different types of logic resources: Logic Array Blocks (LABs), M512, M4K, and M-RAM memory blocks, DSP blocks, and I/O Elements (IOEs). LABs are blocks which consist of 10 LEs each and are used to implement user-defined logic functions. The M512 blocks, the smallest memory blocks, each contain 512 bits of memory, plus parity bits, and can be used to provide single-port or simple dual-port memory operation. The M4K blocks are larger than the M512s and feature 4 kilobits of memory each, plus parity. These blocks can be used in single-port, simple dual-port or true dual-port mode. The M-RAM blocks are significantly larger than both the M512 and M4K blocks, containing 512 kilobits of memory each (plus parity). Like the M4K blocks, the M-RAM blocks can be used in single-port, simple dual-port or true dual-port mode. The DSP blocks are special-purpose resources on the device, and can each be used to implement eight  $9 \times 9$ -bit multipliers, four  $18 \times 18$ -bit multipliers, or one  $36 \times 36$ -bit multiplier. Lastly, the IOE elements are connected to the Stratix device pins, and support a number of different I/O standards. All of these resources are arranged in a 2-dimensional rowand column-based structure on the Stratix device. The EP1S40F780C5 device, one of several in the Stratix family, contains exactly 4,125 LABs (or 41,250 LEs), 384 M512s, 183 M4Ks, 4 M-RAMs (for a total of 3,423,744 memory bits), 14 DSP blocks (for a total of 112  $9 \times 9$ -bit multipliers, 56  $18 \times 18$ -bit multipliers or 14  $36 \times 36$ -bit multipliers) and 616 I/O pins [8].

#### 2.5 Design Space Exploration (DSE)

The term design space in the context of digital embedded systems generally refers to the set of all possible system designs; that is, the complete collection of all possible digital hardware and software configurations that will achieve the functionality required to perform the system's intended tasks. When dealing with a complex system like those commonly encountered in the area of embedded systems, the design space is extremely vast and contains a large number of configurations that are sub-optimal for any given application. Therefore, it is essential to the success of any embedded systems design project that the design space be traversed to determine the system design configuration that best suits the intended application. This is, in essence, the main goal of design space exploration.

#### 2.5.1 Multi-objective Optimization

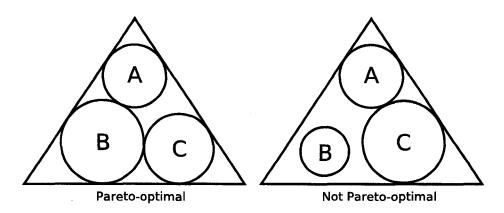

The problem of DSE is essentially a multi-objective optimization problem in which design configurations are chosen so that they provide the best balance between a set of competing *objectives*. Most commonly, these objectives include minimizing IC chip area, reducing power consumption and maximizing system performance. These objectives cannot be optimized independently, since improving one objective will almost always mean sacrificing another. Since several competing objectives are being optimized at once, there is seldom one single "optimal" design configuration for any given multi-objective optimization problem. Instead, there exists a set of configura-

Figure 2.5: The Concept of Pareto-optimality Illustrated (adapted from [60])

tions known as the *Pareto-optimal set* that is a subset of the complete design space. A configuration is said to be Pareto-optimal if you cannot improve one objective without sacrificing another. The concept of Pareto-optimality is illustrated with a geometric example in Figure 2.5 (adapted from [60]).

Suppose in this hypothetical multi-objective optimization problem [60] that the goal was to simultaneously maximize the areas of circles A, B and C within the area of the triangle, with the constraint that the circles must not overlap or pass the boundary of the sides of the triangle. In this case there cannot be just one solution, but rather a multitude. The configuration on the left-hand side of the figure is an example of a Pareto-optimal solution, because you cannot increase the area of any of the circles without decreasing the area of the other two. In contrast, the triangle on the right-hand side is a non Pareto-optimal configuration, because the area of circle B can be increased without affecting the areas of circles A or C.

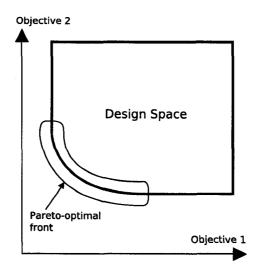

Finding the Pareto-optimal set drastically reduces the size of the design space by eliminating all sub-optimal configurations, allowing the designer to select a single design configuration from the Pareto-optimal set that is well-suited to the intended application. If one were to plot one objective against another on a graph, the result would be something that looks similar to the graph shown in Figure 2.6.

Figure 2.6: Illustration of a 2-Dimensional Design Space

All of the possible design configurations are located within the Design Space region of the graph. Outside of this region, no design configurations can exist. The boundary of the Design Space region at the lower left-hand side nearest to the origin of the graph is referred to as the *Pareto-optimal front*. Design configurations that lie along this boundary line represent the very best configurations of the design space in terms of the objectives across which the graph is plotted. It is this set of configurations that is being sought when Pareto-based design space exploration is performed. Conversely, it is clear that there is also a large space of sub-optimal configurations that exists within the boundaries of the Design Space. Ideally, these configurations can be safely eliminated, or "pruned", from consideration, thus drastically reducing the size of the space that must be explored.

#### 2.5.2 DSE Using Parameterized Cores

In the context of platform-based embedded systems design involving parameterized cores, the goal of DSE is to prune the design space in search of a suitable combination of parameter values for the hardware platform that provides a good balance between

the each of the objectives while satisfying the design constraints imposed by the requirements of a particular application. Many approaches for handling this task have been proposed.

The simplest and most straightforward approach to design space pruning is to exhaustively visit and evaluate each and every combination of parameters in the design space and remove the worst configurations from consideration. Some research has been done on the application of this approach [31, 28]. The obvious drawback to this approach is the fact that it rapidly becomes infeasible to evaluate every configuration as the design space grows. Therefore, this approach is seldom practical on its own, except for very small systems with relatively few parameters, as concluded by Givargis et al [28].

Since the exhaustive approach is so often infeasible, there are a multitude of approaches that have been developed that help to automate the process of DSE of embedded hardware platforms. A good summary of some of these approaches, such as the use of Architectural Description Languages (ADLs), can be found in the literature [32, 66, 53]. For this work one particular approach will be examined: the use of genetic-based algorithms with parameterized cores, as will be discussed in the following sections.

#### Approaches Based on Genetic Algorithms

The idea of a genetic algorithm (GA, sometimes referred to an an evolutionary algorithm or EA) was first proposed by Holland in 1975 [37] and was used primarily in the field of artificial intelligence. However, it was later applied in a wider range of applications and was found to be very effective in solving multi-objective optimization problems, including the problems posed by DSE using parameterized cores. Genetic algorithms are a class of optimization problems that gain their inspiration from the field of biological sciences. There are many variations of the algorithm, but they

all work by attempting to emulate the biological process of natural selection, where stronger members of a population survive and pass on their genes while the weaker members gradually die off. A good overview of genetic and evolutionary algorithms for multi-objective optimization can be found in the literature [26, 14].

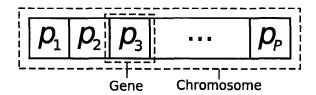

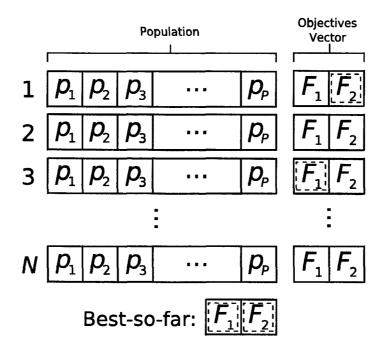

The genetic algorithm starts with and maintains a set of design configurations rather than just a single configuration. This set of configurations is called the population and has a fixed size N. Each member of the population represents one unique design configuration, and is referred to as a chromosome. Each chromosome in the population is made up of a string of symbols that represent the system's parameters. A symbol in the chromosome is called a gene.

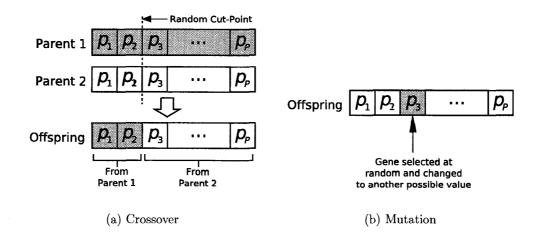

During an iteration or *generation* of the algorithm, each chromosome is evaluated according to its "fitness", where fitness is a measure of how well the configuration meets the problem objectives. Pairs of chromosomes are selected to become *parents* of offspring through reproduction. During this process, features from both parents are combined to form the offspring using the genetic operators: crossover and mutation. During crossover, the genes of the parents are combined to form a new chromosome, called the offspring. The mutation operator produces random changes in a single chromosome without producing offspring.

A new generation of chromosomes is formed through the production of numerous offspring from the set of parents. Since the population has a fixed size, N chromosomes of the total number of parent and offspring chromosomes are selected to survive to the next generation; the rest are discarded. The N surviving chromosomes can either be selected randomly from the full set, or selected based on fitness. After several generations of the algorithm, the population of configurations should converge toward an optimal configuration set.

#### 2.6 Closely Related Work

Yiannacouras [75] developed SPREE, the Soft Processor Rapid Exploration Environment, in order to facilitate the exploration of the design space for soft-core processors targeted for implementation on an FPGA. SPREE consists of a hardware Component Library and an RTL Generator. The RTL Generator fetches hardware components from the library and builds a datapath according to a special Architectural Description which is given to the RTL Generator as an input. The RTL Generator then creates the corresponding control logic, either pipelined or unpipelined, yielding a complete soft-core processor. The generated processors were based on the MIPS-I [35] instruction set architecture. The SPREE system was used to investigate several soft-core processor architectural alternatives including hardware versus software multiplication, different shifter implementations, varying pipeline depths, as well as some other interesting architectural tradeoffs. One major difference between the SPREE system and this present work is the exploration methodology. The SPREE system uses an exhaustive exploration strategy, in which the user must manually explore the various design tradeoffs by developing different architectural descriptions for each processor variant. In contrast, this research applies an automated approach based on a genetic algorithm to explore the design space of a heavily parameterized soft-core description.

The Platune system [30] is an environment that allows an embedded system designer to tune the parameters of a parameterized hardware platform. The system provides a set of simulation and power models for the components of a parameterized system consisting of a MIPS R3000 processor [35] with instruction and data caches, on-chip memory, and a set of interconnecting buses. The simulation models are used to compute the execution time of a specific program running on the processor and to gather information on the power consumption of the system. Platune also features a design space exploration framework that uses a parameter interdependency model

and an exhaustive approach to determine the Pareto-optimal set of configurations. A graph of parameter interdependencies is created, and interdependent parameters are gathered together into clusters. Then an exhaustive exploration approach is applied to each cluster to determine its local Pareto-optimal set. Once each cluster has been searched, pairs of clusters are merged together, and the exhaustive search is applied to the merged clusters. This process continues until a single cluster remains, and the Pareto-optimal set of configurations is determined. In contrast to the Platune system, this work features a GA-based approach to search the design space for the Pareto-optimal set. Additionally, the Platune system is directed specifically toward the use of the MIPS R3000 processor model, which is not designed specifically for FPGA implementation. In this research, a general framework for the design space exploration of any parameterized core has been established, with emphasis on soft-cores targeted for implementation on an FPGA.

Palesi and Givargis [59] present an approach to explore the design space of heavily parameterized systems using a genetic algorithm, namely the Strength Pareto Evolutionary Algorithm 2 (SPEA2) [77]. The approach combines the parameter dependency clustering and exhaustive search method used by Platune with the genetic-based SPEA2 algorithm to reduce the time needed to find the Pareto-optimal set of configurations. Their results indicate that an approximated Pareto-optimal set that is within 1% of the actual set can be obtained using the combined approach while reducing the amount of simulation time required to determine the set by 80%. Ascia et al [10] later use the SPEA2 algorithm directly with the Platune system to search for the Pareto-optimal set of configurations. These researchers provide some useful conclusions about the use of genetic-based algorithms in platform-based design problems. However, they do not focus specifically on the exploration of the design space of soft IP cores targeted for FPGAs.

The PEAS-III system by M. Itoh et al [44] is a System-level design environment

that enables designers to quickly explore the design space of pipelined embedded processors. The system is based on the micro-operation description of instructions, which allows designers to concentrate on the design of a processor's instruction set. A pipelined processor is built from a series of pipeline stage models. Each stage model represents a single stage in the pipeline and consists of pipeline resources such as ALUs and other functional units, inter-stage pipeline registers, a stage controller and the interconnections between them. The PEAS-III system creates a datapath and associated control logic by cascading the stage models in series. Two VHDL descriptions of the processor are generated by the system: a non-synthesizable model used purely for simulation and a version intended for synthesis. In order to evaluate the effectiveness of PEAS-III, several processors were built using the system, including a MIPS R3000 processor, a DLX processor [36], and a simple RISC controller. The PEAS-III system does not utilize any form of automated design space exploration, thus distinguishing it from this present research.

#### 2.7 Summary