### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1-1-2007

### DNLMS-based adaptive filters for echo cancellation.

Raymond Lee University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Lee, Raymond, "DNLMS-based adaptive filters for echo cancellation." (2007). *Electronic Theses and Dissertations*. 7123.

https://scholar.uwindsor.ca/etd/7123

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### DNLMS-based Adaptive Filters for Echo Cancellation

by

#### Raymond Lee

A Thesis Submitted to the Faculty of Graduate Studies and Research through Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2007

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada

#### Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-42314-1 Our file Notre référence ISBN: 978-0-494-42314-1

### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### $\bigodot$ 2007 Raymond Lee

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

# Abstract

Power consumption is a main issue with echo canceller implementation due to the use of high-order adaptive filters. The normalized least-mean-square (NLMS) algorithm is an adaptive filtering algorithm typically used in echo cancellation, but does not permit pipelining, a technique that facilitates low-power filter architectures. This limitation can be overcome by using the delayed NLMS (DNLMS) algorithm. There are two objectives of this thesis related to the implementing a DNLMS adaptive filter for echo cancellation.

The first objective is to apply computationally-efficient techniques to the DNLMS algorithm to reduce power and/or area consumption. The considered techniques either simplify computationally-intensive operations or schedule less filter coefficient updates.

The second objective is to present the hardware implementation of a pipelined DNLMS adaptive filter. The implemented design is pipelined, modular, low-latency, and portable. The design methodology consists of fixed-point and RTL simulations, physical synthesis for the Altera Stratix FPGA, and hardware verification. To my family for their everlasting support.

v

# A cknowledgments

I would like express my sincere gratitude for the encouragement and guidance given to me by my advisors, Dr. Esam Abdel-Raheem and Dr. Mohammed A. S. Khalid. I feel very fortunate to have had two supportive and patient advisors. It has been a pleasure working with both of you. I would also like to express my gratitude to the other members of my committee, Dr. Kemal E. Tepe and Dr. Alioune Ngom, for their kindness, flexibility, and helpful feedback. Also, I would like to thank Academy Publisher for allowing me to include material from the Journal of Communications in my thesis.

Of course, I have to thank my fellow graduate students of the ECE department. Their support and advise was critical to my development as graduate student. Their company and great sense of humour was vital to me keeping my sanity. Who knew that a group of such big, gigantic nerds could be so much fun? There are a lot of people I will need to thank, but special recognition goes to Kevin Banović and Harb Abdulhamid. Working along side them in 268 EH wasn't just fun, it was a privilege.

Finally, I would like to dedicate this thesis to my family. I have received a lot of support from different sources, but their daily support in my life is the one that I am most thankful for.

# Contents

| A        | bstra          | let                                | iv           |

|----------|----------------|------------------------------------|--------------|

| D        | e <b>di</b> ca | tion                               | $\mathbf{v}$ |

| A        | ckno           | wledgments                         | vi           |

| Li       | st of          | Figures                            | ix           |

| Li       | st of          | Tables                             | xi           |

| Li       | st of          | Abbreviations                      | xii          |

| Li       | st of          | Symbols                            | xiv          |

| 1        | Intr           | oduction                           | 1            |

|          | 1.1            | Background on Echo Cancellation    | 1            |

|          | 1.2            | Thesis Objectives                  | 4            |

|          | 1.3            | Thesis Organization                | 5            |

| <b>2</b> | Rev            | view of Adaptive Filtering         | 6            |

|          | 2.1            | Fundamentals of Adaptive Filtering | 6            |

|          | 2.2            | The Method of Steepest-Descent     | 10           |

|          | 2.3            | Least-Mean-Square Algorithm        | 11           |

|          |                |                                    |              |

vii

|   | 2.4           | Norm    | alized Least-Mean-Square Algorithm                           | 12        |

|---|---------------|---------|--------------------------------------------------------------|-----------|

|   | 2.5           | Delay   | ed Weight Adaptation                                         | 13        |

| 3 | Cor           | nputat  | tionally-efficient DNLMS-based Algorithms                    | 14        |

|   | 3.1           | Comp    | utationally-efficient techniques                             | 14        |

|   |               | 3.1.1   | Power-of-two Quantization                                    | 16        |

|   |               | 3.1.2   | M-Max Algorithm                                              | 17        |

|   |               | 3.1.3   | Stop-and-go Algorithm                                        | 18        |

|   |               | 3.1.4   | Proposed Algorithm                                           | 20        |

|   | 3.2           | Simul   | ation Results                                                | 21        |

|   |               | 3.2.1   | Network Echo Cancellation with White Gaussian Input          | 23        |

|   |               | 3.2.2   | Network and Acoustic Echo Cancellation with Composite Source |           |

|   |               |         | Signal Input                                                 | 27        |

| 4 | FP            | GA In   | plementation of Pipelined DNLMS Adaptive Filter              | <b>32</b> |

|   | 4.1           | Archi   | tecture Derivation                                           | 33        |

|   | 4.2           | Design  | n Methodology for FPGA Implementation                        | 39        |

|   |               | 4.2.1   | Fixed-Point Simulations                                      | 40        |

|   |               | 4.2.2   | RTL Simulations                                              | 41        |

|   |               | 4.2.3   | Synthesis and Hardware Verification                          | 44        |

| 5 | Cor           | nclusio | ns and Future Work                                           | 51        |

| R | efere         | nces    |                                                              | 54        |

| A | $\mathbf{Ma}$ | tlab So | ource Code                                                   | 57        |

| в | Ver           | ilog So | ource Code                                                   | 84        |

| V | ITA           | AUCI    | TORIS                                                        | 104       |

viii

# List of Figures

| 1.1 | Network echoes over the PSTN                                                 | 2  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Echo cancellation system model                                               | 3  |

| 1.3 | Acoustic echoes                                                              | 4  |

| 2.1 | Adaptive linear combiner.                                                    | 7  |

| 2.2 | Mean-square error surface.                                                   | 9  |

| 3.1 | Transfer characteristic of POT quantizer for $a=2,b=2,$ and $\tau=0.$ .      | 16 |

| 3.2 | Echo path impulse responses.                                                 | 24 |

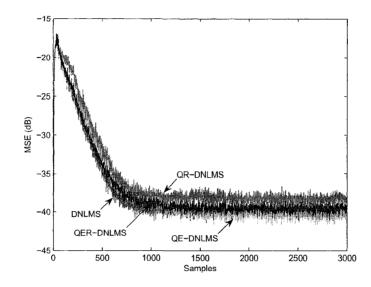

| 3.3 | $\operatorname{MSE}$ curves of DNLMS under different quantization algorithms | 25 |

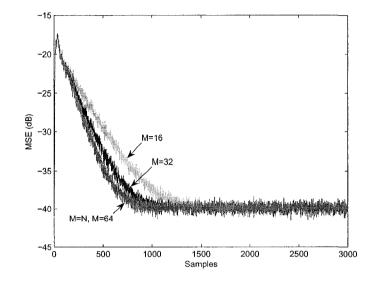

| 3.4 | MSE curves of M-Max-DNLMS for different $M$ 's                               | 26 |

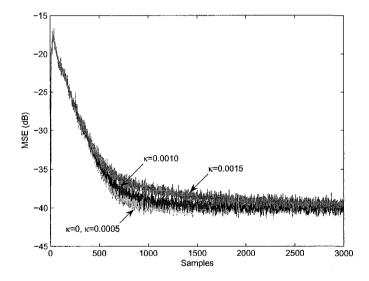

| 3.5 | MSE curves of SAG-DNLMS for different $\kappa$ 's                            | 26 |

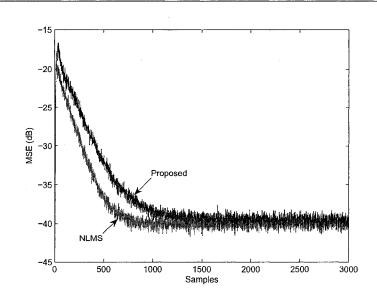

| 3.6 | MSE curves of NLMS and Proposed algorithm.                                   | 27 |

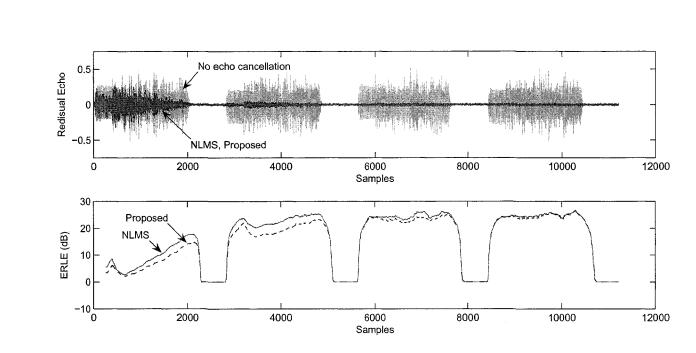

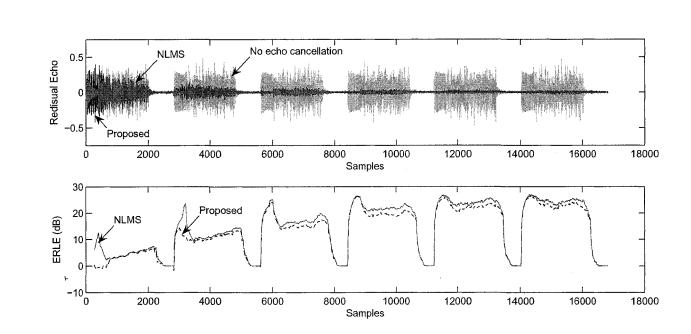

| 3.7 | Residual echo and ERLE of NLMS and proposed algorithm for NEC                |    |

|     | simulation                                                                   | 29 |

| 3.8 | Residual echo and ERLE of NLMS and proposed algorithm for AEC                |    |

|     | simulation.                                                                  | 30 |

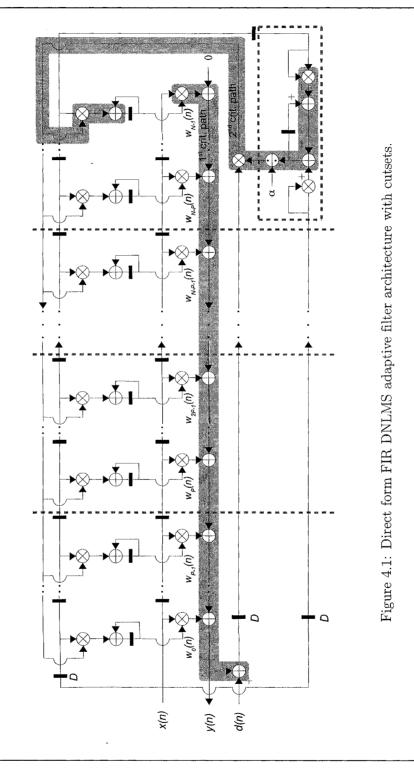

| 4.1 | Direct form FIR DNLMS adaptive filter architecture with cutsets              | 35 |

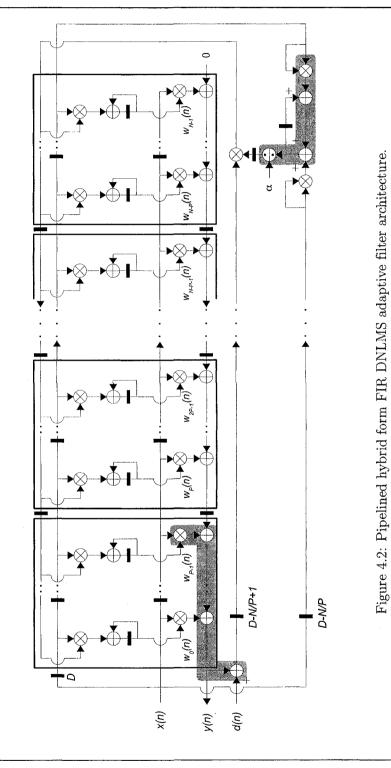

| 4.2 | Pipelined hybrid form FIR DNLMS adaptive filter architecture                 | 36 |

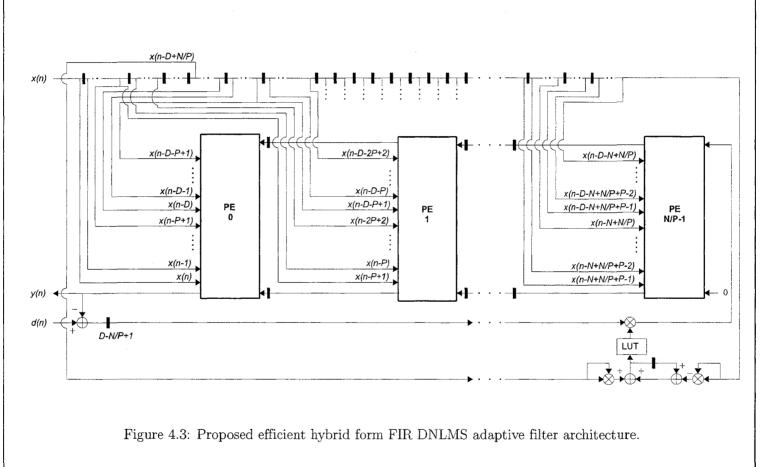

| 4.3 | Proposed efficient hybrid form FIR DNLMS adaptive filter architecture.       | 37 |

#### LIST OF FIGURES

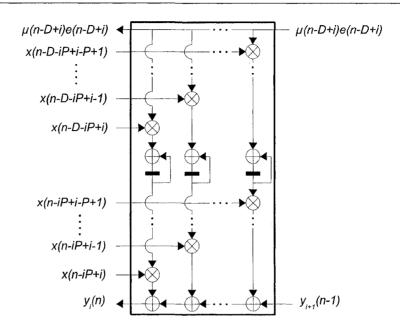

| 4.4  | The $i^{th}$ PE of the efficient hybrid form FIR DNLMS adaptive filter |    |

|------|------------------------------------------------------------------------|----|

|      | architecture.                                                          | 38 |

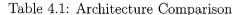

| 4.5  | Design methodology.                                                    | 39 |

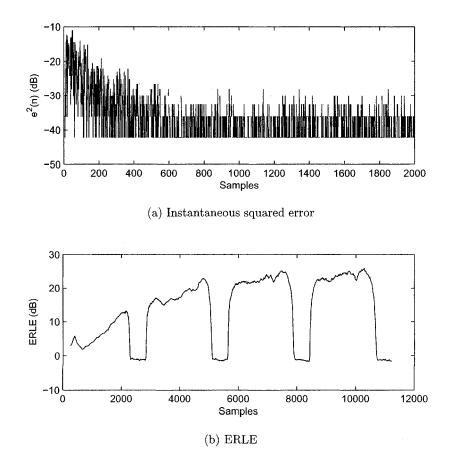

| 4.6  | Results from fixed-point simulations.                                  | 42 |

| 4.7  | Results from RTL simulations                                           | 43 |

| 4.8  | Waveforms from RTL simulation results.                                 | 45 |

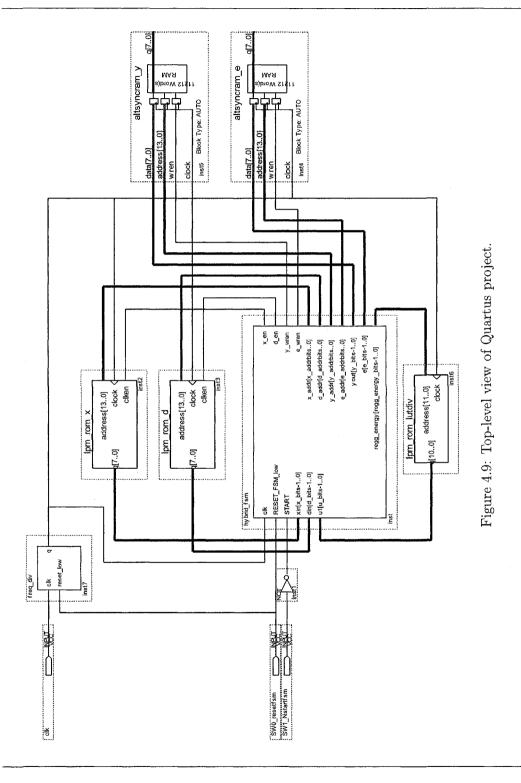

| 4.9  | Top-level view of Quartus project                                      | 46 |

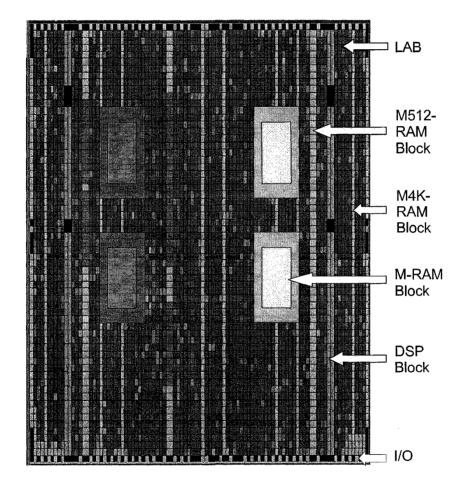

| 4.10 | Post-fitting chip view illustrating resource utilization               | 48 |

| 4.11 | Captured waveforms from hardware implementation                        | 49 |

| 4.12 | Results from hardware simulations.                                     | 50 |

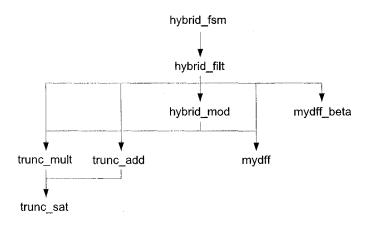

| B.1  | Hierarchy of Verilog modules                                           | 84 |

# List of Tables

| 3.1 | Number of Operations Executed over $m$ input samples $\ldots \ldots \ldots$ | 22 |

|-----|-----------------------------------------------------------------------------|----|

| 3.2 | Impact of SAG algorithm under WGN input                                     | 25 |

| 3.3 | Impact of SAG on Proposed algorithm under CSS input                         | 28 |

|     |                                                                             |    |

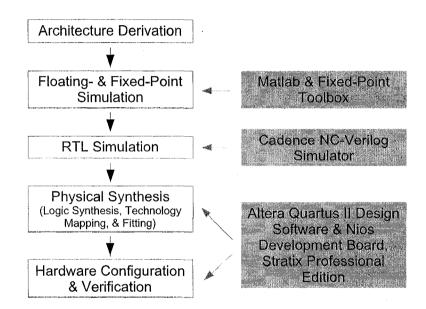

| 4.1 | Architecture Comparison                                                     | 39 |

| 4.2 | Signal Wordlengths                                                          | 41 |

| 4.3 | FPGA Resource Utilization                                                   | 47 |

xi

# List of Abbreviations

| Abbreviation         | Definition                                             |

|----------------------|--------------------------------------------------------|

| AĘC                  | Acoustic echo cancellation.                            |

| ALC                  | Adaptive linear combiner.                              |

| $\operatorname{CAD}$ | Computer-aided design.                                 |

| CMOS                 | Complementary metal-oxide semiconductor.               |

| $\mathbf{CSS}$       | Composite source signal.                               |

| DLMS                 | Delayed least-mean-square.                             |

| DNLMS                | Delayed normalized least-mean-square.                  |

| DSP                  | Digital signal processor or digital signal processing. |

| $\mathrm{DTD}$       | Double-talk detector.                                  |

| $\operatorname{DUT}$ | Design under test.                                     |

| $\mathbf{ERL}$       | Echo return loss.                                      |

| ERLE                 | Echo return loss enhancement.                          |

| $\operatorname{FIR}$ | Finite-duration impulse response.                      |

| FPGA                 | Field programmable gate array.                         |

| FSM                  | Finite-state machine.                                  |

| HDL                  | Hardware description language.                         |

| i.i.d.               | Independent and identically distributed.               |

| I/O                  | Input/output.                                          |

| $\operatorname{ITU}$ | International Telecommunications Union.                |

| LAB                  | Logic array block.                                     |

| LE                   | Logic element.                                         |

| LEM                  | Loudspeaker-enclosure-microphone.                      |

| LMS                  | Least-mean-square.                                     |

| LUT                  | Look-up-table.                                         |

| MSE                  | Mean-squared error.                                    |

xii

| Abbreviation         | Definition                         |

|----------------------|------------------------------------|

| NEC                  | Network echo cancellation.         |

| NLMS                 | Normalized least-mean-square.      |

| $\rm PE$             | Processing element.                |

| POT                  | Power-of-two.                      |

| $\mathbf{PSTN}$      | Public switched telephone network. |

| QE                   | Quantized-Error.                   |

| QER                  | Quantized-Error-Regressor-energy.  |

| QR                   | Quantized-Regressor-energy.        |

| RAM                  | Random access memory.              |

| ROM                  | Read-only memory.                  |

| $\operatorname{RTL}$ | Register transfer level.           |

| SAG                  | Stop-and-go.                       |

| $\operatorname{SNR}$ | Signal-to-noise ratio.             |

| VoIP                 | Voice over Internet protocol.      |

| WGN                  | White Gaussian noise.              |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# List of Symbols

| Symbol              | Definition                                                     |

|---------------------|----------------------------------------------------------------|

| a                   | Number of integer bits, excluding the sign bit.                |

| b                   | Number of fractional bits.                                     |

| d                   | Desired response input.                                        |

| e                   | Error signal.                                                  |

| n                   | Time index.                                                    |

| $\mathbf{p}$        | Cross correlation vector.                                      |

| s                   | Near-end signal.                                               |

| x                   | Input signal.                                                  |

| х                   | Input signal vector or regressor.                              |

| w                   | Weight.                                                        |

| w                   | Weight or coefficient vector.                                  |

| y                   | Output signal.                                                 |

| $\ \mathbf{x}(n)\ $ | Regressor energy.                                              |

| D                   | Adaptation delay.                                              |

| M                   | Parameter of M-Max algorithm; number of weights to be updated. |

| N                   | Filter order.                                                  |

| P                   | Number of weights per PE.                                      |

| $\mathbf{R}$        | Input correlation matrix.                                      |

| $\alpha$            | Convergence parameter of NLMS algorithm.                       |

| eta                 | Parameter of NLMS algorithm.                                   |

| $\nabla$            | Gradient vector of performance function.                       |

| $\kappa$            | SAG-threshold.                                                 |

| $\lambda_{max}$     | Largest eigenvalue of $\mathbf{R}$ .                           |

| $\mu$               | Adaptation step-size.                                          |

| $\tau$              | Smallest magnitude value allowed for POT quantization.         |

$\operatorname{xiv}$

| Symbol                     | Definition                              |

|----------------------------|-----------------------------------------|

| ζ                          | Mean-square error performance function. |

| $\zeta_{min}$              | Minimum mean-square error.              |

| $E\left[\cdot ight]$       | Expectation operator.                   |

|                            | $l_2$ norm operation.                   |

| $sgn\{\cdot\}$             | Sign function.                          |

| $\operatorname{tr}[\cdot]$ | Trace of a matrix.                      |

| $(\cdot)^T$                | Transposition.                          |

# Chapter 1

## Introduction

#### 1.1 Background on Echo Cancellation

Echoes are delayed or distorted versions of a sound or signal that have been reflected back to the source [21]. For small round trip delays, echoes are interpreted as reverberations. In conversations, people usually prefer the presence of reverberations over an anechoic environment. However, when round trip delays are longer than a few tens of milliseconds, echoes become distinct and disruptive [14]. The two types of echoes considered in telecommunications are network echoes and acoustic echoes.

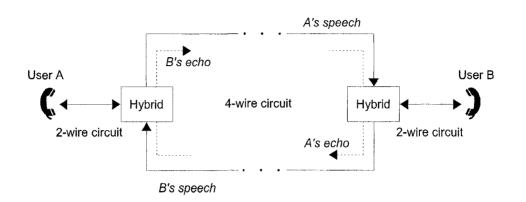

Network echoes appear in telephone calls over the public switched telephone network (PSTN). The link connecting two users is comprised of a two-wire line that connects each phone to its respective local central office and two separate unidirectional lines that make a four-wire inter-office link, as shown in Fig. 1.1. The hybrid transformer is the device that connects the two-wire circuit to the four-wire circuit. Ideally, the hybrid would transfer all energy from the incoming signal on the four-wire

1

Figure 1.1: Network echoes over the PSTN.

circuit to the two-wire circuit. However, due to imperfect impedance matching, some of the energy is reflected back to its source on the four-wire circuit as an echo [31]. Thus, network echoes arise from hybrid devices. For roundtrip delays less than 100 ms duration, echo suppressors were used to suppress network echoes [33]. However, when the round-trip delay exceeded 100 ms, as was the case with the incorporation of satellite links, network echo cancellation (NEC) was required.

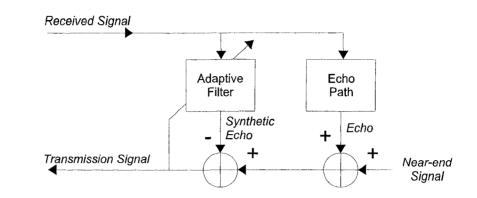

The echo canceller was first introduced in the 1960's by Sondhi [30] and concurrently by Becker and Rudin [8]. The basic principle of echo cancellation is to eliminate the echo from the transmission signal by subtracting a synthesized replica. In order to create the synthetic echo, the unknown time-varying echo path impulse response is modelled using an adaptive filter. Typically, an adaptive filter on the order of hundreds is needed for NEC [21].

Figure 1.2 shows the system model of echo cancellation. When excited by the received signal, the adaptive filter outputs a synthetic echo. By subtracting the synthetic echo, the genuine echo is effectively removed prior to transmission. Usually during adaptation, the near-end signal is assumed to be simply noise. This is a reasonable assumption because a double-talk detector (DTD) is usually implemented to pause the adaptive filter's adaptation, in order to avoid divergence, when both

Figure 1.2: Echo cancellation system model.

received and near-end signals are present, i.e. during double talk [14].

Recently, NEC has received renewed attention with the introduction of voice over Internet protocol (VoIP) [19, 29]. In this application, the packet-switched network is connected to the PSTN through a voice gateway. Network echoes are a problem for VoIP because, irrespective of whether the call is local or long distance, the round trip delay is always large as a result of the inherent large delay in the packet-switched network which includes encoding, jitter buffer, and network propagation delays.

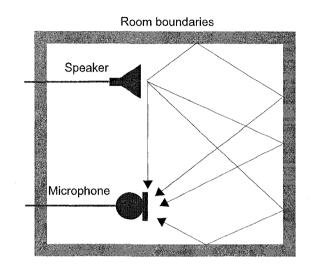

An adaptive filter can be similarly applied to eliminate acoustic echoes in acoustic echo cancellation (AEC). Acoustic echoes arise in applications such as teleconferencing and hands-free telephony, where there is a loudspeaker-enclosure-microphone (LEM) system. An electro-acoustic coupling between the loudspeaker and the microphone results in the microphone picking up signals from the loudspeaker as well as signal reflections off surrounding objects and boundaries [9], as illustrated in Fig. 1.3. AEC presents a more challenging problem compared to NEC because acoustic echoes are generally longer, requiring an adaptive filter on the order of thousands [14].

Figure 1.3: Acoustic echoes.

### 1.2 Thesis Objectives

The normalized least-mean-square (NLMS) algorithm is a commonly used adaptive filtering algorithm for echo cancellation [14]. However, a variant of the NLMS algorithm, the delayed normalized least-mean-square (DNLMS) algorithm [3], is of interest because it allows pipelining, a useful filter design technique suitable for low-power or high-speed applications [22]. With the DNLMS algorithm as the algorithm of choice, this work addresses two issues related to the implementation of an adaptive filter for echo cancellation.

The first issue is the requirement of high-order adaptive filters for echo cancellation. Such large filters have high computational requirements, i.e. a large number of multiplications, divisions, and additions/subtractions occur within one clock period. This translates to large resource demands and high power consumption, thus making implementation challenging. The second issue is that, to this date, there has been little work in presenting architectures for DNLMS adaptive filters [23, 26, 27], none of which present implementation details. Thus, this work has two objectives.

- 1. Reducing the computational demand of the DNLMS algorithm through the application of computationally-efficient techniques.

- 2. Presenting the field programmable gate array (FPGA) implementation of a pipelined DNLMS adaptive filter.

#### 1.3 Thesis Organization

The remainder of the thesis is organized as follows: Chapter 2 provides a review of adaptive filter theory, ending with the introduction of the DNLMS algorithm. Chapter 3 is associated with the first objective of this work: reduction of the amount of computations required by the DNLMS algorithm through application of computationallyefficient techniques. Analysis and simulation results are provided for the modified DNLMS algorithm. Chapter 4 is associated with the second objective of this work: providing details of an FPGA implementation of a pipelined DNLMS adaptive filter. The applied design methodology begins with architecture derivation and ends with hardware verification. Finally, conclusions and future work are described in Chapter 5.

## Chapter 2

# **Review of Adaptive Filtering**

#### 2.1 Fundamentals of Adaptive Filtering

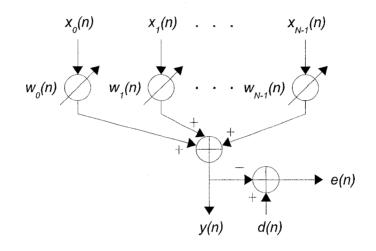

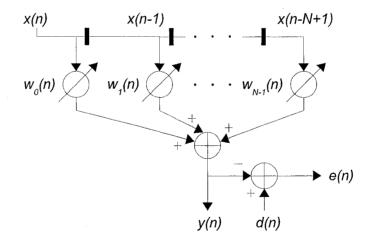

The adaptive linear combiner (ALC), shown in Fig. 2.1(a), is the fundamental building block in most adaptive systems [33]. The output, y(n), is a linear combination of several inputs at time index n and is given by

$$y(n) = \mathbf{x}^{T}(n)\mathbf{w}(n) = \mathbf{w}^{T}(n)\mathbf{x}(n)$$

(2.1)

where  $\mathbf{x}(n) = [x_0(n) \ x_1(n) \ \dots \ x_{N-1}(n)]^T$  is the input signal vector comprised of sampled data from N different sources and  $\mathbf{w}(n) = [w_0(n) \ w_1(n) \ \dots \ w_{N-1}(n)]^T$  is the weight vector (also referred to as the coefficient vector). The output is compared to the desired response input, d(n), to produce the error signal, e(n). The error is given by

$$e(n) = d(n) - y(n).$$

(2.2)

When  $\mathbf{x}(n)$  consists of the N sequential samples of the same signal, i.e.  $\mathbf{x}(n) = [x(n) \ x(n-1) \ \dots \ x(n-N+1)]^T$ , the ALC becomes the adaptive finite-duration

$\mathbf{6}$

(a) General form.

(b) As an FIR filter.

Figure 2.1: Adaptive linear combiner.

impulse response (FIR) filter shown in Fig. 2.1(b). In adaptive filtering,  $\mathbf{x}(n)$  is typically referred to as the regressor.

In order for the output to progressively approximate the desired response, the weights are adjusted in a manner that minimizes a cost function. The mean-square error (MSE) is a commonly used cost function given by

MSE

$$\triangleq \zeta$$

$$= E[e^{2}(n)]$$

$$= E[(d(n) - y(n))^{2}]$$

$$= E[(d(n) - \mathbf{w}^{T}(n)\mathbf{x}(n))^{2}]$$

$$= E[d^{2}(n)] - 2E[d(n)\mathbf{w}^{T}(n)\mathbf{x}(n)] + E[\mathbf{w}^{T}(n)\mathbf{x}(n)\mathbf{x}^{T}(n)\mathbf{w}(n)].$$

(2.3)

Assuming that the weights are fixed, the MSE cost function is given by

$$\zeta = E[d^2(n)] - 2\mathbf{w}^T E[d(n)\mathbf{x}(n)] + \mathbf{w}^T E[\mathbf{x}(n)\mathbf{x}^T(n)]\mathbf{w}.$$

(2.4)

Let  $\mathbf{R}$  be defined as the input correlation matrix given by

$$\mathbf{R} = E[\mathbf{x}(n)\mathbf{x}^{T}(n)]$$

$$= E\begin{bmatrix} x_{0}^{2}(n) & x_{0}(n)x_{1}(n) & \dots & x_{0}(n)x_{N-1}(n) \\ x_{1}(n)x_{0}(n) & x_{1}^{2}(n) & \dots & x_{1}(n)x_{N-1}(n) \\ \vdots & \vdots & \ddots & \vdots \\ x_{N-1}(n)x_{0}(n) & x_{N-1}(n)x_{1}(n) & \dots & x_{N-1}^{2}(n) \end{bmatrix}$$

(2.5)

and let **p** be defined as the cross correlation vector given by

$$\mathbf{p} = E[d(n)\mathbf{x}(n)] = E[d(n)x_0(n) \ d(n)x_1(n) \ \dots \ d(n)x_{N-1}(n)]^T.$$

(2.6)

By substituting  $\mathbf{R}$  and  $\mathbf{p}$  into (2.4), the MSE cost function can be simplified to

$$\zeta = E[d^2(n)] - 2\mathbf{w}^T \mathbf{p} + \mathbf{w}^T \mathbf{R} \mathbf{w}.$$

(2.7)

8

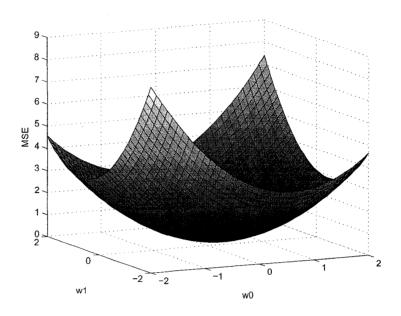

Figure 2.2: Mean-square error surface.

It can be seen from (2.7) that the MSE cost function is a quadratic function of the weights forming a hyperparaboloid surface. Figure 2.2 illustrates the MSE surface as a paraboloid for the case of the weight vector consisting of two weights. The bowl-shaped surface is concave upwards and has only positive values. The bottom of the surface represents the minimum mean-square error,  $\zeta_{min}$ , which projects to optimal weight vector,  $\mathbf{w}^*$ . The values of  $\zeta_{min}$  and  $\mathbf{w}^*$  can be found through the gradient of the MSE cost function.

The gradient of the MSE cost function with respect to the weight vector is given by

$$\nabla \triangleq \frac{\partial \zeta}{\partial \mathbf{w}} = \begin{bmatrix} \frac{\partial \zeta}{\partial w_0} & \frac{\partial \zeta}{\partial w_1} & \dots & \frac{\partial \zeta}{\partial w_{N-1}} \end{bmatrix}^T$$

$$= -2\mathbf{p} + 2\mathbf{R}\mathbf{w}.$$

(2.8)

9

Equating (2.8) to zero allows for the optimal weight vector to be solved as

$$\mathbf{w}^* = \mathbf{R}^{-1}\mathbf{p}.\tag{2.9}$$

Substitution of  $\mathbf{w}^*$  into (2.7) allows for the minimum mean-square error to be solved as

$$\zeta_{min} = E[d^2(n)] - 2\mathbf{w}^{*T}\mathbf{p} + \mathbf{w}^{*T}\mathbf{R}\mathbf{w}^*$$

$$= E[d^2(n)] - \mathbf{w}^{*T}\mathbf{p}. \qquad (2.10)$$

The solution for the optimal weight vector is known as the Wiener solution.

### 2.2 The Method of Steepest-Descent

As discussed in the previous section, the weights of the adaptive filter are adjusted to minimize the MSE cost function. The method of steepest-descent is a well-known weight adaptation procedure that seeks the minimum of the MSE surface. It serves as the basis for several adaptive filtering algorithms [10]. The method iteratively adds to the each weight a term proportional to the instantaneous gradient in order to descend the MSE surface. As a result, the weight vector progressively converges to the Wiener solution or a near-optimal solution.

The weight update equation of the method of steepest-descent is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) - \mu \nabla(n). \tag{2.11}$$

where  $\mu$  is the adaptation step-size that controls the stability and convergence rate. The gradient vector measured at  $\mathbf{w} = \mathbf{w}(n)$  is denoted as  $\nabla(n)$ .

Generally, when the step-size is chosen small, the MSE slowly converges to a steady-state value that will be close to the minimum value. On the other hand, when the step-size is chosen large, the MSE quickly converges to a steady-state value that will be larger than the minimum value. However, having a step-size that is too large will result in the weights diverging from the Wiener solution.

The calculation of the gradient vector requires statistical knowledge of the input and desired signals. In practice, these quantities are usually unknown. To get around this problem, there are methods to estimate the input correlation matrix  $\mathbf{R}$  and correlation vector  $\mathbf{p}$  [33]. However, several steepest-descent-based algorithms alternatively use an estimate of the gradient.

### 2.3 Least-Mean-Square Algorithm

The least-mean-square (LMS) algorithm is the most commonly used weight adaptation procedure in adaptive filtering [10, 33]. It is a steepest-descent-based algorithm that estimates the gradient of the MSE, shown in (2.8), with the gradient of the squared error given by

$$\hat{\nabla}(n) = \frac{\partial e^2(n)}{\partial \mathbf{w}(n)}$$

$$= 2e(n) \left[ \frac{\partial e(n)}{\partial w_0(n)} \frac{\partial e(n)}{\partial w_1(n)} \cdots \frac{\partial e(n)}{\partial w_{N-1}(n)} \right]^T$$

$$= -2e(n)\mathbf{x}.$$

(2.12)

Substituting this estimate for the true gradient in (2.11) yields the weight update equation for the LMS algorithm, given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) - \mu \hat{\nabla}(n)$$

$$= \mathbf{w}(n) - 2\mu e(n) \mathbf{x}.$$

(2.13)

As seen in (2.13), the weight update equation of the LMS algorithm is very simple and straightforward; it does not require calculations of the input correlation matrix nor the correlation vector. Another advantage of the LMS algorithm is that it has

11

guaranteed stable convergence when the step-size is chosen within the range

$$0 < \mu < \frac{1}{\lambda_{max}} \tag{2.14}$$

where  $\lambda_{max}$  is the largest eigenvalue of **R**. Since  $\lambda_{max}$  cannot exceed the trace of **R**, the selectable range of the step-size can also be expressed as

$$0 < \mu < \frac{1}{\operatorname{tr}[\mathbf{R}]}.\tag{2.15}$$

### 2.4 Normalized Least-Mean-Square Algorithm

Several algorithms have been derived from the standard LMS algorithm. One notable variant commonly used in echo cancellation is the normalized least-mean-square (NLMS) algorithm [12, 14]. Its weight update equation is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + \mu(n)e(n)\mathbf{x}(n). \tag{2.16}$$

The step-size,  $\mu(n)$ , is time-varying and is given by

$$\mu(n) = \frac{\alpha}{\|\mathbf{x}(n)\|^2 + \beta} \tag{2.17}$$

where  $\alpha$  is the convergence parameter,  $\beta$  is a small constant preventing division by zero, and  $\|\cdot\|$  is the  $l_2$  norm operation. The quantity  $\|\mathbf{x}(n)\|^2$  will be referred to as the regressor energy. By normalizing the convergence parameter by the regressor energy, large values of  $\mathbf{x}(n)$  have a minimal affect on the adaptation. In other words, unlike the LMS algorithm, the NLMS algorithm does not suffer from the gradient noise amplification problem [15].

The NLMS algorithm has guaranteed stable convergence when the convergence parameter is chosen within the range

$$0 < \alpha < 2. \tag{2.18}$$

12

This range is independent of the input signal statistics, thus making selection of  $\alpha$  much easier than selection of  $\mu$  for the LMS algorithm. The other advantage of the NLMS algorithm is that it can potentially converge faster than the LMS algorithm [12].

### 2.5 Delayed Weight Adaptation

The feedback error of the LMS algorithm limits the speed of adaptation and prohibits pipelining. Pipelining is a technique of breaking up the effective critical path by inserting delays, thereby facilitating either low-power or high-speed architectures [22]. To allow pipelining, (2.13) can be modified by inserting delays of D samples, resulting in the weight update equation for the delayed least-mean-square (DLMS) algorithm given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + \mu e(n-D)\mathbf{x}(n-D).$$

(2.19)

Since the convergence speed of the DLMS algorithm worsens as D increases, D should be kept as small as possible [18].

Likewise, delaying the weight adaptation can be extended to the NLMS algorithm [3]. The weight update equation of the delayed normalized least-mean-square (DNLMS) algorithm is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + \mu(n-D)e(n-D)\mathbf{x}(n-D).$$

(2.20)

## Chapter 3

# Computationally-efficient DNLMS-based Algorithms

In this chapter, computationally-efficient techniques are applied to the DNLMS algorithm in order to reduce power and/or area consumption. NEC and AEC simulations are provided to show that applying these techniques introduce marginal performance degradation. Please note that the material presented in this chapter has been published in [17].

### 3.1 Computationally-efficient techniques

As seen in (2.1), calculation of the ALC output requires N multiplications and N-1additions per iteration. Furthermore, (2.20) indicates that the DNLMS weight update requires N+1 multiplications and N additions per iteration. Therefore, the number of required multiplications and additions per iteration is proportional to the adaptive filter order. As mentioned in Chapter 1, high-order adaptive filters are typically applied in echo cancellation. The related high demand for large amounts of computations per iteration translates to high power consumption for the hardware implementation. There are several modifications that can be made to an adaptive filtering algorithm to reduce power and/or area consumption. Two general ways considered here are (1) simplifying computationally-intensive operations of the algorithms and (2) reducing the switching activity in the device.

The large number of multipliers is the main reason for the high power consumption. Adders are not as large of a concern because they are considerably simpler than multipliers. For example, a 4-bit ripple carry adder requires 20 logic gates while a 4-bit by 4-bit binary multiplier requires 16 logic gates plus 3 4-bit adders [20]. Simplifying the multiplications to less complicated operations, such as additions or shifts, would reduce power and area consumption. This can be achieved by using power-of-two (POT) quantization [10, 34].

Dynamic power consumption of complementary metal-oxide semiconductor (CMOS) circuits is due to the charging and discharging of the capacitive loads occurring each time a transistor's binary representation switches, i.e.  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transition [32]. Thus, the higher the amount of switching activity, the higher the dynamic power consumption. Reducing the switching activity would therefore reduce dynamic power consumption. The M-Max algorithm [2] and the stop-and-go algorithm (SAG) [1, 24] both reduce the switching activity by scheduling less weight updates.

The aforementioned computationally-efficient techniques have been applied to the LMS and NLMS algorithms. The remainder of this section shows the application of these techniques to the DNLMS algorithm. Additionally, a new stopping criterion for the SAG algorithm is introduced.

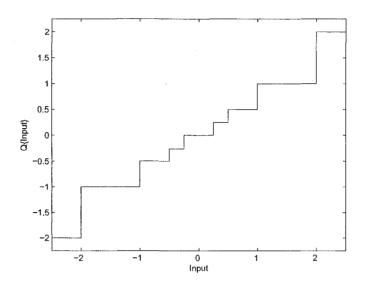

Figure 3.1: Transfer characteristic of POT quantizer for a = 2, b = 2, and  $\tau = 0$ .

#### 3.1.1 Power-of-two Quantization

POT error quantization has been applied to the LMS algorithm in order to simplify N multiplications required for the weight update to shift operations, thereby reducing the computational load [10, 34]. The quantization is a nonlinear operation that results in the error data being represented as a binary word with a single "1" bit. This idea can be extended to the regressor energy, thereby allowing the division operation in (2.17) to be implemented as a shift operation as well. The POT quantization is given as

$$Q\{\cdot\} = \begin{cases} sgn\{\cdot\}2^{a-1}, & |\cdot| \ge 2^{a-1} \\ sgn\{\cdot\}2^{\lfloor log_2(|\cdot|) \rfloor}, & 2^{-b} \le |\cdot| < 2^{a-1} \\ sgn\{\cdot\}\tau, & |\cdot| < 2^{-b} \end{cases}$$

(3.1)

where  $a \ge 0$  is the number of integer bits excluding the sign bit,  $b \ge 0$  is the number of fractional bits, and  $\tau$  is set to either 0 or  $2^{-b}$ . Figure 3.1 illustrates the transfer characteristic of the POT quantizer for a = 2, b = 2, and  $\tau = 0$ .

By applying POT quantization to the error and regressor energy, DNLMS is

modified to the Quantized-Error-Regressor-energy DNLMS (QER-DNLMS) algorithm, for which the weight update equation is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + \mu(n-D)Q\{e(n-D)\}\mathbf{x}(n-D)$$

(3.2)

where

$$\mu(n-D) = \frac{\alpha}{Q\{\|\mathbf{x}(n-D)\|^2 + \beta\}}.$$

(3.3)

Note that if  $\alpha$  is chosen to be a POT number, then QER-DNLMS weight update equation will consist of N + 1 shifts plus 2 POT quantizations in place of N multiplications and 1 division per iteration.

#### 3.1.2 M-Max Algorithm

Partial update algorithms update only a portion of the filter weights, effectively reducing the demand of memory resources and computation power when implementing adaptive filtering algorithms on digital signal processors (DSPs) [11]. Since the computational cost of adaptive filtering algorithms is proportional to the filter order, partial update algorithms are most effective in high-order filter applications such as echo cancellation. Partial update algorithms are considered for hardware implementation because updating only a portion of the weights would decrease the switching activity in the device, thereby reducing the dynamic power consumption.

A straightforward selective-partial weight update algorithm is the M-Max algorithm [2]. The M-Max algorithm, which was originally applied to the NLMS algorithm, only updates the weights corresponding to the M largest absolute values of the regressor, where M < N. The M-Max-NLMS algorithm saves N - M weight updates per iteration while maintaining close performance to NLMS. Extending this algorithm to DNLMS yields the M-Max-DNLMS algorithm, for which the weight update equation is given by

$$w_{i}(n+1) = \begin{cases} w_{i}(n) + \mu(n-D)e(n-D)x(n-i-D), & \text{if } i \text{ corresponds to one} \\ & \text{of the first } M \text{ maxima} \\ & \text{of } |x(n-i-D)| \\ & w_{i}(n), & \text{otherwise} \end{cases}$$

(3.4)

where i = 0, ..., N - 1. Compared to the DNLMS algorithm, the M-Max-DNLMS algorithm has N - M less multiplications and additions per iteration. The overhead cost of this M-Max algorithm includes implementing a sorting algorithm. If the SORTLINE sorting algorithm [25] is used, the amount of additional comparisons per iteration would be at most  $\lfloor 2log_2N \rfloor + 2$ .

#### 3.1.3 Stop-and-go Algorithm

A SAG technique was first introduced in [24] to improve the convergence capabilities of decision-aided blind joint equalization and carrier recovery. The idea behind this algorithm is to "stop" adaptation or let it "go" based on the error at the particular sampling time under consideration. In [1], the SAG concept was applied to the NLMS algorithm in order to reduce the amount of computations. In this SAG algorithm, when the magnitude of the error is below a pre-defined threshold, weight adaptation is stopped for that iteration. The weight update equation for the SAG-NLMS algorithm is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + f(n)\mu(n)e(n)\mathbf{x}(n)$$

(3.5)

where

$$f(n) = \begin{cases} 1, & |e(n)| > \kappa \\ 0, & |e(n)| \le \kappa \end{cases}$$

(3.6)

In (3.6),  $\kappa$  is a positive real number and f(n) is the flag indicating whether or not to update the coefficients. In [1],  $\kappa$  was determined by observing the statistics of |e(n)|

over a large number of iterations. Here, the SAG-threshold is related to the regressor energy.

Consider the weight update correction term of the NLMS algorithm given by

$$\Delta \mathbf{w}(n) = \mathbf{w}(n+1) - \mathbf{w}(n)$$

$$= \frac{\alpha}{\|\mathbf{x}(n)\|^2} e(n) \mathbf{x}(n)$$

(3.7)

where, for simplicity, the  $\beta$  term has been omitted. The weight update should be stopped when the |e(n)| is small so that  $|\Delta \mathbf{w}(n)|$  is significantly small and  $\mathbf{w}(n+1) \approx$  $\mathbf{w}(n)$ . To ensure that this condition is true for all values in the vector  $\Delta \mathbf{w}(n)$ , let the stopping criterion be defined in terms of the largest absolute value of  $\Delta \mathbf{w}(n)$ , which is associated with the largest absolute value of  $\mathbf{x}(n)$ . The new SAG-stopping criterion is defined as max{ $|\Delta \mathbf{w}(n)|$ }  $\leq \kappa$ , where again  $\kappa$  is a positive real number. Substituting (3.7) into this condition gives

$$|e(n)| \le \frac{\kappa}{\alpha \max\{|\mathbf{x}(n)|\}} \|\mathbf{x}(n)\|^2.$$

(3.8)

To avoid division, (3.8) can be rewritten as

$$\frac{\alpha}{\kappa} \max\{|\mathbf{x}(n)|\} |e(n)| \le \|\mathbf{x}(n)\|^2$$

(3.9)

where the ratio  $\frac{\alpha}{\kappa}$  can be implemented as a single constant. Now, applying the SAG algorithm to DNLMS with the new stopping criterion gives SAG-DNLMS, for which the weight update equation is given by

$$\mathbf{w}(n+1) = \mathbf{w}(n) + f(n-D)\mu(n-D)e(n-D)\mathbf{x}(n-D)$$

(3.10)

where

$$f(n-D) = \begin{cases} 1, & \|\mathbf{x}(n-D)\|^2 < & \frac{\alpha}{\kappa} \max\{\|\mathbf{x}(n-D)\|\} | e(n-D) | \\ 0, & \|\mathbf{x}(n-D)\|^2 \ge & \frac{\alpha}{\kappa} \max\{\|\mathbf{x}(n-D)\|\} | e(n-D) | \end{cases}$$

(3.11)

Assuming that  $\alpha$  and  $\kappa$  are chosen such that the ratio  $\frac{\alpha}{\kappa}$  is a POT number, then when the weight adaptation is stopped, there is a savings of N multiplications, N additions, and 1 shift for the weight update as well as 1 division for the step-size calculation for that iteration. One overhead cost of the SAG algorithm is the calculations of f(n-D), which requires one comparison and two multiplications per iteration. However, if the constants  $\alpha$  and  $\kappa$  are power-of-two numbers, then one of the multiplications can be replaced with a shift operation. Another overhead cost is the implementation of a max selection algorithm. A fast algorithm for maximum/minimum calculation across a sliding data window has been proposed in [13] and was labeled the MAXLIST algorithm. This algorithm requires three comparisons and  $O(\log N)$  memory locations on average for independent and identically distributed (i.i.d.) input signals. However, if the SAG algorithm is to be used with the M-Max algorithm, then the sorting algorithm can also serve to find the maximum values of the regressor.

#### 3.1.4 Proposed Algorithm

The proposed algorithm is the DNLMS modified with all the techniques previously mentioned in this section. Its coefficient update equation is given by

$$w_{i}(n+1) = \begin{cases} w_{i}(n) + f(n-D)\mu(n-D)Q\{e(n-D)\}x(n-i-D), & \text{if } i \text{ corresponds} \\ & \text{to one of the first} \\ & M \text{ maxima of} \\ & |x(n-i-D)| \\ \\ & w_{i}(n), & \text{otherwise} \end{cases}$$

$$(3.12)$$

where f(n-D) is given by

$$f(n-D) = \begin{cases} 1, & \|\mathbf{x}(n-D)\|^2 < \frac{\alpha}{\kappa} \max\{\|\mathbf{x}(n-D)\|\} \|Q\{e(n-D)\}\| \\ 0, & \|\mathbf{x}(n-D)\|^2 \ge \frac{\alpha}{\kappa} \max\{\|\mathbf{x}(n-D)\|\} \|Q\{e(n-D)\}\| \end{cases}$$

(3.13)

and  $\mu(n-D)$  is that in equation (3.3).

Assuming that  $\alpha$  and  $\kappa$  are POT numbers, the combined techniques have the effect of: (1) simplifying N multiplications and 1 division to N + 1 shifts and 2 POT quantizations; (2) saving N - M shifts and additions per "GO" iteration; and (3) saving M + 2 shifts and M additions per "STOP" iteration.

Table 3.1 summarizes the total number of multiplications, divisions, additions, shifts, and comparisons that execute over m input samples for adaptive filtering when the DNLMS algorithm and its variants previously introduced are used. The amount of computations was derived under the following assumptions:  $\alpha$  is a POT number for all algorithms, resulting in at least one shift operation in the coefficient update calculation; the ratio  $\frac{\alpha}{\kappa}$  is implemented as a single constant equal to a POT number; the regressor energy is calculated recursively as  $\|\mathbf{x}(n)\|^2 = \|\mathbf{x}(n-1)\|^2 + x^2(n) - x^2(n-N)$ , requiring 2 multiplications and 2 additions per iteration; and the SAG algorithms have only g out of m samples in the "GO" mode. It can be seen that an adaptive filter using the proposed algorithm has N less multiplications and 1 less division per iteration compared to the DNLMS algorithm at the cost of additional shifts and comparisons. The number of reduced additions is dependent on the choice of M and how often the proposed algorithm is in "STOP" mode.

#### 3.2 Simulation Results

In this section, two simulation examples are presented to compare the performance of all algorithms discussed previous section. See Appendix A for the Matlab source code.

| 1 | ಲು                       |

|---|--------------------------|

|   | COMPUTATIONALLY-EFFICIEN |

|   | VT DNLMS-BASED           |

|   | ALGORITHMS               |

Table 3.1: Number of Operations Executed over m input samples

| Algorithm          | Multiplications | Divisions | Additions   | Shifts      | Comparisons                   |

|--------------------|-----------------|-----------|-------------|-------------|-------------------------------|

| DNLMS              | m(2N+2)         | m         | m(2N+3)     | m           | 0                             |

| QER-DNLMS          | DNLMS $m(N+2)$  |           | m(2N+3)     | m(N+2)      | 0                             |

| M-Max-DNLMS        | m(M + N + 2)    | m         | m(M+N+3)    | m           | $m(2\lfloor log_2N\rfloor+2)$ |

| SAG-DNLMS          | gN+m(N+3)       | g         | gN + m(N+3) | g+m         | 4m                            |

| Proposed algorithm | m(N+2)          | 0         | gM + m(N+3) | g(M+2) + 2m | $m(2\lfloor log_2N\rfloor+3)$ |

#### 3.2.1 Network Echo Cancellation with White Gaussian Input

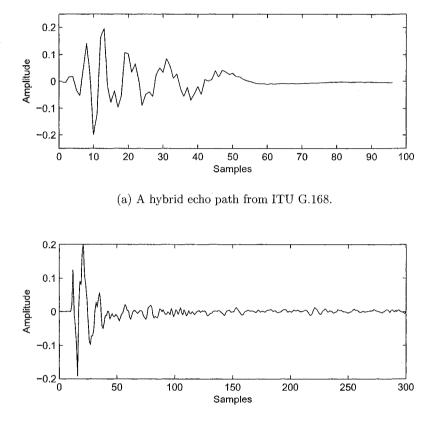

In this set of simulations, the performance of each algorithm mentioned in the previous sections is investigated under varying parameters for NEC. Simulations are carried out using an echo path impulse response model from the International Telecommunication Union (ITU) G.168 Recommendation [16], shown in Fig. 3.2(a). The input is white Gaussian noise (WGN) with signal-to-noise ratio (SNR) of 30 dB. The echo return loss (ERL), which is the ratio of the input signal power to the echo signal power, is 6 dB. The filter length is chosen to equal the channel length, i.e. N = 96. All simulations have parameters  $\alpha = 0.5$ ,  $\beta = 0.008$ , and D = 32. The MSE is calculated as the average instantaneous squared error over 200 trials.

The first simulation results show how DNLMS is affected by POT quantization. Quantized-Error DNLMS (QE-DNLMS) has POT quantization of the delayed error e(n-D) to an 8-bit word (a = 1, b = 6). Quantized-Regressor-energy DNLMS (QR-DNLMS) has POT quantization of the delayed regressor energy  $||x(n-D)||^2$  to an 8-bit word (a = 7, b = 0). As mentioned in the previous section, QER-DNLMS has POT quantization of both the delayed error and regressor energy to the same wordlengths used for QE-DNLMS and QR-DNLMS respectively. For QE-DNLMS,  $\tau = 0$  and for QR-DNLMS,  $\tau = 2^{-b}$  because both achieved better performances for those choices of  $\tau$ . Figure 3.3 shows that, compared to DNLMS, QE-DNLMS converges slower and achieves a lower steady-state MSE, QR-DNLMS converges slower and achieves a higher steady-state MSE, and QER-DNLMS achieves similar performance.

The next simulation shows the affects of using different values of M for M-Max-DNLMS. Note that for M = N the M-Max-DNLMS is reduced to DNLMS. Figure 3.4 shows that as M decreases, the MSE convergence time decreases.

Next, simulations to investigate how varying  $\kappa$  affects the MSE learning curve of SAG-DNLMS are carried out. Note that  $\kappa = 0$  represents DNLMS. It is shown in Fig. 3.5 that as  $\kappa$  increases, convergence time increases. Table 3.2 shows how

(b) An acoustic echo path of the inside of a car.

Figure 3.2: Echo path impulse responses.

Figure 3.3: MSE curves of DNLMS under different quantization algorithms.

often, on average over 200 trials, the SAG-DNLMS coefficients were updated before and after convergence. This table also includes results for the proposed algorithm, which will be discussed later. For SAG-DNLMS, it can be seen that as  $\kappa$  increases, the percentage of samples in the "GO" mode decreases drastically, especially after convergence.

Finally, the performance of the proposed algorithm is compared to that of the

| Algorithm | 10        | Percent Samples in "GO" mode |                   |  |  |  |  |  |  |  |  |

|-----------|-----------|------------------------------|-------------------|--|--|--|--|--|--|--|--|

| Algorithm | κ         | Before Convergence           | After Convergence |  |  |  |  |  |  |  |  |

| SAG-DNLMS | 0.0005    | 63.24                        | 35.32             |  |  |  |  |  |  |  |  |

| SAG-DNLMS | 0.0010    | 31.64                        | 6.75              |  |  |  |  |  |  |  |  |

| SAG-DNLMS | 0.0015    | 21.16                        | 1.41              |  |  |  |  |  |  |  |  |

| Proposed  | $2^{-11}$ | 44.97                        | 14.13             |  |  |  |  |  |  |  |  |

Table 3.2: Impact of SAG algorithm under WGN input

Figure 3.4: MSE curves of M-Max-DNLMS for different M's.

Figure 3.5: MSE curves of SAG-DNLMS for different  $\kappa$ 's.

Figure 3.6: MSE curves of NLMS and Proposed algorithm.

standard NLMS algorithm. The parameter chosen include D = 32, M = 32,  $\kappa = 2^{-11}$ , quantization of e(n-D) to an 8-bit word  $(a = 1, b = 6, \tau = 0)$ , and quantization of  $||x(n-D)||^2$  to an 8-bit word  $(a = 7, b = 0, \tau = 2^{-b})$ . From Fig. 3.6, it can be seen that the proposed algorithm has moderate performance degradation when compared to NLMS. From Table 3.2, it can be seen that the proposed algorithm experiences significant reductions in computations due to its SAG-related portion alone.

### 3.2.2 Network and Acoustic Echo Cancellation with Composite Source Signal Input

In this simulation example, NLMS and the proposed algorithm are simulated for both NEC and AEC applications. The input used in this simulation is the composite source signal (CSS) from ITU G.168. The CSS has been downsampled to 8 kHz. It is approximately 350 ms long and consists of a 48.62 ms duration voice signal, a 200 ms duration pseudo-noise signal, and a 101.38 ms duration pause. This sequence is

|     | Percent Samples in "GO" mode |              |       |  |  |  |  |  |  |  |  |

|-----|------------------------------|--------------|-------|--|--|--|--|--|--|--|--|

|     | Voice                        | Pseudo Noise | Pause |  |  |  |  |  |  |  |  |

| NEC | 32.13                        | 42.23        | 2.42  |  |  |  |  |  |  |  |  |

| AEC | 34.33                        | 50.54        | 6.28  |  |  |  |  |  |  |  |  |

Table 3.3: Impact of SAG on Proposed algorithm under CSS input

repeated as many times as needed, with an inversion at each repetition, to create a longer signal.

For NEC, the echo path shown in Fig. 3.2(a) is once again used. For AEC, the echo path impulse response model of the inside of a car, shown in Fig. 3.2(b), is used. The SNR is 30 dB. The filter lengths are given as N = 96 for NEC and N = 300 for AEC. Algorithmic parameters for NLMS and the proposed algorithm in both NEC and AEC simulations include  $\alpha = 0.125$  and  $\beta = 0.008$ . Additionally, the proposed algorithm has the following parameters: M = 32 for NEC and M = 128 for AEC;  $\kappa = 2^{-13}$  for NEC and  $\kappa = 2^{-14}$  for AEC; and all remaining parameters are the same as the ones used in the first simulation example.

For this simulation example, echo return loss enhancement (ERLE), a typical measure of echo canceller performance, is calculated and plotted. ERLE is defined as

$$ERLE = 10 \log_{10} \frac{E[d^2(n)]}{E[(d(n) - y(n))^2]} dB.$$

(3.14)

and can be described as the ratio of the power of the echo versus the power of the residual echo.

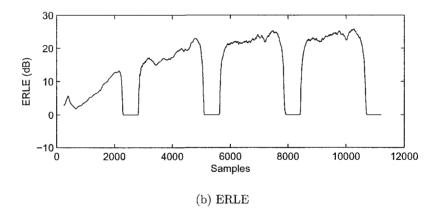

Figure 3.7 shows the residual echo and corresponding ERLE of NLMS and the proposed algorithm for NEC simulation. The echo is included with the residual echoes and labelled as the case when there is no echo cancellation. The results show that the echo is effectively cancelled after the first CSS sequence for both algorithms. Also, the proposed algorithm achieves similar ERLE performance to NLMS.

Figure 3.7: Residual echo and ERLE of NLMS and proposed algorithm for NEC simulation.

COMPUTATIONALLY-EFFICIENT DNLMS-BASED ALGORITHMS

లు

Figure 3.8: Residual echo and ERLE of NLMS and proposed algorithm for AEC simulation.

లు

For AEC simulation, Fig. 3.8 shows that the echo is effectively cancelled after the third CSS sequence. Although the proposed algorithm initially has a lower ERLE performance than NLMS, it achieves similar ERLE performance to NLMS.

Finally, Table 3.3 shows, for the proposed algorithm under NEC and AEC simulations, how often the samples were in the "GO" mode over the voice, pseudo noise, and pause portions of the input. It can be seen that the proposed algorithm provides a significant amount of computational savings, especially during periods of pause.

# Chapter 4

# FPGA Implementation of Pipelined DNLMS Adaptive Filter

As mentioned in Chapter 2, the DNLMS algorithm is suitable for implementing pipelined adaptive filter architectures. However, to this date there has been little work presenting architectures for DNLMS adaptive filters [23, 26, 28], none having given a detailed implementation. This chapter presents the FPGA implementation of a pipelined, regular, modular, low-latency, portable DNLMS adaptive filter.

This chapter is organized as follows: Section 4.1 shows the derivation of the architecture for the DNLMS adaptive filter. The design is then tested for echo cancellation application. Section 4.2 discusses the design methodology which includes fixed-point and register transfer level (RTL) simulations, physical synthesis for the Altera Stratix EPS140F780C5 FPGA [6], and functional verification results obtained from hardware implementation using the Nios Development Board, Stratix Professional Edition [4].

#### 4.1 Architecture Derivation

A pipelined architecture can be derived using the cutset retiming technique [22]. A cutset is a set of edges in a graph that, when removed, partition the graph into two separate sub-graphs. Cutset retiming is performed by removing k delays from each edge moving in a given direction, from one sub-graph to the other, while adding k delays to the remaining edges moving in the opposite direction, where k is an arbitrary positive integer [22]. This technique does not change the input/output characteristic of the graph. In [7], cutset retiming is used to produce a hybrid FIR form filter architecture, a cross between the direct and transposed FIR forms, for the DLMS adaptive filter. In this section, a pipelined architecture is similarly derived for a more efficient implementation. Cutset retiming has been used to derive a pipelined architecture for the DNLMS adaptive filter in [26, 28], however that design was ultimately a folded architecture. Although folded architectures consume less resources, they require operation at higher frequencies than unfolded architectures.

Figure 4.1 shows the direct form DNLMS adaptive FIR filter architecture. Note that D delays are applied to the input x(n) in two places. The delays are applied in this manner to provide a sufficient amount of delays for the retiming technique.

The critical path is defined as the path of the graph not containing a delay element that has the longest computation time. The critical path of the direct form structure is highlighted in Fig. 4.1 and labelled "1<sup>st</sup> crit. path". Thus, the critical time is  $(N+1)t_a + t_m$ , where  $t_a$  and  $t_m$  are the amounts of time required to complete single addition and multiplication operations respectively. Recall from Chapter 1 that echo cancellation requires the use of high-order adaptive filters. In other words, N is large and consequently, so is the critical time of this architecture. Using cutset retiming, delays can be inserted to break up the critical path, thereby decreasing the critical time while preserving the functionality and zero-latency characteristic of the direct form FIR DNLMS adaptive filter architecture.

Cutsets, shown by dashed lines in Fig. 4.1, are applied to the filter such that P weights are grouped together. It is assumed that N is a multiple of P. It will be seen that applying the cutsets in this regular manner results in a regular structure. An additional cutset is applied to the step-size calculation component, seen in the lower-right corner of Fig. 4.1. By doing this, a delay will be inserted in the potential critical path labelled "2<sup>nd</sup> crit. path", which has a computation time of  $3t_a + 3t_m + t_d$ , where  $t_d$  is the amount of time required to complete a single division operation.

Applying cutset retiming results in the hybrid form DNLMS adaptive FIR filter architecture shown in Fig. 4.2. Identical processing elements (PEs), each containing Pweights, are outlined. Two potential critical paths are highlighted. Thus, the critical time for this pipelined architecture is the larger amount between  $(P + 1)t_a + t_m$ and  $t_a + t_m + t_d$ . This is true under the condition that D > N/P - 1. Therefore, the minimum value of D is N/P. Note that there is a redundancy of signal values between the regressor,  $\mathbf{x}(n)$ , and the delayed regressor,  $\mathbf{x}(n - D)$ . By having one single tap-delay line for the input, the number of delay elements can be reduced by N - 2N/P + D + 1.

Figure 4.3 shows the proposed efficient architecture of the hybrid form FIR DNLMS adaptive filter. The contents of  $i^{th}$  PE are illustrated in Fig. 4.4, where i = 0, 1, ..., (N/P - 1). The values  $y_0(n), y_1(n) \ldots, y_{N/P}(n)$  are defined as intermediate values of the output, where  $y_0(n) = y(n)$  and  $y_{N/P} = 0$ . Also, it is shown in Fig. 4.3 that the divider and the delay following it has been replaced with an look-up table (LUT), which is assumed to have an inherent delay of  $t_d$ . Since  $t_d$  is now equal to the amount of time required to read from memory, the critical time for this design is clearly  $(P+1)t_a + t_m$ .

Now the tradeoff introduced by varying the value of P can be discussed. As P decreases, the critical time decreases as well as the degree of data broadcasting of

Figure 4.4: The  $i^{th}$  PE of the efficient hybrid form FIR DNLMS adaptive filter architecture.

$\mu(n - D + i)e(n - D + i)$  seen in the *i*<sup>th</sup> PE. However, the minimum value of *D*, i.e. N/P, increases. Recall from Section 2.5 that *D* should be kept as small as possible since a larger value would worsen the convergence behaviour. Therefore, changes in *P* results in a tradeoff between architectural design characteristics and algorithmic performance.

Table 4.1 summarizes the different critical times and number of delay elements required for each discussed architecture.

| Architecture | Critical Time                             | No. of Delay Elements |

|--------------|-------------------------------------------|-----------------------|

| Direct Form  | $(N+1)t_a + t_m$                          | 3N + 3D               |

| Hybrid Form  | $\max\{(P+1)t_a + t_m, t_a + t_m + t_d\}$ | 3N - 2N/P + 3D + 1    |

| Proposed     | $(P+1)t_a + t_m$                          | 2N + 2D               |

Figure 4.5: Design methodology.

# 4.2 Design Methodology for FPGA Implementation

Figure 4.5 shows the design methodology used to implement the proposed architecture shown in Fig. 4.3. Each step is discussed in further details in the following subsections.

#### 4.2.1 Fixed-Point Simulations

Fixed-point simulations of the pipelined hybrid form FIR DNLMS adaptive filter for echo cancellation are carried out using the fixed-point toolbox in Matlab. See Appendix A for the Matlab fixed-point source code.

The echo path impulse response model illustrated in Fig. 3.2(a) is used to create the desired response signal. The two test input signals used are WGN and the CSS from ITU G.168. The CSS sequence is repeated four times, with an inversion at each repetition, to create a longer signal. The SNR is 30 dB.

The filter length is chosen to equal the channel length, i.e. N = 96. Other parameter values were set as P = 3 and  $\beta = 0.0625$ . Recall from Section 4.1 that the design constraint for the adaptation delay was given as D > N/P - 1. Since it should also be kept as small as possible, D is chosen to equal 32. The parameter  $\alpha$ is equal to 0.5 and 0.125 for WGN input and CSS input respectively. To measure the filter's performance, the instantaneous squared error is calculated for the case of WGN input and ERLE is calculated for the case of CSS input.

Two's complement number system was chosen for the implementation. Overflow is avoided by saturating the sum or product while rounding is handled with truncation. The wordlengths, shown in Table 4.2, were determined by observing the range of all signals in floating-point simulations and by performing fixed-point and RTL simulations to ensure adequate performance.

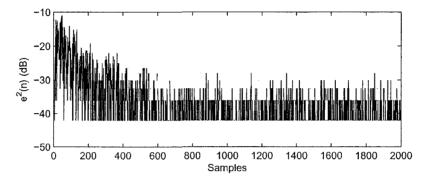

Figure 4.6(a) shows the instantaneous squared error plotted from fixed-point simulation of the DNLMS adaptive filter when WGN input was applied. It can be seen that the filter exhibits stable behaviour with the squared error having converged to its steady-state value within the first 600 samples. Figure 4.6(b) shows the ERLE performance of the filter when CSS input was applied. It is shown that the echo is effectively cancelled after the first CSS sequence. The results shown in Fig. 4.6 will be used as a benchmark for checking the equivalence of between the fixed-point

| Signal(s)                      | Wordlengths (Total, Fractional) |

|--------------------------------|---------------------------------|

| x(n), d(n), e(n), y(n)         | (8, 7)                          |

| $\mathbf{w}(\mathbf{n})$       | (18, 17)                        |

| $\mu(n)$                       | (11, 7)                         |

| $\ \mathbf{x}(\mathbf{n})\ ^2$ | (12, 7)                         |

Table 4.2: Signal Wordlengths

design model and the other design models that follow in this section.

#### 4.2.2 RTL Simulations

The design in Fig. 4.3 was modelled using Verilog Hardware Description Language (HDL). Each Verilog module was written behaviourally and is parametizable, and independent of vendor technology (see Appendix B for Verilog source code). Thus, the design description can be considered as an intellectual property (IP) core. It is flexible and portable, making it suitable for design re-use. These characteristics are important in digital design because it reduces the "time-to-market" for projects using similar architectures.

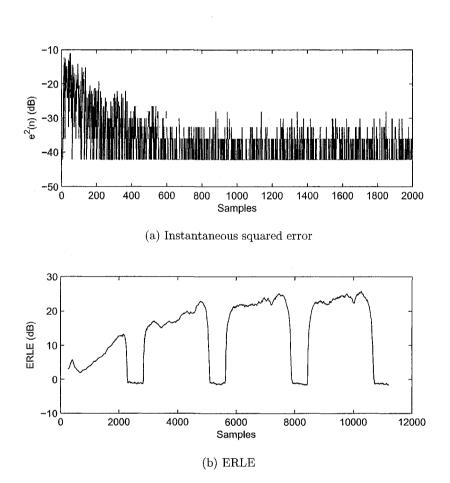

Cadence NC-Verilog Simulator was used to perform RTL simulations. All parameters and wordlengths have the same values mentioned in Section 4.2.1. Both WGN and CSS inputs are used. Figures 4.7(a) and 4.7(b) show the squared error and ERLE plots from the RTL simulation results, respectively. These plots are nearly identical to the fixed-point simulation plots in Fig. 4.6(a) and Fig. 4.6(b). The only difference is that the error and output from the RTL simulations are delayed by one clock period. This is due to buffering of the input. Thus, the implemented design will have a latency of one. Aside from that difference, the RTL simulations generate the same outputs as fixed-point simulations.

(a) Instantaneous squared error plot from fixed-point simulation for WGN input.

Figure 4.6: Results from fixed-point simulations.

Figure 4.7: Results from RTL simulations.

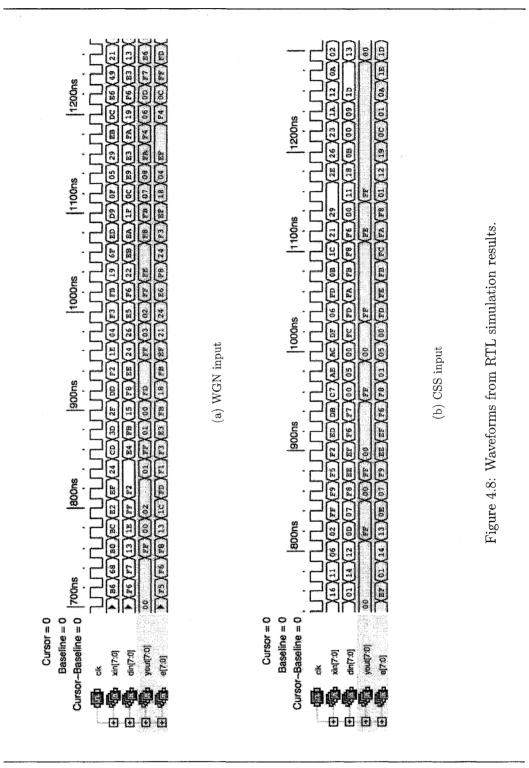

Figure 4.8 shows the captured signal waveforms of x(n), d(n), y(n), and e(n)(which are given alias names xin, din, yout, and e, respectively) from the RTL simulations. The chosen time frame is the moment when y(n) begins to have a non-zero output. These results will be used to compare the hardware implementation in Section 4.2.3 to the RTL simulation.

#### 4.2.3 Synthesis and Hardware Verification

The Verilog behavioural description of the design under test (DUT), i.e. the adaptive filter, was physically synthesized for the Altera Stratix EPS140F780C5 FPGA, then functionally verified using the Altera Nios Development Board, Stratix Professional Edition. The Altera Quartus II 5.0 design software is used to perform logic synthesis, technology mapping, fitting, timing analysis, hardware configuration, and functional verification [5].

To stimulate the DUT, a finite-state machine (FSM) was incorporated into the Quartus project. The FSM was used to reset the DUT, apply inputs, and write outputs to memory. Appendix B contains the Verilog source code for the FSM.

The top-level of the Quartus project is shown in Fig. 4.9. It can be seen that the FSM's I/Os are mapped to an on-board clock pin through a frequency divider module, two on-board push-button pins, and memory modules. The timing analysis performed by the Quartus II Timing Analyzer indicated that the maximum operating frequency of the DUT is 32.27 MHz. Thus, a frequency divider was necessary to reduce the 50 MHz clock supplied on the on-board oscillator. The push-buttons were used to manually reset the FSM to its idle state and to initiate the test. The ROM modules contained the input and desired response signal data as well as the LUT data necessary for the division operation. The RAM modules were used to store the error and output data. Using the In-System Memory Content Editor, the content of the ROM/RAM modules was viewed and manually changed during online operation.

| Resource                 | Used    | Available | Utilization (%) |

|--------------------------|---------|-----------|-----------------|

| Logic elements           | 38,037  | 41,250    | 92              |

| Pins                     | 3       | 616       | < 1             |

| Memory bits              | 407,936 | 3,423,744 | 11              |

| DSP block 9-bit elements | 112     | 112       | 100             |

Table 4.3: FPGA Resource Utilization

In this manner, the error and output data were exported to files.

Table 4.3 summarizes the resource utilization after fitting. It is shown that the implementation requires nearly all of the available logic elements (LEs). An LE is the Altera Stratix FPGA's smallest unit of logic [6]. The digital signal processing (DSP) blocks, which contain dedicated hardware suitable for DSP applications, were completely utilized. The implementation requires few I/O pins and memory resources. To further convey the resource utilization, Fig. 4.10 shows a high-level view of the FPGA after fitting. Unused resources are given light colours. The logic array blocks (LABs), each of which contain 10 LEs, have a colour gradient corresponding to their usage. The darker a LAB is coloured, the more LEs within it are utilized.

After completing physical synthesis and timing analysis, programming files are generated and used to configure the FPGA. After programming the FPGA, WGN and CSS input were applied to the DUT. During online operation, SignalTap II Analyzer was used to capture signal waveforms. Figure 4.11 shows the captured signal waveforms of x(n), d(n), y(n), and e(n) from the hardware tests. The trigger moment used for capturing the data is the instance when y(n) begins to have a nonzero output. It can be seen that the waveforms in this figure identically match the RTL simulation waveforms in Fig. 4.8.

Finally, the error data from the hardware implementation was acquired through the In-System Memory Content Editor and plotted in Fig. 4.12. These plots are

Figure 4.10: Post-fitting chip view illustrating resource utilization.

| Name                   | -2 -1        | <u>p</u>     | 1             | 2 3            | 4         | 5     | 6            | 7       | 8 9            | } 1     | 0            | 1 1          | 2 1     | 13 14          |

|------------------------|--------------|--------------|---------------|----------------|-----------|-------|--------------|---------|----------------|---------|--------------|--------------|---------|----------------|

| 🗄 hybrid_fsminstixin   | ( BEN ( ESh  | X BOh        | X BCh )       | <u>χ</u> εzh χ | EFh X 24h | X CDh | <u>χ</u> 30h | X 2Fh   | χ poh )        | ( F2h ) | ( 1Eh.       | X 04h        | (F3h    | FBh            |

| ⊞-hybrid_fsm:instidin  | ( F6h X F7h  | <u>X 13h</u> | χ <u>15</u> ħ | (FFA )         | F2h       | X E4h | X FBh        | X 15h   | X F8h          | (EEn)   | χ <u>24h</u> | X 26h        | (ESh    | (FBh )         |

| ⊞- hybrid_fsminstlyout | Oốh          | X FFh        | ( 00n         | ( 02h          | <u> </u>  | X FFb | X Oth        | X 00h ) | X FI           | 2n )    | (FFh         | Х озн        | ( 02h ) | (FPh)          |

| ⊕ hybrid_faminstie.    | ( F5h )( F6h | X F8h        | X 13h         | <u>( 16h )</u> | Fin X Fin | X F3h | X E3h        | X FBh   | ( <u>18h</u> ) | (FBh)   | (EFn         | ( <u>21h</u> | (24h    | ( <u>E6h</u> ) |

(a) WGN input

| Name                   | -3 -    | 2 -     | 1     | 2              | 1     | 2            |        | 4             | 5       | <u>Ş</u> | l     | 8     | 9 1    | p 1     | 1 1    | 2 13   |

|------------------------|---------|---------|-------|----------------|-------|--------------|--------|---------------|---------|----------|-------|-------|--------|---------|--------|--------|

| j⊡ hybrid_fsmiinstixin | (167)   | ( 11h ) | ( 06h | (02h)          | (FFh  | (FSh)        | (FSh ) | <u> (</u> F2h | X EDh 🗍 | (DBh)    | (CZh  | (Afh  | X ACh  | (DFh)   | (06h)  | (FDn)  |

| ⊡- hybrid_fsminstidin  | ( 01h ) | (14h)   | ()    | ( 00h )        | ( 07h | ( F8n )      | (EEh)  | <u>(</u> εթ)  | X 66h   | ( F7h )  | ( son | X 05h | X .00h | (FCh; ) | (FDh ) | (FAn ) |

| ⊕ hybrid_fsm:instyout  |         | Oan     |       | <b>(</b> Я     | ħ     | ( <u>00h</u> | (FFh)  | X             | đợn     | ि        | ( F   | Fh    | X0     | 3h )    | (F     | Fh     |

| ⊕ hybrid_fsminste      | (EFb)   | ( 01h ) | ( 14h | ( <u>13</u> h) | ( OEh | ( 07h        | (F9h)  | X EEh         | X EFh   | (FGh)    | ( F8h | ( 01h | X 05h  | ( 00h ) | (FDh)  | (FEn)  |

(b) CSS input

Figure 4.11: Captured waveforms from hardware implementation.

FPGA IMPLEMENTATION OF PIPELINED DNLMS ADAPTIVE FILTER

₽

Figure 4.12: Results from hardware simulations.

identical to the RTL simulation plots in Fig. 4.7 and differ the fixed-point simulation plots in Fig. 4.6(a) and Fig. 4.6(b) by a delay of one clock period. Again, this is due to buffering of the input.

# Chapter 5

# Conclusions and Future Work

This thesis has focused on the implementation of the DNLMS adaptive filter for echo cancellation. The DNLMS algorithm is of interest because unlike the NLMS algorithm, DNLMS allows pipelining, which in turn facilitates low-power or highspeed architectures. Two issues related to the implementation were addressed.

The first issue is that echo cancellation typically requires high-order adaptive filters which induce high power and area consumption. Application of computationallyefficient techniques to the DNLMS algorithm has been considered. POT quantization was applied to the DNLMS algorithm, which has simplified multiplication/division to a single shift. Simplifying such computationally-intensive operations has the effect of reducing power and area consumption. The DNLMS algorithm was also modified by using the M-Max algorithm and a SAG algorithm. Both reduce the amount of computations by scheduling less weight updates. Having less computations results in decreased switching activity in the device, which reduces the dynamic power consumption. For the SAG algorithm, a new and effective stopping criterion related to

the regressor energy has been introduced. NEC and AEC simulations have shown that, compared to the standard NLMS algorithm, the proposed algorithm experienced only moderate performance degradation when using either WGN input or ITU G.168 CSS input.