#### **University of Windsor**

# Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

10-5-2017

# FPGA IMPLEMENTATION FOR ELLIPTIC CURVE CRYPTOGRAPHY OVER BINARY EXTENSION FIELD

Che Chen

University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Chen, Che, "FPGA IMPLEMENTATION FOR ELLIPTIC CURVE CRYPTOGRAPHY OVER BINARY EXTENSION FIELD" (2017). *Electronic Theses and Dissertations*. 7243.

https://scholar.uwindsor.ca/etd/7243

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# FPGA IMPLEMENTATION FOR ELLIPTIC CURVE CRYPTOGRAPHY OVER BINARY EXTENSION FIELD

by

Che Chen

A Thesis

Submitted to the Faculty of Graduate Studies

through the Department of Electrical and Computer Engineering

in Partial Fulfillment of the Requirements for

the Degree of Master of Applied Science

at the University of Windsor

Windsor, Ontario, Canada

2017

© 2017 Che Chen

# FPGA IMPLEMENTATION FOR ELLIPTIC CURVE CRYPTOGRAPHY OVER BINARY EXTENSION FIELD

by

Che Chen

APPROVED BY:

D. Wu School of Computer Science

R. Rashidzadeh Department of Electrical and Computer Engineering

H. Wu, Advisor Department of Electrical and Computer Engineering

#### **AUTHOR'S DECLARATION OF ORIGINALITY**

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

#### **ABSTRACT**

Elliptic curve cryptography plays a crucial role in network and communication security. However, implementation of elliptic curve cryptography, especially implementation of scalar multiplication on an elliptic curve, faces multiple challenges. One of the main challenges is side channel attacks (SCAs). SCAs pose a real threat to the conventional implementations of scalar multiplication such as binary methods (also called doubling-and-add methods). Several scalar *multiplication* algorithms with countermeasures against side channel attacks have been proposed. Among them, Montgomery Powering Ladder (MPL) has been shown an effective countermeasure against simple power analysis. However, MPL is still vulnerable to certain more sophisticated side channel attacks. A recently proposed modified MPL utilizes a combination of sequence masking (SM), exponent splitting (ES) and point randomization (PR). And it has shown to be one of the best countermeasure algorithms that are immune to many sophisticated side channel attacks [11]. In this thesis, an efficient hardware architecture for this algorithm is proposed and its FPGA implementation is also presented. To our best knowledge, this is the first time that this modified MPL with SM, ES, and PR has been implemented in hardware.

# **DEDICATION**

To my loving parents:

Father: Zhanming Chen Mother: Chun Xu

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor Dr. Huapeng Wu for his patient instruction on my thesis. Dr. Wu is the most knowledgably and kind professor I have ever met, and offered many invaluable opinions and advices during my study and work. I also thank Dr. Dan Wu for his feedbacks on the thesis, and Dr. Rashid Rashidzadeh for his detailed comment to improve this thesis.

Additionally, I would like to appreciate my loving parents. Without their support and encouragement, it is impossible for me to achieve such accomplishment.

I would also grateful to all my colleagues and friends for their support and time. Finally, I wish to show my gratitude to everyone at the Faculty of ECE for the help I received.

# TABLE OF CONTENTS

| AUTHOR'S DECLARATION OF ORIGINALITY               | iii  |

|---------------------------------------------------|------|

| ABSTRACT                                          | iv   |

| DEDICATION                                        | V    |

| ACKNOWLEDGEMENTS                                  | vi   |

| LIST OF TABLES                                    | x    |

| LIST OF FIGURES                                   | xi   |

| LIST OF ALGORITHMS                                | xii  |

| LIST OF ACRONYMS                                  | xiii |

| CHAPTER I INTRODUCTION                            | 1    |

| 1.1 Motivation                                    | 1    |

| 1.2 Summary of Contribution                       | 4    |

| 1.3 Thesis Organization                           | 5    |

| CHAPTER II MATHEMATICAL BACKGROUND                | 6    |

| 2.1 Finite Field                                  | 6    |

| 2.2 Elliptic Curve over $GF(2^m)$                 | 7    |

| 2.3 Elliptic Curve Public Key cryptography        | 10   |

| 2.3.1 System Setup                                | 10   |

| 2.3.2 Generation of the Key Pairs                 | 10   |

| 2.3.3 Elliptic Curve Integrated Encryption Scheme | 11   |

| 2.3.4 Elliptic Curve Diffie-Hellman Key Exchange  | 12   |

| 2.3.5 Elliptic Curve Digital Signature Algorithm  | 13   |

| CHAPTER III SIDE CHANNEL ATTACKS                  | 15   |

| 3.1 Timing Attack                                 | 16   |

| 3.2 Fault Attack                                  | 16   |

| 3.3 Electromagnetic Attack                                    | 17             |

|---------------------------------------------------------------|----------------|

| 3.4 Power Analysis Attack                                     | 18             |

| CHAPTER IV EXISTING WORK REVIEW AND SECURITY ANALY            | <b>YSIS</b> 20 |

| 4.1 Classical Binary Algorithm                                | 21             |

| 4.2 Double-and-Add Always Algorithm                           | 23             |

| 4.3 Non Adjacent Form Method                                  | 25             |

| 4.4 Montgomery Powering Ladder Algorithm                      | 27             |

| 4.4.1 Explanation of Algorithm                                | 27             |

| 4.4.2 Advantage of MPL                                        | 28             |

| 4.4.3 Relative Doubling Attack against MPL                    | 29             |

| 4.4.4 M-Safe Error Attack against MPL                         | 30             |

| 4.4.5 Comparative Power Analysis against MPL                  | 31             |

| 4.4.6 MPL Based Hardware Implementation                       | 30             |

| CHAPTER V ANALYSIS OF MODIFIED MPL WITH COUNTERME             | ASURES .33     |

| 5.1 Existing Countermeasure Techniques                        | 33             |

| 5.1.1 Coron's three countermeasures to DPA                    | 33             |

| 5.1.2 Exponent Splitting                                      | 34             |

| 5.1.3 Blinded Fault Resistant Exponentiation                  | 35             |

| 5.2 Security Analysis of Existing Countermeasure Techniques   | 36             |

| 5.2.1 High-Order Attack                                       | 36             |

| 5.2.2 Template Attack.                                        | 38             |

| 5.3 Modified MPL with sequence masking and exponent splitting | 39             |

| 5.3.1 Algorithm Explanation                                   | 39             |

| 5.3.2 Security Analysis                                       | 42             |

| CHAPTER VI PROPOSED HARDWARE IMPLEMENTATION                   | 46             |

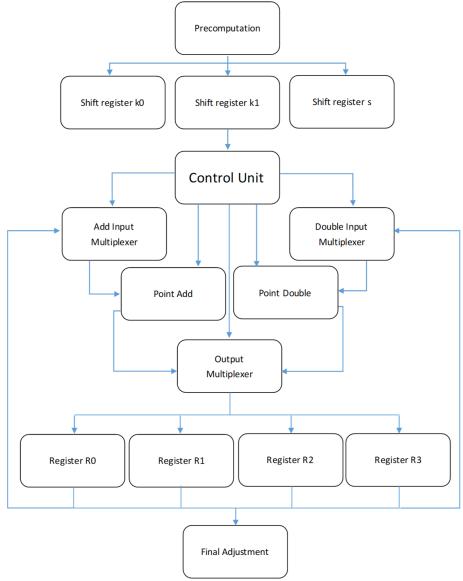

| 6.1 Hierarchical of ECC Architecture                          | 46             |

| 6.2 Random Number Generation                                  | 47             |

| 6.3 Addition in $GF(2^m)$                                     | 49             |

| 6.4 Multiplication in $GF(2^m)$                               | 49             |

| 6.5 Squaring in GF(2 <sup>m</sup> )                           | 50             |

| 6.6 Inversion in $GF(2^m)$                       | 51 |

|--------------------------------------------------|----|

| 6.7 Elliptic Curve Group Operations              | 53 |

| 6.8 Scalar Multiplication                        | 54 |

| 6.9 Synthesis Results                            | 56 |

| CHAPTER VII DISCUSSION AND POSSIBLE FUTURE WORKS | 60 |

| 7.1 Discussion                                   | 60 |

| 7.2 Possible Future Work                         | 60 |

|                                                  |    |

| REFERENCES                                       | 62 |

| APPENDICES                                       | 68 |

| VITA AUCTORIS                                    | 76 |

# LIST OF TABLES

| 1.1   | Public key systems and the hard math problems                                | 2 |

|-------|------------------------------------------------------------------------------|---|

| 1.2   | A comparison of key sizes                                                    | 3 |

| 3.1   | Category of SCAs                                                             | 6 |

| 4.1   | Doubling attack against double-and-add always algorithm                      | 4 |

| 4.2   | Doubling attack against NAF method                                           | 6 |

| 4.3   | Relative doubling attack against MPL                                         | 0 |

| 5.1   | Probability transition                                                       | 7 |

| 5.2   | An example of bit-level imbalance [36]                                       | 8 |

| 6.1   | NIST-recommended parameters                                                  | 6 |

| 6.2   | Hardware usage of different algorithms implemented                           | 6 |

| 6.3   | FPGA implementation complexity comparison between proposed design and        |   |

| rela  | ted works5                                                                   | 7 |

| 6.4   | Comparison of SCA countermeasure property between proposed work and existing |   |

| re la | ted works5                                                                   | 8 |

# LIST OF FIGURES

| 2.1 Point addition on ECC.                                    | 8  |

|---------------------------------------------------------------|----|

| 3.1 Traditional cryptosystem                                  | 15 |

| 4.1 Vulnerability of binary method to SPA                     | 22 |

| 4.2 Comparative power analysis against MPL                    | 32 |

| 5.1 Resistance of Algorithm 5.2 to relative doubling attack   | 43 |

| 6.1 Hierarchical architecture for computation involved in ECC | 47 |

| 6.2 233-bit LFSR                                              | 48 |

| 6.3 Multiplication unit                                       | 50 |

| 6.4 Squaring a polynomial                                     | 51 |

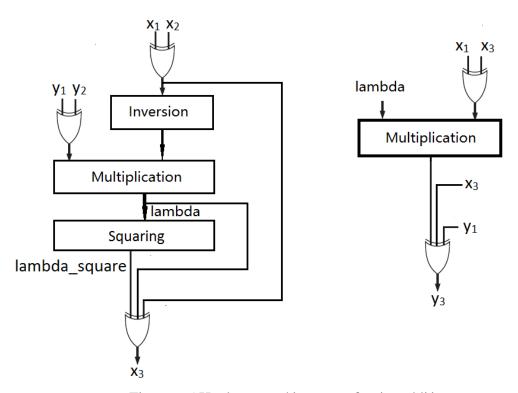

| 6.5 Hardware architecture of point addition                   | 53 |

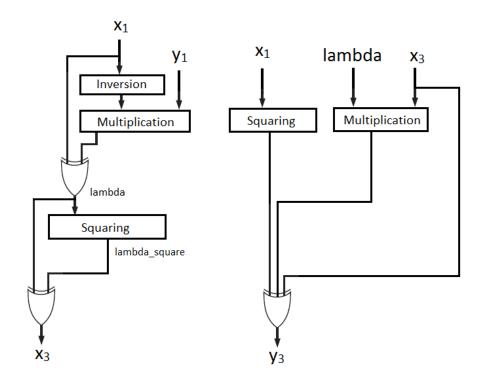

| 6.6 Hardware architecture of point doubling                   | 54 |

| 6.7 Architecture of proposed implementation                   | 55 |

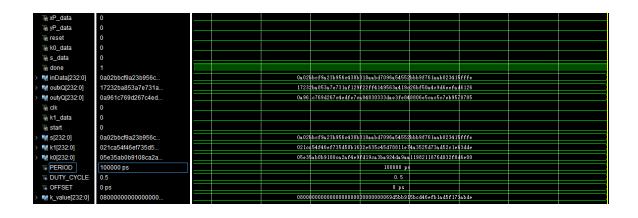

| 6.8 Output waveform                                           | 56 |

# LIST OF ALGORITHMS

| 4.1 Right to left version of double-and-add method  | 20 |

|-----------------------------------------------------|----|

| 4.2 Left to right version of double-and-add method. | 21 |

| 4.3 Double-and-add always method.                   | 23 |

| 4.4 Non adjacent form method                        | 25 |

| 4.5 Montgomery powering ladder                      | 28 |

| 5.1 Masked montgomery powering ladder               | 35 |

| 5.2 Modified MPL with SM, ES and PR                 | 41 |

| 6.1 Extended euclidean method [42]                  | 52 |

#### LIST OF ACRONYMS

DPA Differential Power Analysis

ECC Elliptic Curve Cryptosystem

ECDHKE Elliptic Curve Diffie-Hellman Key Exchange

ECDLP Elliptic Curve Discrete Logarithm Problem

ECDSA Elliptic Curve Digital Signature Algorithm

ECIES Elliptic Curve Integrated Encryption Scheme

EM Electro Magnetic

FPGA Field-programmable Gate Array

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

LUT Look Up Table

MPL Montgomery Powering Ladder

MVN Multivariate Normal Distribution

RSA Rivest, Shamir, Adleman

SCA Side Channel Attack

SPA Simple Power Analysis

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Motivation

The Internet is increasingly important to the people all over the world who use it for personal and business purposes. While the internet brings much convenience to people, there still exist security risks and vulnerabilities in using the internet. For example, various cyber-attacks, including side channel attacks, pose a great danger for the Internet users. Network security, which provides physical and software countermeasures to protect the network from unauthorized access and attacks, becomes a very active research area and industry. Cryptography plays a critical role in providing essential and unique network security services to the internet.

There are two main families of cryptography from the point of view of key generation, symmetric-key cryptography and asymmetric-key cryptography. In symmetric-key cryptography system, there is only one key used both for encryption and decryption. This system requires that both parties involved in the communication share one secret key, which has to be pre-arranged in advance in a procedure called key establishment. This is regarded as a main drawback of symmetric-key cryptography system since it cannot resolve the issue of key establishment without resorting to a third party.

Unlike symmetric-key cryptography system, the asymmetric-key cryptography system (more popularly known as public-key system) uses two keys, one for encryption and the other for decryption. The key used for encryption is the public key, which is accessible to the public and can be distributed widely and easily. The other one used for decryption is the private key, which must be kept secret and is only known to the owner of

the cryptosystem. By differentiating the encryption key and decryption key, the asymmetric-cryptography system can provide very important and unique security services such like key exchange and digital signature. A drawback of asymmetric-cryptography systems is that they have higher computational complexity, compared to symmetrical key systems.

Since Diffie and Hellman proposed the Diffie-Hellman key exchange scheme as the first asymmetric-cryptography system in 1976 [3], several asymmetric-key cryptography systems have been presented, such like RSA, ElGamel, and Elliptic curve cryptography. All these algorithms are based on some different hard mathematical problems. Based on their underlying mathematical problems, these algorithms can be classified as follows.

| Public key system           | Hard Math Problems                        |

|-----------------------------|-------------------------------------------|

| RSA                         | Integer factorization                     |

| ElGamal                     | Discrete logarithm problem                |

| Elliptic curve cryptosystem | Elliptic curve discrete logarithm problem |

Table 1.1 Public key systems and the hard math problems

The security strength of the cryptosystem relies on the fact it is hard to solve these mathematical problems. The Elliptic Curve Cryptosystem (ECC), first proposed by Miller and Koblitz in 1985 [1], [2], can provide higher security strength per bit compared to other asymmetric-cryptography system such like RSA. This is because elliptic curve discrete logarithm problem (ECDLP) is much harder to solve than factorization of a product of two large primes.

| Security Level (bits) | RSA Key Size (bits) | ECC Key Size (bits) |

|-----------------------|---------------------|---------------------|

| 00                    | 1024                | 1.00                |

| 80                    | 1024                | 160                 |

| 112                   | 2048                | 224                 |

|                       |                     |                     |

| 128                   | 3072                | 256                 |

| 102                   | 7690                | 294                 |

| 192                   | 7680                | 384                 |

| 256                   | 15360               | 512                 |

|                       |                     |                     |

Table 1.2 A comparison of key sizes

The large RSA key size requires long computation time and large VLSI area when implemented in hardware. While ECC is based on the elliptic curve discrete logarithm problem, the security of ECC relies on the difficulty of elliptic curve discrete logarithm problem. ECC can provide same level security strength as RSA with much shorter keys. Table 1.2 shows a comparison of key sizes needed to achieve equivalent level of security strength. This feature of ECC makes it very suitable for smart cards, credit cards, pagers, PDAs and mobile phones [4].

Other than solving the difficult ECDLP to break ECC mathematically, attackers can take advantage of the physical implementation and retrieve secret parameters by observing the information leaked during the computation. This method is referred to as Side Channel Attacks (SCA) and discussed in [5], [6]. Scalar multiplication, which multiplies a point on an elliptic curve by a scalar, is the main computation involved in ECC. Unguarded scalar multiplication algorithms are vulnerable to SCAs. In order to protect

ECC from SCA, the computation steps involved in the scalar multiplication algorithms have to be regular so that less useful side channel information can be leaked to attackers. There have been several existing algorithms for computing the scalar multiplication. A classical algorithm is the binary algorithm or doubling-and-add., it can be easily cracked by Simple Power Analysis (SPA) since it may consume different power in each iteration, depending on binary bit of the scalar. To withstand SPA, a double and add always algorithm is proposed by Coron in 1999 [7]. The idea is to add a dummy operation to make every iteration consume same power, thus the computation is regular in each step. However, this algorithm still remains insecure against a doubling attack proposed by Fouque in 2003 [8]. To provide further protection against various SCAs, Montgomery Powering Ladder (MPL) is invented by Marc Joye and Sung-Ming Yen in 2003 [9]. Although MPL is highly regular and efficient compared to the classical algorithms, it is still subject to SCAs such like Differential Power Analysis (DPA). Introduced by Kocher in 1999 [10], Differential Power Analysis focus on capturing the power consumption of the target device and by analyzing the power consumption to get information of the secret key. Another Modified Montgomery Power Ladder algorithm proposed by He in [11] can provide protection to more SCAs than the regular MPL. To the best of our knowledge, scalar multiplication based on this algorithm has not yet been implemented. Thus an efficient implementation of ECC, which can resist more SCAs is needed for modern cryptographic applications.

#### 1.2 A Summary of Contributions

In this thesis we propose an efficient hardware architecture for the modified MPL with sequence masking (SM), exponent splitting (ES) and point randomization (PR)

algorithm [11]. More specifically we

- Proposed an efficient hardware architecture for the modified MPL with SM,

ES and PR algorithm [11].

- Presented a FPGA implementation for the modified MPL with SM, ES and

PR algorithm [11], which is the first time in literature.

#### 1.3 Thesis Organization

The rest of the thesis is organized as follows. Chapter II provided mathematical background in finite field and elliptic curve which are important for understanding the proposed work. The concept of SCA is introduced and then many types of SCAs are reviewed in Chapter III. In Chapter IV an overview of existing related works is given. Chapter V provides a detailed discussion on a modified MPL with SM, ES and PR. Chapter VI proposes an efficient hardware architecture for the modified MPL with SM, ES and PR. FPGA implementation of the proposed architecture is also presented and the FPGA results are analyzed and discussed. Conclusive remarks are given and possible future works are commented in Chapter VII.

#### **CHAPTER II**

#### MATHEMATICAL BACKGROUND

This chapter introduces the related mathematical background of the ECC based systems. Definition of finite field and elliptic curve are given. Arithmetic over finite field, point operations over elliptic curve is also curved. Finally, some ECC scheme is introduced.

#### 2.1 Finite Field

Finite field, also known as Galois Field (GF), is proposed by Galois in 1832. Galois Theory emphasis a relation between groups and fields. Finite field was introduced as an example of a field. A finite field is a finite set of numbers in which addition and multiplication are defined. It is an additive group under the addition operation. All the nonzero elements in a finite field form a multiplicative group under multiplication operation. Primitive element is the generator of the multiplicative group. For a finite field F, if P is the smallest integer satisfying that P and P for every field element P in the finite field P, then P is the characteristic of P.

Prime finite field GF(p) consists of elements  $\{0,1,2...p-1\}$ , where p is a prime number. Arithmetic in GF(p) can be described as follows. Addition is defined as modulo-p addition. Multiplication is defined as modulo-p multiplication. p is the characteristic of GF(p).

Extension finite field  $GF(p^m)$ , where p is a prime and m is a positive integer greater than 1, the elements of  $GF(p^m)$  are polynomials of degree up to m-1 with coefficients belonging to GF(p),

$$GF(p^m) = \{a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_2x^2 + a_1x + a_0\}$$

where  $a_i \in GF(2)$ , irreducible polynomial is f(x). p is a prime and m is a positive integer

greater than 1, the elements of  $GF(p^m)$  are polynomials of degree up to m-1 with coefficients belonging to GF(p). The irreducible polynomial f(x) cannot be factored into product of polynomials that has degree less than m.

Binary Extension finite field  $GF(2^m)$  is a special case of  $GF(p^m)$ , where is consists of  $2^m$  elements and its characteristic is 2.

$$GF(2^m) = \{a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_2x^2 + a_1x + a_0\},\$$

where  $a_i \in GF(2)$ , irreducible polynomial is f(x). Elements in this field can be represented as (m-1) degree polynomial, for example if A is an element in  $GF(2^m)$ , A can be represented as

$$A = a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_2x^2 + a_1x + a_0$$

, where  $a_i \in GF(2)$

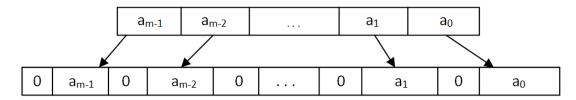

It can also be represented as an m bits binary string  $(a_{m-1}, a_{m-2}, ..., a_1, a_0)$ , where  $a_i \in GF(2)$ . This representation is defined as the polynomial basis representation. This representation is beneficial in hardware implementation since its operations like addition and multiplication can be realized using AND logic gate and XOR logic gate. The addition operation over binary extension field is modulo 2 addition. The multiplication is modulo f(x), modulo 2 multiplication.

#### 2.2 Elliptic Curve over GF(2<sup>m</sup>)

Let p be a prime number greater than 3, and coefficients a, b in the field GF(p), then the elliptic curve E over GF(p) is defined with equation:

E:

$$y^2 = x^3 + ax^2 + b$$

This equation is a simplified Weierstrass equation. The points on the curve satisfy that both the x-coordinate and y-coordinate are both elements over GF(p). Assume there

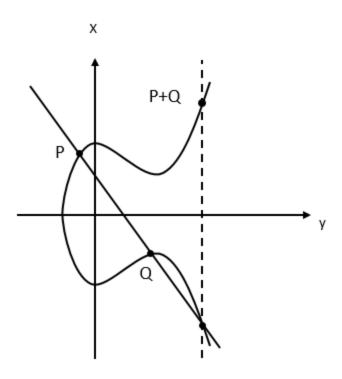

two points  $P(x_1,y_1)$  and  $Q(x_2,y_2)$  on the curve. The group operator point addition obeys the following rules. Draw a line through point P and Q, if there exists a third point  $R(x_3,y_3)$  which intersects with the curve. The mirror reflection of R about the x-axis is defined as the addition result. If such an intersection point does not exist, we consider the result as infinity. The point at infinity Q, defined by Q + Q = Q, exists for every elliptic curve. The additive inverse of point Q is its reflection across the Q-axis. All the points on curve Q and the point at infinity forms a group Q defined by the point addition operator. Q is an abelian group sine the group operator addition is commutative.

Figure 2.1 Point addition on ECC

If P and Q satisfy  $x_1 \neq x_2$ , then we have point addition computed using the following equation.

$$\begin{cases} \lambda = \frac{y_1 + y_2}{x_1 + x_2} \\ x_3 = \lambda^2 + x_1 + x_2 \\ y_3 = (x_1 + x_3)\lambda + y_1 \end{cases}$$

If P and Q satisfy P = Q and  $y_1 \neq 0$ , then point doubling is defined below.

$$\begin{cases} \lambda = \frac{3x_1^2 + a}{2y_1} \\ x_3 = \lambda^2 + 2x_1 \\ y_3 = (x_1 + x_3)\lambda + y_1 \end{cases}$$

For an integer k, scalar multiplication kP is defined as repeated addition like

$$kP = P + P + \cdots P$$

repeated for k times.

The order n of point P is defined as the minimal integer satisfies nP = 0.

Let a and b be elements in  $GF(2^m)$ . An elliptic curve E over  $GF(2^m)$  can be defined by the equation

E:

$$y^2 + xy = x^3 + ax^2 + b$$

Points over elliptic curve defined in  $GF(2^m)$  have similar operations to that defined in GF(p). Consider two points  $P(x_1,y_1)$  and  $Q(x_2,y_2)$  on the curve, and  $R(x_3,y_3)$  be the result of P+Q. If P=Q, point addition is computed as follows.

$$\begin{cases} \lambda = \frac{y_1 + y_2}{x_1 + x_2} \\ x_3 = \lambda^2 + \lambda + x_1 + x_2 + a \\ y_3 = (x_1 + x_3)\lambda + x_3 + y_1 \end{cases}$$

If  $P \neq Q$ , point doubling is performed as below.

$$\begin{cases} \lambda = \frac{y_1}{x_1} + x_1 \\ x_3 = \lambda^2 + \lambda + a \\ y_3 = x_1^2 + \lambda x_3 + x_3 \end{cases}$$

All the addition, multiplication and inversion involved in there equations are finite field arithmetic. The most time consuming operations are finite field multiplication and inversion.

#### 2.3 Elliptic Curve

For a given field GF(p) and curve E over the field, it is easy to calculate kP for a point P on the curve. However, if kP and P is known, it is considered very difficult to calculate integer k. This is called the ECDLP problem, and the security strength of ECC relies on it.

### 2.3.1 System Setup

To setup a secure elliptic curve cryptography system, the parameters of the curve has to be chosen very carefully. The elliptic curve used in the system need to be non-singular since singular curves are easy to crack.

The parameters needed to construct an elliptic curve cryptography system including the following. Finite field GF(p) defined by p, elliptic curve E defined by a and b, base point P, the order of the base point n and the factor h. The parameter set is known to the public.

If the system is over GF(p), the parameter set is  $D = \{p, a, b, P, n, h\}$ . The parameters are defined as above stated. If the cryptography system is built over  $GF(2^m)$ , the parameter set is  $D = \{m, f(x), a, b, P, n, h\}$  where f(x) is the irreducible polynomial define the field. To calculate factor h, first count all the points and the point at infinity to get the order of the elliptic curve #E, then h is #E divided by n.

#### 2.3.2 Generation of the key pairs

After the system is set up, assume Bob is trying to communicate with Alice. Alice

will choose the keys as introduced below.

Step 1: Choose a random integer  $d \in [1, n-1]$

Step 2: Computes point Q = dP

The public key is point Q, and private key is integer d.

#### 2.3.3 Elliptic Curve Integrated Encryption Scheme (ECIES)

The most extended encryption and decryption scheme based on ECC is the Elliptic Curve Integrated Encryption Scheme (ECIES). This scheme is a variant of the ElGamal scheme proposed in [12]. This scheme is described as follows:

System Setup:

Step 1: Alice sets the ECC system parameter sets  $D = \{p, a, b, P, n, h\}$

Step 2: Computes Key Pair (Q, d)

Encryption:

Step 1: Bob selects a random number  $k \in [1, n-1]$

Step 2: Computes R = kP, and Z = hkQ.

Step 3: X-coordinate of Z and R is converted to  $(k_1,k_2)$  using a key derivation hash function

Step 4: Message m is encrypted with  $k_1$  using a symmetrical key cipher to get C = ENC(m)

Step 5: Computes t = MAC(C) using  $k_2$ , where MAC is a message authentication code

Step 6: Cipher text (R, C, t) is sent to Alice

Decryption:

Step 1: Alice computes Z = hdR

Step 2: X-coordinate of Z and R is converted to  $(k_1, k_2)$  using a key derivation hash

function

Step 3: Computes t = MAC(C) using  $k_2$ , where MAC is a message authentication code

Step 4: Message m is decrypted with  $k_1$  using a symmetrical key cipher to get m = DEC(C)

This scheme works since when Alice generates Z, it follows that,

$$Z = hdR = hd(kP) = hk(dP) = hkQ$$

So both the encryption and decryption generate the same key pair  $(k_1, k_2)$ .

#### 2.3.4 Elliptic Curve Diffie-Hellman Key Exchange (ECDHKE)

ECDHKE is the generic key exchange scheme based on the Diffie-Hellman mechanism applied to elliptic curves [13]. The information available to the public is the elliptic curve E over GF(p), and a point P with order n on the curve. The computations are described as follows:

Computation of Alice:

Step 1: Alice chooses random number  $a \in [1, n-1]$

Step 2: Computes  $\alpha P$  and it is sent to Bob

Step 3: After receiving bP form Bob, Alice computes scalar multiplication a(bP) to get abP

Computation of Bob:

Step 1: Bob chooses random number  $b \in [1, n-1]$

Step 2: Computes bP and it is sent to Alice

Step 3: After receiving aP form Alice, Bob computes scalar multiplication b (aP) to get baP

The secret key shared by the two parties is k = abP. By applying this scheme, the

secret key is securely exchanged.

### 2.3.5 Elliptic Curve Digital Signature Algorithm (ECDSA)

ECDSA is the elliptic curve variant of the Digital Signature Algorithm [14]. This scheme can be introduced as the following steps:

System Setup:

Step 1: Alice sets the ECC system parameter sets  $D = \{p, a, b, P, n, h\}$

Step 2: Computes Key Pair (Q, d)

Signing of the message:

Step 1: Alice calculates e = H(m), where H is a hash function.

Step 2: Chooses random number  $k \in [1, n-1]$

Step 3: Calculates point  $R = kP(x_1, y_1)$ .

Step 4: Calculates  $sig_1 = x_1 \mod n$ . If  $sig_1 = 0$ , Alice chooses another k.

Step 5: Calculates  $sig_2 = k^{-1}(e + dx_1) \mod n$ .

Step 6: The signature is the pair  $(sig_1, sig_2)$ .

Verification of the signature:

Step 1: Bob calculates e = H(m), where H is a hash function.

Step 2: Calculates  $w = sig_2^{-1} \mod n$ .

Step 3: Calculates  $u_1 = ew \mod n$  and  $u_2 = sig_1w \mod n$ .

Step 4: Calculates point  $X = u_1P + u_2Q$  and retrieve the x-coordinate of X denoted by  $x_2$

Step 5: The signature is valid if  $sig_1 = x_2 \mod n$ , if not the signature is rejected.

To prove the correctness of the algorithm, the following equation can be performed.

$$\begin{split} X &= u_1 P + u_2 Q \\ &= u_1 P + u_2 d \times P \\ &= (u_1 + u_2 d) \times P \\ &= (e \times sig_2^{-1} + sig_1 \times sig_2^{-1} d) \times P \\ &= (e + sig_1 d) sig_2^{-1} \times P \\ &= (e + sig_1 d) (e + sig_1 d)^{-1} (k^{-1})^{-1} \times P = kP \end{split}$$

Thus from the computation it is verified  $sig_1 = x_2 \mod n$  from point X = kP.

From all the above algorithms, it can be seen that scalar multiplication is the main computation involved in elliptic curve cryptography. SCAs mainly target the scalar multiplication in ECC to compromise partial or the full secret key.

#### **CHAPTER III**

#### SIDE CHANNEL ATTACKS

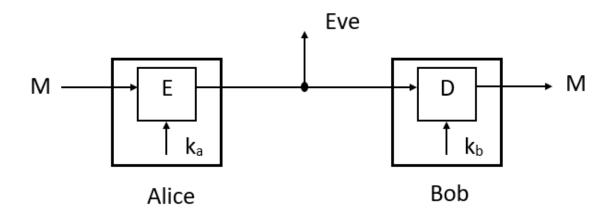

To consider a cryptosystem under mathematically circumstances, a black-box model is usually used. In the black-box scheme, attackers cannot get any intermediate computation results [15]. The only information available to the attackers are plaintext and cipher text. Thus in order to break the cryptosystem, the attackers need to solve the hard math problem such like ECDLP in ECC.

Figure 3.1 Traditional cryptosystem

However, such model is not adequate under most scenarios in practice. When a cryptosystem is implemented on hardware, there will be unintended information leaked during the execution of the algorithm. The attackers thus can try to find correlation between the leaked information and the secret key. Side Channel can be classified based on the types of side channel information. Information can be extracted from timing, power consumption or electromagnetic radiation features. Hardware or software faults, computational errors, and changes in frequency or temperature can also lead to leak of information. Table 3.1 shows the relation between leaked information and type of side channel attacks.

| Side Channel Information  | Side Channel Attacks        |

|---------------------------|-----------------------------|

| D                         | Simple power analysis(SPA)  |

| Power traces              | Differential power analysis |

|                           | Comparative power analysis  |

| Time                      | Timing attack               |

| Faults and error          | Fault attack                |

| Electromagnetic radiation | EM attack                   |

Table 3.1 Category of SCAs

#### 3.1 Timing Attack

Many of the implementations of cryptographic algorithms perform the computations in a non-constant time. The time variations sometimes can become a breakthrough point of the system. If the difference of time is correlated to the secret parameters, then a statistical analysis can reveal enough information to access the key. Timing attack was first introduced by Kocher in [5].

The working principle of timing attack is to capitalize on the time difference, thus an easy countermeasure is to make the implementation on the hardware equalize the computation time in each step.

#### 3.2 Fault Attack

The idea of fault attack is to inject a fault and force the system to leak information related to the secret parameter. Fault attack was first introduced in [16]. Consider a hardware implementation of a cryptosystem, the execution of a fault attack usually two steps [17]. The first step is to inject a fault and the second step is to do a cryptanalysis based on the erroneously result.

Among the many fault attacks, differential fault attack (DFA) caught most attention of the scientists and researchers. To initialize DFA, a bit error is enforced into the hardware before or during the computation. By analyzing the correct result and the erroneous result, the information of the secret key is compromised. Biehl and Müller proposed an effective DFA against ECC in 2000 [18]. The main idea is to construct a reference elliptic curve  $E_r$  and choose a reference point  $P_r$  on the Curve. By inputting this reference point into the tamper-proof hardware, the reference result  $d \times P_r$  on the curve is  $E_r$  computed. Since curve  $E_r$  is carefully chosen that the order of the curve has a factor r equals to the order of  $P_r$ , the ECDLP is deduced to the subgroup of order r. Next another reference point is carefully chosen and the whole process is duplicated. The secret parameter d can be revealed.

Yen and Joye introduced another fault attack scheme in [19], this attack targets the algorithms with dummy operations. By carefully timing a fault injection, the attacker can distinguish whether this fault causes an error in the result. Thus it can be known whether a redundant operation is executed. By repeating the procedure, the whole secret key can be retrieved. This attack is called safe-error attack.

#### 3.3 Electromagnetic Attack

Electromagnetic (EM) attack [20] is based on the fact that all electrical device radiates electromagnetic waves when operating. An adversary examines the changes of the electromagnetic field first and then an electromagnetic analysis is executed trying to extract the secret information.

Wu and Yu introduced an EM attack against scalar multiplication in [21]. The attacker is targeting a classical binary algorithm. The electromagnetic traces captured have

significant difference when different computation is executed. Thus it is easy to access the secret key by comparing the power traces.

#### 3.4 Power Analysis Attack

Similar to EM attacks, power consumption is often leaked during the running process of the cryptographic device. By observing the power traces, attackers can get access to the information on where a certain operation happened and what secret parameter is involved. Since power analysis attacks usually use little resources, power constrained applications such like smart cards are primary targets of it [22].

Power analysis attack can be generally categorized into two types, simple power analysis (SPA) and differential power analysis (DPA). SPA attacker examines the power traces of cryptography computations and distinguish the power consumption caused by the secret key. The attacker tries to get secret information by observation of repetitive patterns in the obtained power traces. If power consumptions are distinguishable the information of secret key is leaked. DPA relies on the statistical analysis to reveal the correlation between the secret bit and power consumption. It is usually executed in two steps. First the power traces are captured, then analysis regarding the captured information is carried out. Among all the various SCAs, DPA is being regarded as one of the strongest. The difference lies in that despite merely observation of the power spectrum, DPAs employ more statistical methods to guess the secret key.

Coron shows in [7] how DPAs work against scalar multiplication, which is the main computation in ECC. Since in many scalar multiplication algorithms, the result is computed by continuous point addition chain. That is, given a point P and scalar d, dP is calculated as:

$$P \rightarrow d_0 P \rightarrow d_1 P \rightarrow d_2 P \rightarrow d_3 P \rightarrow \cdots \rightarrow dP$$

The attacker starts guessing from  $d_0 = 1$  to d. For each  $d_i$ , a set  $A_i$  with all possible  $d_i = d_j + d_k$  where  $0 \le j \le k < i$  is built. For each element  $d_i$  in the set  $A_i$ , the correlation of power consumption and  $d_i P$  is computed. When the peak is achieved in the computation, the desired  $d_i$  is recovered. By repeating the same pattern for  $d_0 = 1$  to d, the secret key d will be compromised at last.

#### CHAPTER IV

#### EXISTING WORK REVIEW AND SECURITY ANALYSIS

There have been different scalar multiplication algorithms existing to improve the overall performance for efficient or security. In this chapter we introduce the different algorithms and their implementations. Also the security strength of these algorithms will be analyzed.

#### 4.1 Classical binary algorithm

The binary algorithm is also known as the "square and multiply method" to do exponentiation calculation. It is a very old algorithm which has over 2000 year's history [23]. While in the scalar multiplication scenario, it is very simply adapted as the double and add algorithm.

The basic idea of double and add algorithm is to make full use of the binary form of the scalar. Consider a point P and scalar k, rather than add point P to itself d times to get the result kP, the double and add method will obviously reduce number of addition operation needed.

The binary algorithm has two versions, one is from the least significant bit to the most significant bit shown in Algorithm 4.1.

Algorithm 4.1.Right to left version of double-and-add method

Input:

$$P \in E$$

,  $k = (k_{n-1}, ..., k_1, k_0)_2$ ,  $k_i \in 0,1$

Output:  $Q = kP \in E$

Step 1: x = 0, y = P;

Step 2: for i=0 to n-1 do

```

Step 3: if k_i = 1, then x = x + y

```

Step 4: end if

Step 5: y = 2y

Step 6: end for

Step 7:Return x

The other is calculating from the most significant bit to the least significant bit, as shown in algorithm 4.2.

Algorithm 4.2.Left to right version of double-and-add method

Input:  $P \in E, k = (k_{n-1}, ..., k_1, k_0)_2, k_i \in 0,1$

Output:  $Q = kP \in E$

Step 1: x = P;

Step 2: for i=n-2 down to 0 do

Step 3: x = 2x

Step 4: if  $k_i = 1$ , then x = x + P

Step 5: *end if*

Step 6: end for

Step 7: Return x

Although the addition operation is significantly reduced in the double-and-add algorithm, the drawbacks of this algorithm is crucial. Comparing the operations carried out when the secret bit  $k_i$  is different, it is clear that more computations are executed when

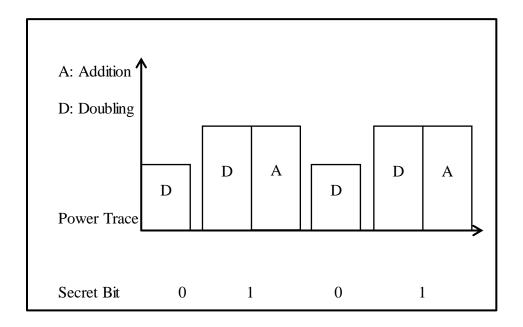

$k_i = 1$ . In every iteration, the doubling operation is always performed, while addition only happens when  $k_i = 1$ . This variation responses directly into the power consumption. As shown in Figure 4.1, D denotes doubling operation and A represents addition operation. The secret bit is chosen as  $k = (0101)_2$ . The length of the power peak is different, thus the attacker can observe the power traces and distinguish the secret bits. This figure shows exactly how the double-and-add algorithm is vulnerable to the SPA attack. Because of this major drawback, many other algorithms is have been developed.

Figure 4.1 Vulnerability of binary method to SPA

A high speed ECC processor is implemented by Hossain and Kong in 2015 [24]. Over field  $GF(2^{233})$ , their ECC processor can perform scalar multiplication 2.66 ms at 255.66 MHz in on a Xilinx Kintex-7 devices. This design features to speed up the overall computation time. They applies the double-and-add algorithm to the design in a trade-off for speed. As stated previously, this design can be easily crack by SCA attacks.

### 4.2 Double-and-Add Always Algorithm

In order to achieve more security strength against SPA, Coron proposed a double-and-add always algorithm in 1999 [7]. The main idea of this algorithm is to add a dummy operation to standard double-and-add to equalize the power consumption of each cycle. As illustrated in Algorithm 4.3, a dummy addition is executed when the processing bit is zero. In this way, the algorithm is performing a doubling followed by an addition in every iteration. Since the algorithm is regular now, it has resistance to SPA attacks.

Algorithm 4.3.Double-and-add always method

Input:  $P \in E, k = (k_{n-1}, ..., k_1, k_0)_2$ ,  $k_i \in 0,1$ Output:  $Q = kP \in E$ Step 1: x = 0, y = 0;

Step 2:  $for i = n - 1 \ down \ to \ 0 \ do$ Step 3: x = 2x;

Step 4: y = x + P;

Step 5:  $if \ k_i = 1, then \ x = y$ ;

Step 6:  $end \ if$ Step 7:  $end \ for$ Step 8:  $Return \ x$

However, another fault attack called c-safe error attack [9] can easily crack this algorithm. When the secret bit is zero, the addition result won't affect the final result. When the attacker altered one bit of the secret key to zero, the result can be compared with the original output. If the result remains the same, the attacker knows that the secret bit is zero.

In the case the result changed, the attacker will figure that the secret bit is one and it is quite easy to locate. This algorithm is taking as an unsuccessful sequence mask example since the countermeasure takes to prevent SPA benefits other attacks [26].

Another attack threatening this algorithm is the doubling attack, which proposed by Fouque and Valette in [25]. The name is from the fact this attack is based on the doubling operation in the scalar multiplication. This type of attack only works when using left to right algorithms. To better explain it, consider two points P, 2P and secret  $k=9=(1001)_2$  as input. Double-and-add always method is used to compute kP and k (2P). As illustrated in Table 4.1, if we focus the doubling operation in each iteration, some of them shares the same pattern. To be more specific, doubling operation at iteration 2 calculating k (2P) is the same as doubling operation at iteration 3 calculating kP. Thus two zeros is overserved by the adversary. This attack reveals all the bits with the value zero and using these information, the whole secret bits can be revealed consequently.

Table 4.1 Doubling attack against double-and-add always algorithm

| Iteration i | $k_i$ | kP                                      | k(2P)                                                   |

|-------------|-------|-----------------------------------------|---------------------------------------------------------|

| 3           | 1     | 2 × 0<br>0 + P                          | $\begin{array}{c} 2 \times 0 \\ 0 + 2P \end{array}$     |

| 2           | 0     | 2 × P<br>2P + P                         | $ \begin{array}{c} 2 \times 2P \\ 4P + 2P \end{array} $ |

| 1           | 0     | $ 2 \times 2P \\ 4P + P $               | $2 \times 4P$ $8P + 2P$                                 |

| 0           | 1     | 2 × 4 <i>P</i><br>8 <i>P</i> + <i>P</i> | 2 × 8 <i>P</i><br>16 <i>P</i> + 2 <i>P</i>              |

To the best knowledge, implementation for double-and-add always algorithm is very few since it is not efficiency compared to classical double-and-add. Although it has more resistance to SPA, it is still vulnerable to many other attacks such like safe error attack. This method later stimulated development of more advanced algorithms such like MPL.

## 4.3 Non Adjacent Form Method

As stated in previous chapter, a point P(x,y) on elliptic curve E over binary field, has additive inverse in the form -P = (x, x + y). Thus subtraction of point is actually the same as point addition on an elliptic curve. The non-adjacent form (NAF) is a signed digit representation [27] inspired by this fact. In NAF method, the secret key is represented by the following equation.

$$k = \sum_{i=0}^{l-1} k_i 2^i$$

, where  $k_i \in \{0, \pm 1\}, k_{l-1} \neq 0$

In this expression, there is no two continuous nonzero digits. The advantage of this representation is that generally it has fewer nonzero bits [23], which leads to a reduction of addition operation needed in the algorithm. The NAF method is shown in Algorithm 4.4.

Algorithm 4.4. Non Adjacent Form method

Input:

$$P \in E, NAF(k) = \sum_{i=0}^{l-1} k_i 2^i, k_i \in \{0, \pm 1\}$$

Output:  $Q = kP \in E$

Step 1: x = P, y = 0;

Step 2: for i=I-2 down to 0 do

Step 3: x = 2x;

Step 4: *if*  $k_i = 1$ , *then* x = x + P;

Step 5: else *if*  $k_i = -1$ , *then* x = x + (-P);

Step 6: end if

Step 7: end for

Step 8: Return x

The doubling attack mentioned in previous section still applies to the NAF method. Taking an integer k=29, and NAF(k)=(1,0,0-1,0,1). Then if the adversary calculates kP and takes k(2P) as a reference. From Table. 4.2, it is shown that the intermediate value at iteration i when computing k(2P) equals the result at iteration i-1 when computing kP. All the secret bits with value zero is thus revealed. Since approximately two third of the bits in NAF representation is zero [28], most bits are retrieved applying doubling attack.

Table 4.2 Doubling attack against NAF method

| Iteration i | $k_i$ | kP                        | k(2P)                       |

|-------------|-------|---------------------------|-----------------------------|

| 4           | 0     | 2 × P                     | 2 × 2P                      |

| 3           | 0     | 2 × 2 <i>P</i>            | 2 × 4P                      |

| 2           | -1    | $2 \times 4P$ $8P + (-P)$ | $2 \times 8P$ $16P + (-2P)$ |

| 1           | 0     | 2 × 7 <i>P</i>            | 2 × 14P                     |

| 0           | 1     | $2 \times 14P$ $28P + P$  | $2 \times 28P$ $56P + 2P$   |

Wang introduced his implementation of an ECC coprocessor over  $GF(2^{233})$  in 2005 [29]. In this paper, a digit-serial multiplier which can achieve half or quarter clock cycles compared to the full-serial multiplier is proposed. With proper precomputation, this design can reduce the total calculating time by applying the projective coordinates. The coprocessor can perform a scalar multiplication in 2.28 ms at 80 MHz. However, the implementation algorithm chosen by the author is NAF method which vulnerable to attacks like doubling attack.

### 4.4 Montgomery Powering Ladder Algorithm

#### 4.4.1 Explanation of Algorithm

The Montgomery powering ladder is first proposed in [9] to provide a countermeasure to SPA. For a given  $k = \sum_{i=0}^{l-1} k_i 2^i$ , in order to compute kP, the MPL is constructed based on the following relationships. Define  $L_j = \sum_{i=j}^{l-1} k_i 2^i$  and  $H_j = L_j + 1$ .  $L_j$  and  $H_j$  can then be represented as

$$\{ \begin{aligned} L_j &= 2L_{j+1} + k_j = L_{j+1} + H_{j+1} + k_j - 1. \\ H_j &= L_{j+1} + H_{j+1} + k_j \end{aligned}$$

So at iteration j, it is easy to express  $L_j$  and  $H_j$  using the previous values from iteration j + 1

$$(L_{j}, H_{j}) = \begin{cases} (2L_{j+1}, L_{j+1} + H_{j+1}) \text{ when } k_{j} = 0\\ (L_{j+1} + H_{j+1}, 2H_{j+1}) \text{ when } k_{j} = 1 \end{cases}$$

The above equations implies the structure of MPL. The calculations are very similar to each other and in each iteration one doubling is performed with one addition. Recall that the main computation of scalar multiplication is point doubling and point addition, the following algorithm is obtained.

Algorithm 4.5. Montgomery Powering Ladder

Input:  $P \in E$ ,  $k = (k_{n-1}, ..., k_1, k_0)_2$ ,  $k_i \in 0,1$

Output:  $Q = kP \in E$

Step 1: x = 0, y = P;

Step 2: for i=n-1 down to 0 do

Step 3: *if*  $k_i = 0$ , then y = x + y; x = 2x

Step 4: else if  $k_i = 1$ , then x = x + y; y = 2y

Step 5: end if

Step 6: end for

Step 7: Return x

#### 4.4.2 Advantage of MPL

In algorithm 4.5, it is obvious that the computations for point addition and point doubling are independent. Thus they can be calculated parallel. This feature results in faster calculation speed. Moreover, since in every circle, MPL executes the same operation, it is considered highly regular. This structure makes it invulnerable to SPA.

Another c safe-error attack introduced in previous section also has no effect to MPL. Unlike the double-and-add always algorithm, there is no dummy operation in MPL. So any fault injected will lead an error in the result.

The doubling attack is considered ineffective. Assume there are two registers  $R_0$  and  $R_1$  to store the intermediate values. It could be the value stored in  $R_0$  or  $R_1$  performs the doubling, depending on the secret bit. While the previous algorithms which are

vulnerable to doubling attack all shares the fixed doubling pattern, the attacker cannot see a repeated doubling operation when there is no continuous bits with the same value one or zero. But if there exists successive bits carrying the same value, the algorithm is vulnerable to a relative doubling attack proposed in [30].

## 4.4.3 Relative Doubling Attack against MPL

While the doubling attack mainly focus on finding the 0 bits, the relative doubling attack compares the value of two adjacent secret key bits. Let registers  $R_0$  store the value of  $L_i$ , and registers  $R_1$  store the value of  $H_i$ . If  $k_i = k_{i-1} = 0$ , the following doubling computation is observed.

$$\begin{cases} R_0 \leftarrow 2 \times L_i P \text{: iteration } i-1 \text{ when calculating } kP \\ R_0 \leftarrow L_{i+1} \times 2P \text{: iteration } i \text{ when calculating } k(2P) \end{cases}$$

Since  $L_i=2L_{i+1}$  when obviously the above equations are doing the same computation. Thus, if such collisions are observed, the attacker get the information  $k_i=k_{i-1}=0$ .

Similar situation applies to when  $k_i = k_{i-1} = 1$ . Then in register  $R_1$ ,

$$\begin{cases} R_1 \leftarrow 2 \times H_i P \text{: iteration } i-1 \text{ when calculating } kP \\ R_1 \leftarrow H_{i+1} \times 2P \text{: iteration } i \text{ when calculating } k(2P) \end{cases}$$

same computations will be carried because that  $H_i = 2H_{i+1}$ . While when ki is not equal to  $k_{i-1}$ , there is no collision detected.

Taking  $k=105=(1101001)_2$ , the adversary computes kP and k(2P) as the pattern shown in Table. 4.3. It is very clear that at iteration 1 and 2, collisions in register  $R_0$  is detected. This fact leads to secret key bits  $k_2=k_1=0$ . Taking iteration 5 and 6 as another example, the operations regarding values in register  $R_1$  is the same, thus the attacker figures  $k_6=k_5=0$ . When there is no collision happened, that means the two

adjacent secret bits are holding different values. Then the whole secret key is revealed from the collision location bit by bit.

Table 4.3 Relative doubling attack against MPL

| Iteration i | $k_i$ | kP                   | k(2P)                 |

|-------------|-------|----------------------|-----------------------|

| 6           | 1     | $R_0 = 0 + P$        | $R_0 = 0 + 2P$        |

|             |       | $R_1 = 2 \times P$   | $R_1 = 2 \times 2P$   |

| 5           | 1     | $R_0 = P + 2P$       | $R_0 = 2P + 4P$       |

|             |       | $R_1 = 2 \times 2P$  | $R_1 = 2 \times 4P$   |

| 4           | 0     | $R_0 = 2 \times 3P$  | $R_0 = 2 \times 6P$   |

|             |       | $R_1 = 3P + 4P$      | $R_1 = 6P + 8P$       |

| 3           | 1     | $R_0 = 6P + 7P$      | $R_0 = 12P + 14P$     |

|             |       | $R_1 = 2 \times 7P$  | $R_1 = 2 \times 14P$  |

| 2           | 0     | $R_0 = 2 \times 13P$ | $R_0 = 2 \times 26P$  |

|             |       | $R_1 = 13P + 14P$    | $R_1 = 26P + 28P$     |

| 1           | 0     | $R_0 = 2 \times 26P$ | $R_0 = 2 \times 52P$  |

|             |       | $R_1 = 26P + 27P$    | $R_1 = 52P + 54P$     |

| 0           | 1     | $R_0 = 52P + 53P$    | $R_0 = 104P + 106P$   |

|             |       | $R_1 = 2 \times 53P$ | $R_1 = 2 \times 106P$ |

#### 4.4.4 M-safe Error Attack against MPL

Despite the relative doubling attack, another fault attack M safe-error attack introduced in [19] is also proven to be effective against MPL. In this scheme, the fault induced by the attacker is temporary memory fault and it is very carefully timed. M safe-error attack takes advantage of the two distinct operations carried out in each cycle of MPL. Consider the different computation when  $k_i$  is different. When  $k_i = 1$ , the two operations are  $R_0 = R_0 + R_1$  and  $R_1 = 2R_1$ . Any fault injected into  $R_1$  will change the value of the result, thus it is not a safe error. If  $k_i = 0$ , then  $R_0 = 2R_0$  and  $R_1 = R_0 + R_1$  will be computed, error inputted into more significant bits of  $R_1$  will be erased after the

resigning of value in  $R_1$ . In other words, the result still remains and the error is regarded a safe-error. The attacker can retrieve the secret bit  $k_i$  based on the above fact.

## 4.4.5 Comparative Power Analysis against MPL

Comparative Power Analysis is proposed by Homma in 2010 [31]. It is a more powerful attack which can compromise multiple scalar multiplication algorithms such like double-and-add algorithm, double-and-add always algorithm and MPL algorithm. While the original attack introduced is aiming at implementation of exponentiation, it also applies to scalar multiplication.

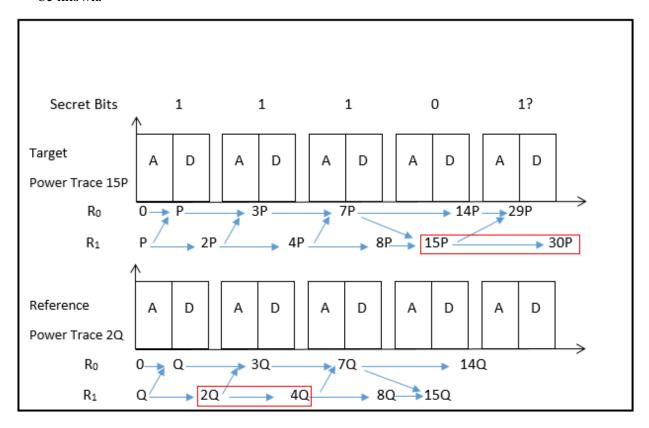

Similar to the relative doubling attack, the basic idea of comparative power analysis is also generating collisions by inputting a pair of carefully chosen message. More specifically, the chosen inputs are set to satisfy the equation  $\alpha P = \beta Q$ , where  $\alpha$  and  $\beta$  are integer. The input P is computed with the target operation  $\alpha P$  while the input Q is illustrates the reference power trace. When the collision happens, the doubling operation of the two input will have very similar power trace. By comparison of the power traces, the target secret key bit is leaked. Unlike doubling attack, the collision can be retrieved from different time frames.

Figure 4.2 shows an example how the attack scheme works. The input condition is chosen as 15P = 2Q. Consider the first four bits of the secret key is known to the attacker, the target bit is the fifth bit. The attacker then make an assumption that the target bit is 1, and illustrates the power traces. Then he examines the reference power traces at the time frame 2Q doubling is computing, if the power trace shares similarity with the target power trace at the time frame computing 15P doubling, the target secret bit is 1. The assumption made at the beginning is correct. If there is no similarity detected in the target and reference

power trace, the secret bit is 0. Note that the collision is generated at different timeframe of the two power traces. By repeating the attack pattern, all the bits of the secret key will be known.

Figure 4.2 Comparative power analysis against MPL

## 4.4.6 MPL based hardware implementation

Deschamps and G.Sutter implemented EC scalar multiplication over  $GF(2^{163})$  in 2008 [32]. This design is implemented using MPL algorithm. The computation time is 1ms at 100MHz and a comparison with binary algorithm implementation has been made. As stated previously, implementation on unprotected MPL is still vulnerable to some SCAs, thus an implementation on a more secure algorithm is proposed in the next chapter.

#### CHAPTER V

### ANALYSIS OF MODIFIED MPL WITH COUNTERMEASURES

In this chapter we introduce a modified MPL with sequence masking, exponent splitting and point randomization proposed in [11]. A small modification has been done to this algorithm to make it suitable for ECC scalar multiplication since it is originally invented for exponentiation operation.

## 5.1 Existing countermeasure techniques

In previous Chapters, it has been stated that unprotected MPL is still vulnerable to a lot of side channel attacks. To offer protections in algorithm level, He, Huang and Wu proposed a highly secure MPL for exponentiation operation [11]. Several countermeasures had been applied to enhance its security strength.

#### 5.1.1 Coron's three countermeasures to DPA

Coron has proposed three countermeasures against DPA to improve the original MPL [7]. The first is to randomize the secret private exponent. The main idea is to change the representation of the secret exponent. Denote # $\varepsilon$  as the number of all the points on the curve E, and select a random number k. Then the following computation is carried out to calculate  $d' = d + k\#\varepsilon$ , the computation Q = dP is replaced by Q = d'P. The correctness of this transform is based on the fact that  $\#\varepsilon P = 0$ . To expand this equation in detail, we get the following proof.

$$Q = d'P = (d + k. #\varepsilon)P = dP + k. #\varepsilon. P = dP + O = dP$$

The size of the random number k is suggested to be 20 for better security performance. By applying this countermeasure, the compute process is changed while the result Q still remains the same.

The second countermeasure is to blind the point P. Choose a random R on the same curve as point P. Point R is used as a mask to provide protection to the point P. Another point S is computed as S = dR. The cryptographic system then performs the scalar multiplication d(R+P). In order to retrieve Q = dP, a subtraction will be applied the previous result. Since S is already known, the final result will be recovered by d(R+P) - S. Point R and S will be updated in every initialization of the scalar multiplication.

The third countermeasure is to randomize to projective representation [33] of the point P(x,y). Point P can be represented in projective coordinates as (X,Y,Z). Since it is not the only projective representation point P has, it can be written as  $(\lambda X, \lambda Y, \lambda Z)$  where  $\lambda \neq 0$ . The binary representation of point P is then guarded. Since this thesis mainly focus on implementation in affine coordinates, this countermeasure will not be discussed in detail.

# 5.1.2 Exponent Splitting

Exponent Splitting technique is first proposed in [34]. While it is used in exponentiation is the paper, the idea is the same in scalar multiplication. The basic thought is based on the simple observation that

$$dP = (d-a)P + aP$$

In this splitting technique, the scalar d can be split into two parts as the above equation indicated. First a random number r is generated, where r is smaller than d. r' is then calculated by r' = d - r. The scalar multiplication then become

$$dP = rP + r'P$$

since d = r + r', it is obvious that the result is the same without scalar splitting.

Since we can see from the equation, the splitting technique is basically transforming a single scalar multiplication into two separate computations, thus it will be more time

consuming to put this technique into practice. Usually it takes two times the original time. But considering the security strength, sometimes the trade-off is worthy. This technique offers enhanced protection against SPA, and the randomization also helps to prevent some differential attacks.

## 5.1.3 Blinded Fault Resistant Exponentiation

This technique is first proposed by Fumaroli and Vigilant in [35]. It is an extension of Coron's second countermeasure [7]. The main idea is to add a mask to the base point P to construct a masked MPL. The algorithm is originally for exponentiation operation, but by a small modification, it can be also applied to scalar multiplication.

Algorithm 5.1. Masked Montgomery Powering Ladder

Input:  $P \in E, k = (k_{n-1}, ..., k_1, k_0)_2, k_i \in 0,1$

Output:  $Q = kP \in E$

Step 1: *Select random point R on E*;

Step 2:  $R_0 = R$ ,  $R_1 = P + R$ ,  $R_2 = -R$

Step 3: for i=n-1 down to 0 do

Step 4: if  $k_i = 0$ , then  $R_1 = R_0 + R_1$ ;  $R_0 = 2R_0$ ;  $R_2 = 2R_2$

Step 5: else if  $k_i = 1$ , then  $R_0 = R_0 + R_1$ ;  $R_1 = 2R_1$ ;  $R_2 = 2R_2$

Step 6: end if

Step 7: end for

Step 8:  $Return\ Q = R_0 + R_2$

In Algorithm 5.1, at the beginning of the operation, a random point R is picked. R is acting as a mask to the base point P. Three registers  $R_0$ ,  $R_1$ ,  $R_2$  are needed for the

algorithm.  $R_0$  is initialised with the mask R,  $R_1$  is initialised with P + R and  $R_2$  is given the anti-mask -R. The mask is updated at each iteration. The intimidate values in  $R_0$  and  $R_1$  are blinded with the updated mask  $2^{n-i}R$ . The anti-mask value is also updated at every iteration. The value in register  $R_2$  is following the pattern  $2^{n-i}(-R)$ . At the end of the computation, the final unmask step will be executed to recover the original desired result.

This algorithm can provide resistance to more attacks while still keeps the feature that regular MPL offers. Since the regular MPL is highly regular, the algorithm is insensitive to SPA. As the mask technique is applied in this algorithm, the intermediate values are independent from the input and output according to [35]. Thus the attacker cannot exploited the secret key by DPA. Moreover, since any fault injected during any time of the computation will cause the change of the temporary result. The adversary cannot retrieve valuable information regarding the secret key bit.

### 5.2 Security Analysis of Existing Countermeasure Techniques

Although the techniques introduced in previous section are great improvement to the strength of existing algorithms. They still face security challenge stand alone.

#### 5.2.1 High-Order Attack

The high-order attack is first proposed by Muller and Valette in [36]. This attack is specifically derived from the statistical property of the exponent splitting. Although r is a randomly selected number, the pair (r,r') is not uniformly distributed since they satisfy d = r + r'.

If the i-th bits of r,r' and d is denoted as  $r_i$ ,  $r_i'$  and  $d_i$ ,  $C_i$  representing the carry bit generated at the i-th iteration. The following equation is satisfied.

$$C_i \oplus r_i \oplus r_i' = d_i$$

Let  $P_i$  be the probability that the carry bit is zero, and  $P_r$  is set to be the probability the pair  $(r_i, r_i')$  be a certain value. In the case  $d_i = 0$  and  $C_i = 0$ , the probability for the pair  $(r_i, r_i')$  holds the value (0,0) or (1,1) is the same. When the value is (0,0), it is easy to get  $C_{i+1} = 0$ . On the contrary,  $C_{i+1} = 1$ . The same rules apply when  $d_i = 1$ . Table. 5.1 shows the transition of the probability. The probabilities of iteration i is generated from the previous iteration i - 1. It is a Markov chain.

Table 5.1 Probability transition when  $d_i = 0$  or 1

| $P_r(r_i, r_i')$ | $d_i = 0$              | $d_i = 1$              |

|------------------|------------------------|------------------------|

| $P_r(0,0)$       | $0.5 \times P_i$       | $0.5\times(1-P_i)$     |

| $P_r(0,1)$       | $0.5 \times (1 - P_i)$ | $0.5 \times P_i$       |

| $P_r(1,0)$       | $0.5 \times (1 - P_i)$ | $0.5 \times P_i$       |

| $P_r(1,1)$       | $0.5 \times P_i$       | $0.5 \times (1 - P_i)$ |

| $P_{i+1}$        | $0.5 \times P_i$       | $0.5 \times (1 + P_i)$ |

An example in [36] illustrates the idea of how this attack works. A secret d with length 24 bits is chosen and the probability distribution of the pair  $(r_i, r_i')$  is computed in Table.5.2. The table shows whenever the secret bit d has a long run of 0s or 1s, it is very likely the randomly generated pair  $(r_i, r_i')$  hold different value. Taking the probability transition illustrated in Table.5.1 into account, the probability of  $P_i$  can be calculated. In the case the secret bit is running long 0s (from  $d_7$  to  $d_{11}$  in the table),  $P_i$  is approaching 0

Table 5.2 An example of bit-level imbalance [36]

|               | $d_0$ | $d_1$ | $d_2$ | <br>$d_7$ | $d_8$ | $d_9$ | $d_{10}$ | $d_{11}$ | <br>$d_{18}$ | $d_{19}$ | $d_{20}$ | $d_{21}$ | $d_{22}$ | $d_{23}$ |

|---------------|-------|-------|-------|-----------|-------|-------|----------|----------|--------------|----------|----------|----------|----------|----------|

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

| $(r_i, r_i')$ | 0     | 1     | 0     | <br>0     | 0     | 0     | 0        | 0        | <br>0        | 1        | 1        | 1        | 1        | 1        |

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

| $P_r(0,0)$    | 50    | 25    | 38    | <br>16    | 8     | 4     | 2        | 1        | <br>8        | 47       | 23       | 11       | 5        | 2        |

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

| $P_r(1,0)$    | 0     | 25    | 12    | <br>34    | 41    | 46    | 48       | 49       | <br>42       | 3        | 27       | 39       | 45       | 48       |

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

| $P_r(0,1)$    | 0     | 25    | 13    | <br>33    | 42    | 46    | 49       | 49       | <br>43       | 4        | 28       | 40       | 46       | 49       |

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

| $P_r(1,1)$    | 50    | 25    | 37    | <br>17    | 9     | 4     | 1        | 1        | <br>7        | 46       | 22       | 10       | 4        | 1        |

|               |       |       |       |           |       |       |          |          |              |          |          |          |          |          |

indicating that there is no carry bit generated. While in the case of continuous 1s (from  $d_{19}$  to  $d_{23}$  in the table),  $P_i$  gets very close to 1, shows that the carry bit is propagating as the computation runs. If the attacker can launch an attack revealing the probabilities of the pair  $(r_i, r_i')$ , he can proceed to find information regarding the secret bit. The secret bit will no longer be secret.

#### 5.2.2 Template Attack

Template attack [37] is based on the fact that power consumptions can be characterized by a multivariate normal distribution during the computations. Normally, it can be executed in two steps. The first step is to setup the templates and the second step is using the template to initialise attacks.

The multivariate normal distribution is defined by a covariance matrix C and a mean vector m. Where C holds the covariance of the targeting point and m is the mean of all the point on the trace. The pair (m, C) is called the template. By sending in different data and key bit, a group of power trace is generated by the adversary. Until then, every data and key pair leads to a template. Then as stated above, in the second step, the attacker

compares the power trace from the target device with all the templates, and determine which one has the highest probability to be the correct template. After the correct template is recovered, the key is then retrieved.

Since in ECC scalar multiplication, the base point P is fixed. This observation offers template attack a great opportunity. In [38], Herbst and Medwed proposed a template attack scheme against masked MPL. In the scenario of scalar multiplication, the attacker set up the templates by running the scalar multiplication several times using different input data. The hamming weight of some intimidate values are also correlated. The power trace is then obtained to match with the template. In order to simplify the matching process, the first two multiplication of the base point are usually taken out to do the match. The template with highest matching probability indicates the first bit. The mask technique only blinds the point, but still by means of template attack, partial bits of secret k is recovered. The attacker can then focus on the masking operation to determine the mask R. Since the hamming weight is known by the matching process. The mask R will not be safe.

### 5.3 Modified MPL with SM, ES and PR

Since all the countermeasures listed in previous section is vulnerable to different attacks stand alone. He, Huang and Wu burrowed some of the ideas mentioned before and combined them to create a more secure algorithm [11].

## 5.3.1 Algorithm Explanation

The new algorithm is illustrated as algorithm 5.2. The new algorithm is a combination of three ideas. The sequence masking technique [11], exponent splitting [34] and randomization of the message [35]. The combination of these three techniques greatly improved the security strength of the MPL. Further protections are provided to the

vulnerabilities stated in previous sections.

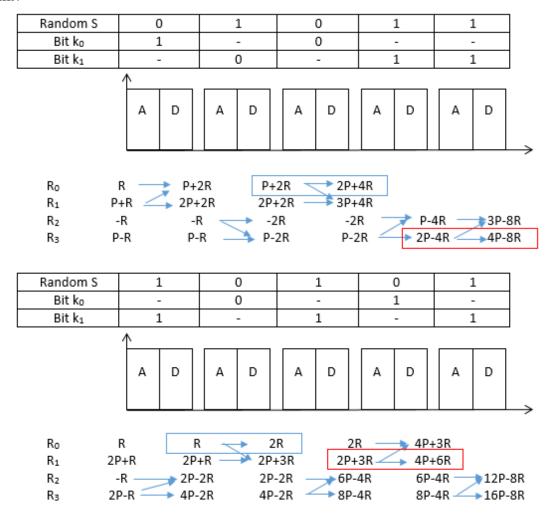

This algorithm works as follows, in the pre-computation phase, a random number  $k_0$  smaller than secret bit k is generated. The secret bit k is divided into two parts, the first part is the random number  $k_0$ , the second part is calculated as  $k_1 = k - k_0$ . After that a random point R on the same curve with point P is generated. The point R is acting as a mask, it is initialized to all the registers and the value is updated in each iteration. Another random number S with the same bit size of secret key k is generated afterwards. The introduction of random number S is acting as a switch, it determines which computation to be executed. The original scalar multiplication is computed following each bit of k sequentially. With the random number S, it turns into a randomly computed process.

Moving to the main iteration part of the algorithm, registers  $R_0$  and  $R_1$  holds the values related to the secret bit  $k_0$ . While  $R_2$  and  $R_3$  store the values computed using  $k_1$ . As introduced above, two scalar multiplications take turns to compute according to the current bit of S. When the main iteration part is finished, a final adjustment adding the values in  $R_0$  and  $R_2$  is carried out to get the desired output.

The following observations proved the correctness of the algorithm easily. Let i denotes the iteration number, the mask is updated following a pattern  $2^iR$ . The first scalar multiplication generates the intermediate value  $2^iR + k_0P$ , the second scalar multiplication holds that  $2^i(-R) + (k - k_0)P$ . Adding them up, we get the value of kP.

# Algorithm 5.2. Modified MPL with SM, ES and PR

Input:

$$P \in E$$

,  $k = (k_{n-1}, ..., k_1, k_0)_2$ ,  $k_i \in 0,1$

Output:  $Q = kP \in E$

Step 1: Select random point R on E;

Step 2: Select random number  $k_0 = (k_{n-1}^{(0)} ... k_0^{(0)})_2$  that  $k_0 \in (1, k)$

let

$$k_1 (k_{n-1}^{(1)} ... k_0^{(1)})_2 = k - k_0$$

;

$k_0$  and  $k_1$  are stored in shift registers

$$D_0 = (d_{n-1}^{(0)} \dots d_0^{(0)})_2$$

and  $D_1 = (d_{n-1}^{(1)} \dots d_0^{(1)})_2$

Step 3: Genarate n bit sequence  $S = (s_{n-1}, ..., s_1, s_0)_2$

Step 4: Set

$$R_0 = R$$

,  $R_1 = P + R$ ,  $R_2 = -R$ ,  $R_2 = P + (-R)$

Step 5: for i=n-1 down to 0 do

Step 6:  $if s_i = 0$ , then

Step 7: if

$$d_{n-1}^{(0)} = 0$$

, then  $R_1 = R_0 + R_1$ ;  $R_0 = 2R_0$ ;

Step 8:

$$else\ R_0 = R_0 + R_1$$

;  $R_1 = 2R_1$ ;

Step 9: end if;  $D_0$  shifts left by 1 bit.

Step 10: else if

$$d_{n-1}^{(1)} = 0$$

, then  $R_3 = R_2 + R_3$ ;  $R_2 = 2R_2$ ;

Step 11:

$$else R_2 = R_2 + R_3; R_3 = 2R_3;$$

Step 12: end if;  $D_1$  shifts left by 1 bit.

Step 13: end if

Step 14: end for

Step 15: for i = n - 1 down to 0 do

Step 16:  $if s_i = 1$ , then

Step 17: if

$$d_{n-1}^{(0)} = 0$$

, then  $R_1 = R_0 + R_1$ ;  $R_0 = 2R_0$ ;

Step 18:

$$else\ R_0 = R_0 + R_1;\ R_1 = 2R_1;$$

Step 19: end if;  $D_0$  shifts left by 1 bit.

Step 20: else if

$$d_{n-1}^{(1)} = 0$$

, then  $R_3 = R_2 + R_3$ ;  $R_2 = 2R_2$ ;

Step 21:  $else R_2 = R_2 + R_3; R_3 = 2R_3;$

Step 22: end if;  $D_1$  shifts left by 1 bit.

Step 23: end if

Step 24: end for

Step 25:  $Return R_0 = R_0 + R_2$

5.3.2 Security Analysis

As mentioned in previous sections, this algorithm provides enhanced protection to

more attacks compared to existing algorithms.

Since algorithm 5.2 still holds the high regularity MPL offers, SPA is not effective

against it. The main computation part always compute a doubling and an addition

regardless the input bit. This it keeps all the resistance the regular MPL can provide. C-safe

error attack is also eliminated because there is no dummy operation in this modified MPL.

Taking M-safe error into account. In M-safe error attack scheme, the induced

memory fault need to be very carefully timed to determine whether it changed the result.

Even if the attacker reveals a secret bit by a successfully inducing a safe error, the whole

key pattern is not compromised since the key is divided into two parts. Moreover, the

computation is executed in a random order. Thus M-safe error cannot threat the modified

MPL.

Another attack mentioned above is the comparative power analysis, it also has little

effect on the modified MPL with SM, ES and PR. This attack scheme is very similar to the

relative doubling attack. Both the two attacks are trying to get two power traces and by

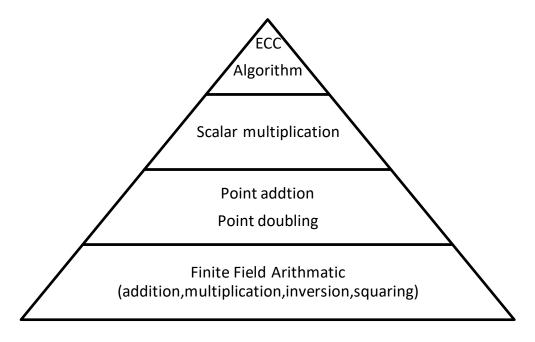

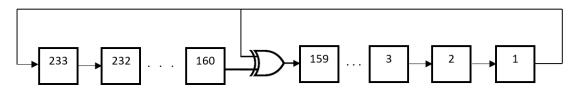

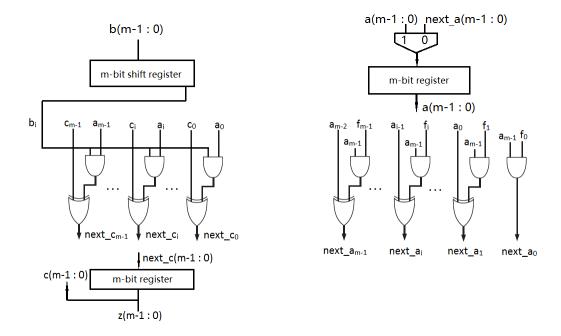

comparing them to get valuable information of the secret key. Since the secret key is