### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2009

### High speed world level finite field multipliers in F2m

Ashkan Hosseinzadeh Namin University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Namin, Ashkan Hosseinzadeh, "High speed world level finite field multipliers in F2m" (2009). *Electronic Theses and Dissertations*. 7899.

https://scholar.uwindsor.ca/etd/7899

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### High Speed World Level Finite Field Multipliers in $\mathbb{F}_{2^m}$

by

### Ashkan Hosseinzadeh Namin

A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario, Canada 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-57643-4 Our file Notre référence ISBN: 978-0-494-57643-4

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

# Canada

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant. © 2009 Ashkan Hosseinzadeh Namin

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

### **Declaration of Co-Authorship**

I hereby declare that this thesis incorporates material that is the result of joint research as follows:

This thesis incorporates the outcome of joint research undertaken in collaboration with Karl Leboeuf under the supervision of Dr. Roberto Muscedere. The collaboration contributions are outlined in Chapter 8. The personal contributions, design work and development performed by the author are the focus of this chapter.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contributions of other researchers to my thesis, and have obtained written permission from the co-authors to include the above materials in my thesis.

I certify that with the above qualification, this thesis, and the research to which it refers is the product of my own work.

### Abstract

Finite fields have important applications in number theory, algebraic geometry, Galois theory, cryptography, and coding theory. Recently, the use of finite field arithmetic in the area of cryptography has increasingly gained importance. Elliptic curve and El-Gamal cryptosystems are two important examples of public key cryptosystems widely used today based on finite field arithmetic. Research in this area is moving toward finding new architectures to implement the arithmetic operations more efficiently.

Two types of finite fields are commonly used in practice, prime field GF(p) and the binary extension field  $GF(2^m)$ . The binary extension fields are attractive for high speed cryptography applications since they are suitable for hardware implementations. Hardware implementation of finite field multipliers can usually be categorized into three categories: bit-serial, bit-parallel, and word-level architectures. The word-level multipliers provide architectural flexibility and trade-off between the performance and limitations of VLSI implementation and I/O ports, thus it is of more practical significance.

In this work, different word level architectures for multiplication using binary field are proposed. It has been shown that the proposed architectures are more efficient compared to similar proposals considering area/delay complexities as a measure of performance. Practical size multipliers for cryptography applications have been realized in hardware using FPGA or standard CMOS technology. to similar proposals considering area/delay complexities as a measure of performance. Practical size multipliers for cryptography applications have been realized in hardware using FPGA or standard CMOS technology. Also different VLSI implementations for multipliers were explored which resulted in more efficient implementations for some of the regular architectures. The new implementations use a simple module designed in domino logic as the main building block for the multiplier. Significant speed improvements was achieved designing practical size multipliers using the proposed methodology. To my family, with love ...

### **Acknowledgments**

There are several people who deserve my sincere thanks for their generous contributions to this project. I would first like to express my sincere gratitude and appreciation to Dr. Huapeng Wu and Dr. Majid Ahmadi, my supervisors for their invaluable guidance and constant support throughout the course of this thesis work.

In addition to my advisors, I would like to thank the rest of my thesis committee: Dr. Roberto Muscedere and Dr. Esam Abdel-Raheem from the electrical and computer engineering department, Dr. Arunita Jaekel from the school of computer science and Dr. Gerald E. Sobelman from the University of Minnesota for their participation in my seminars, reviewing my thesis, and their constructive comments.

I also like to thank Dr. Roberto Muscedere and Till Kuendiger for their assistants regarding the VLSI CAD tools and facilities used during the course of the project. I am thankful to my research colleagues in the RCIM lab of the University of Windsor and my friends whom have supported and believed in me: Golnar Khodabandehloo, Mitra Mirhassani, Mahzad Azarmehr, Andrew Tam, Kevin Biswas and Matthew Meloche. A Special thanks goes to Karl Leboeuf, for proofreading this thesis.

Finally, my deepest gratitude goes to my family for their unconditional love, support and encouragement.

### Contents

| De | eclara  | tion of Co-Authorship                                       | iv   |

|----|---------|-------------------------------------------------------------|------|

| Ał | ostrac  | et                                                          | v    |

| De | edicat  | ion                                                         | vii  |

| Ac | know    | vledgments                                                  | viii |

| Li | st of I | Figures                                                     | XV   |

| Li | st of ] | Tables                                                      | xvii |

| Li | st of A | Abbreviations                                               | xix  |

| 1  | Intr    | oduction                                                    | 1    |

|    | 1.1     | Summary of Contributions                                    | 3    |

|    | 1.2     | Outline of the Thesis                                       | 4    |

| 2  | Mat     | hematical Preliminaries                                     | 7    |

|    | 2.1     | Groups, Rings and Fields                                    | 7    |

|    | 2.2     | Binary Field and Bases                                      | 9    |

|    |         | 2.2.1 Normal Basis and Its Arithmetic in $\mathbb{F}_{2^m}$ | 10   |

|    |         | 2.2.1.1 Normal Basis Representation                         | 10   |

|   |      |          | 2.2.1.2     | Normal basis multiplication                             | 10 |

|---|------|----------|-------------|---------------------------------------------------------|----|

|   |      | 2.2.2    | Redunda     | nt Basis and its Arithmetic in $\mathbb{F}_{2^m}$       | 12 |

|   |      |          | 2.2.2.1     | Redundant Representation                                | 12 |

|   |      |          | 2.2.2.2     | Redundant Basis Multiplication                          | 13 |

|   |      |          | 2.2.2.3     | Redundant Basis and Normal Basis                        | 14 |

| 3 | Con  | ıb Arch  | itectures f | for Finite Field Multiplication in $\mathbb{F}_2^m$     | 15 |

|   | 3.1  | Introdu  | uction      |                                                         | 15 |

|   | 3.2  | Prelim   | inaries on  | Finite Field Bases and Arithmetic in $\mathbb{F}_{2^m}$ | 17 |

|   |      | 3.2.1    | Redunda     | nt Representation and Multiplication                    | 17 |

|   |      | 3.2.2    | Reordere    | d Normal Basis Representation and Multiplication        | 18 |

|   | 3.3  | Propos   | ed Hybrid   | Multiplier Using Redundant Representation               | 19 |

|   |      | 3.3.1    | Bit-serial  | word-parallel multiplication algorithm                  | 19 |

|   |      | 3.3.2    | Comb sty    | le multiplication architecture                          | 21 |

|   |      | 3.3.3    | Architect   | cure complexities and comparison                        | 23 |

|   | 3.4  | Propos   | ed Hybrid   | Multiplier Using Reordered Normal Basis                 | 24 |

|   |      | 3.4.1    | Bit-serial  | word-parallel multiplication algorithm                  | 24 |

|   |      | 3.4.2    | Bit-serial  | word-parallel multiplier architecture                   | 25 |

|   |      | 3.4.3    | Architect   | ure complexities and comparison                         | 27 |

|   | 3.5  | FPGA     | Implemen    | tations                                                 | 29 |

|   | 3.6  | Conclu   | isions      |                                                         | 30 |

| 4 | A No | ew Finit | te Field M  | ultiplier Using Redundant Representation                | 31 |

|   | 4.1  | Introdu  | iction      |                                                         | 31 |

|   | 4.2  | Prelim   | inaries .   |                                                         | 32 |

|   |      | 4.2.1    | Redunda     | nt Representation                                       | 32 |

|   |      | 4.2.2    | Redunda     | nt Basis Multiplication                                 | 33 |

|   |      | 4.2.3    | An Over     | view of Bit-Serial RB Multipliers                       | 33 |

|   |      |          |             |                                                         |    |

|   | 4.3                                           | Propos                                                                                   | ed SIPO Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                             |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 4.3.1                                                                                    | A New Bit-Serial RB Multiplication Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                                             |

|   |                                               | 4.3.2                                                                                    | Multiplier Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                             |

|   | 4.4                                           | Compl                                                                                    | exity Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                                                                                             |

|   |                                               | 4.4.1                                                                                    | Comparison to Other RB Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                             |

|   |                                               | 4.4.2                                                                                    | Comparison to Normal Basis Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                                                             |

|   | 4.5                                           | Propos                                                                                   | ed Digit-Level SIPO Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                                                                                             |

|   |                                               | 4.5.1                                                                                    | A New Digit-Level RB Multiplication Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                             |

|   |                                               | 4.5.2                                                                                    | Proposed Digit-Level RB Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                                                                                             |

|   |                                               | 4.5.3                                                                                    | Complexity Comparison to Previous RB Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                                                             |

|   |                                               | 4.5.4                                                                                    | Complexity Comparison to Previous NB Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                                                             |

|   | 4.6                                           | Conclu                                                                                   | sions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                                                             |

| _ |                                               |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                                             |

| 5 | AH                                            | ign Spe                                                                                  | ed Word Level Multiplier in $\mathbb{F}_{2^m}$ Using Redundant Representation                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43                                                                                                                                             |

|   | ~ 1                                           | <b>T</b> . 1                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                                                             |

|   | 5.1                                           |                                                                                          | letion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                                                                                                                                             |

|   | 5.1<br>5.2                                    | A Brie                                                                                   | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                                                                                             |

|   |                                               |                                                                                          | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .<br>Redundant Basis for $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>44                                                                                                                                       |

|   |                                               | A Brie                                                                                   | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                                                                                             |

|   |                                               | A Brie<br>5.2.1<br>5.2.2                                                                 | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .<br>Redundant Basis for $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>44                                                                                                                                       |

|   | 5.2                                           | A Brie<br>5.2.1<br>5.2.2<br>Propos                                                       | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .<br>Redundant Basis for $\mathbb{F}_{2^m}$<br>Redundant Basis Multiplication in $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                     | 44<br>44<br>45                                                                                                                                 |

|   | 5.2<br>5.3                                    | A Brie<br>5.2.1<br>5.2.2<br>Propos                                                       | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .<br>Redundant Basis for $\mathbb{F}_{2^m}$<br>Redundant Basis Multiplication in $\mathbb{F}_{2^m}$                                                                                                                                                                                                                                                                                                                                     | 44<br>44<br>45<br>46                                                                                                                           |

|   | 5.2<br>5.3                                    | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>Propos                                             | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ Redundant Basis for $\mathbb{F}_{2^m}$ Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ ed Word Level Multiplication In RBed Word Level Multiplier Architecture in RB                                                                                                                                                                                                                                                               | 44<br>45<br>46<br>47                                                                                                                           |

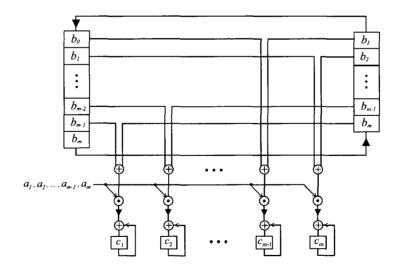

|   | 5.2<br>5.3                                    | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2                                     | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ Redundant Basis for $\mathbb{F}_{2^m}$ Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ Word Level Multiplication In RBRedundant Level Multiplier Architecture in RBMultiplier Architecture                                                                                                                                                                                                                                         | 44<br>45<br>46<br>47<br>47                                                                                                                     |

|   | 5.2<br>5.3                                    | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2                                     | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .         Redundant Basis for $\mathbb{F}_{2^m}$ .         Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ .         ed Word Level Multiplication In RB       .         ed Word Level Multiplier Architecture in RB       .         Multiplier Architecture       .         Architecture Complexities       .                                                                                                                      | 44<br>45<br>46<br>47<br>47<br>50                                                                                                               |

|   | 5.2<br>5.3                                    | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4                   | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .         Redundant Basis for $\mathbb{F}_{2^m}$ .         Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ .         ed Word Level Multiplication In RB       .         ed Word Level Multiplier Architecture in RB       .         Multiplier Architecture       .         Architecture Complexities       .         An example       .                                                                                           | 44<br>45<br>46<br>47<br>47<br>50<br>51                                                                                                         |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul> | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4                   | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .         Redundant Basis for $\mathbb{F}_{2^m}$ .         Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ .         ed Word Level Multiplication In RB       .         ed Word Level Multiplier Architecture in RB       .         Multiplier Architecture       .         Architecture Complexities       .         An example       .         Word Level Architecture with MSB First       .                                    | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>47</li> <li>47</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> </ul>             |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul> | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>Compl          | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .         Redundant Basis for $\mathbb{F}_{2^m}$ .         Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ .         ed Word Level Multiplication In RB       .         ed Word Level Multiplier Architecture in RB       .         Multiplier Architecture       .         Architecture Complexities       .         Word Level Architecture with MSB First       .         word Level Architecture       .                       | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>47</li> <li>47</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> </ul>             |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul> | A Brie<br>5.2.1<br>5.2.2<br>Propos<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>Compl<br>5.5.1 | f Review of Redundant Representation and Its Arithmetic in $\mathbb{F}_{2^m}$ .         Redundant Basis for $\mathbb{F}_{2^m}$ .         Redundant Basis Multiplication in $\mathbb{F}_{2^m}$ .         ed Word Level Multiplication In RB       .         ed Word Level Multiplier Architecture in RB       .         Multiplier Architecture       .         Architecture Complexities       .         Word Level Architecture with MSB First       .         Comparison to Other Word Level RB Multipliers       . | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>47</li> <li>47</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>53</li> </ul> |

|   | 5.6   | Conclu  | sions                                                                     | 57 |

|---|-------|---------|---------------------------------------------------------------------------|----|

| 6 | High  | Speed   | Word Level Multipliers in $\mathbf{GF}(2^m)$ Using Reordered Normal Basis | 58 |

|   | 6.1   | Introdu | ction                                                                     | 58 |

|   | 6.2   | A Brief | f Review of Reordered Normal Basis and Its Arithmetic in $GF(2^m)$ .      | 59 |

|   |       | 6.2.1   | Reordered Normal Basis                                                    | 59 |

|   |       | 6.2.2   | Reordered Normal Basis Multiplication                                     | 61 |

|   | 6.3   | Propos  | ed High Speed Word Level Multiplier Type One Using Reordered              |    |

|   |       | Norma   | l Basis                                                                   | 62 |

|   |       | 6.3.1   | Word-level multiplication algorithm using reordered normal basis .        | 62 |

|   |       | 6.3.2   | Multiplier Architecture                                                   | 64 |

|   |       | 6.3.3   | Architecture complexities                                                 | 69 |

|   |       | 6.3.4   | An example                                                                | 69 |

|   | 6.4   | Propos  | ed High Speed Word Level Multiplier Type Two Using Reordered              |    |

|   |       | Norma   | l Basis                                                                   | 70 |

|   |       | 6.4.1   | Word-level multiplication algorithm using reordered normal basis .        | 70 |

|   |       | 6.4.2   | Multiplier architecture                                                   | 72 |

|   |       | 6.4.3   | Architecture complexity                                                   | 73 |

|   |       | 6.4.4   | An example                                                                | 75 |

|   | 6.5   | Compa   | risons                                                                    | 75 |

|   | 6.6   | Conclu  | sions                                                                     | 79 |

| 7 | High  | Speed   | VLSI Implementation of a Multiplier Using Redundant Represen-             |    |

|   | tatio | n       |                                                                           | 80 |

|   | 7.1   | Introdu | ection                                                                    | 80 |

|   | 7.2   | A Brief | f Review of Redundant Basis and its Arithmetic in $\mathbb{F}_{2^m}$      | 82 |

|   |       | 7.2.1   | Redundant Basis for $\mathbb{F}_{2^m}$                                    | 82 |

|   |       | 7.2.2   | Redundant Basis Multiplication in $\mathbb{F}_{2^m}$                      | 83 |

|   |       |         |                                                                           |    |

|   |      | 7.2.3    | Redundant Basis and Normal Basis                                            | 84  |

|---|------|----------|-----------------------------------------------------------------------------|-----|

|   |      | 7.2.4    | Multiplier Architecture in Redundant Basis                                  | 85  |

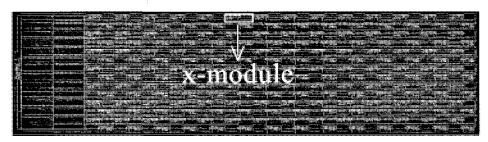

|   | 7.3  | Desig    | n of the Multiplier Main Building Block (x-module)                          | 86  |

|   | 7.4  | Desigr   | n of a Practical Size Multiplier Using the x-module                         | 88  |

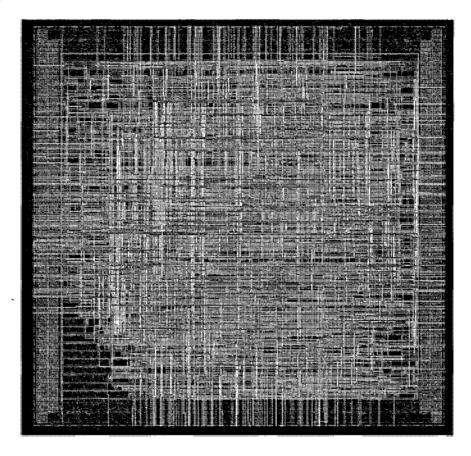

|   | 7.5  | Desigr   | n of Practical Size Multiplier Using static CMOS                            | 89  |

|   | 7.6  | Differe  | ent VLSI implementation Comparisons                                         | 90  |

|   | 7.7  | Conclu   | usions                                                                      | 91  |

| 8 | Higl | n Speed  | Implementation of a SIPO Multiplier Using Reordered Normal                  |     |

|   | Basi | S        |                                                                             | 92  |

|   | 8.1  | Introdu  | uction                                                                      | 92  |

|   | 8.2  | A Brie   | f Review of Reordered Normal Basis and Its Arithmetic in $\mathbb{F}_{2^m}$ | 94  |

|   |      | 8.2.1    | Reordered Normal Basis Definition                                           | 94  |

|   |      | 8.2.2    | Reordered Normal Basis Multiplication                                       | 94  |

|   |      | 8.2.3    | A Review of Existing Architectures for ONB Type II Multiplication           | 95  |

|   | 8.3  | Desigr   | n of A Practical Size Multiplier Using xax-module                           | 97  |

|   |      | 8.3.1    | Multiplier Size Selection                                                   | 97  |

|   |      | 8.3.2    | Selected Multiplier Architecture                                            | 97  |

|   |      | 8.3.3    | Design and Implementation of the xax-module                                 | 98  |

|   |      | 8.3.4    | Design and Implementation of the 233-bit Multiplier Using the               |     |

|   |      |          | xax-module                                                                  | 100 |

|   | 8.4  | Desigr   | n of the 233-bit Multiplier Using Static CMOS                               | 104 |

|   | 8.5  |          | nparison of Different VLSI Implementations                                  |     |

|   | 8.6  | Conclu   | isions                                                                      | 106 |

| 9 | Con  | clusions | s and Future Work                                                           | 108 |

|   | 9.1  | Conclu   | usions                                                                      | 108 |

|   | 9.2  | Future   | Work                                                                        | 110 |

| References    | 111 |

|---------------|-----|

| VITA AUCTORIS | 115 |

# **List of Figures**

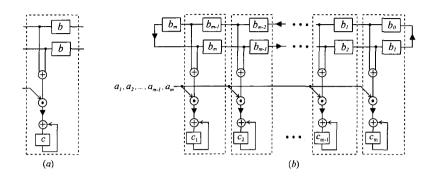

| 3.1                                           | Words vs. comb style inputs                                                                                          | 20                   |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|

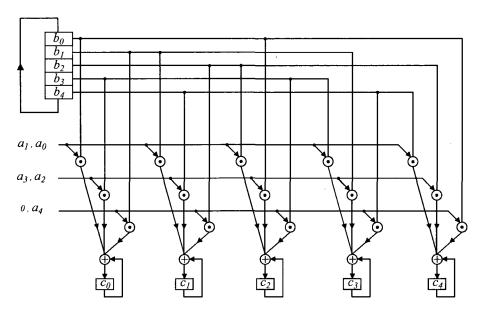

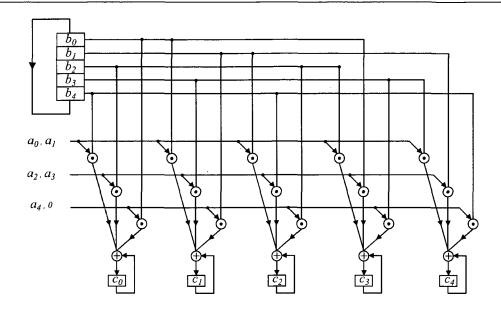

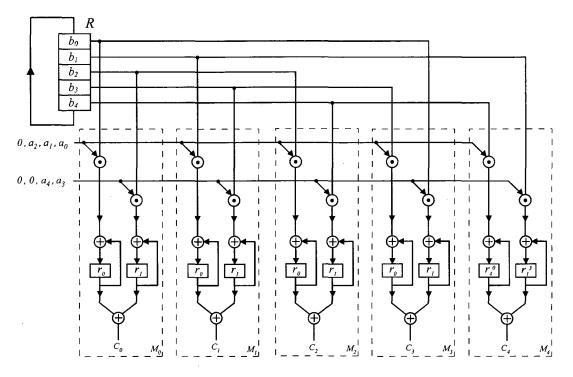

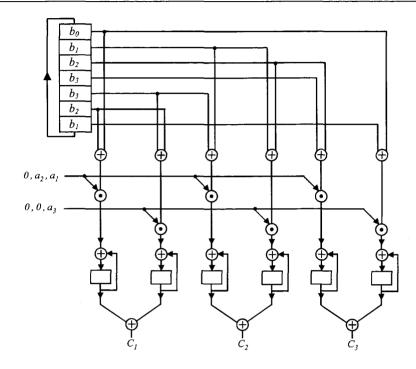

| 3.2                                           | Proposed comb style redundant basis multiplier for $\mathbb{F}_{2^4}$ (LSB first) $\ . \ . \ .$                      | 22                   |

| 3.3                                           | Proposed comb style redundant basis multiplier for $\mathbb{F}_{2^4}$ (MSB first)                                    | 23                   |

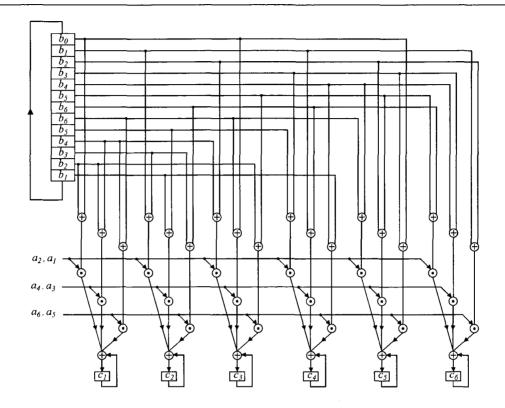

| 3.4                                           | Proposed comb style multiplier in $\mathbb{F}_{2^6}$ using reordered normal basis (LSB                               |                      |

|                                               | first)                                                                                                               | 26                   |

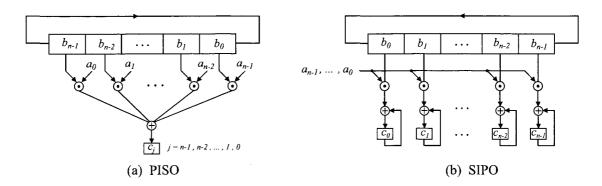

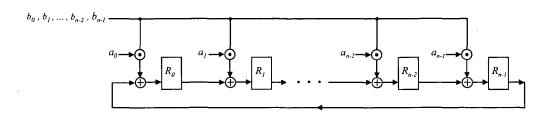

| 4.1                                           | Previously proposed bit-serial RB multipliers                                                                        | 34                   |

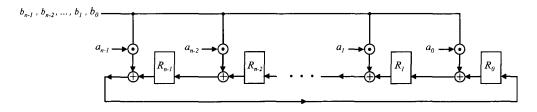

| 4.2                                           | Proposed serial-in parallel-out RB multiplier (MSB first)                                                            | 36                   |

| 4.3                                           | Proposed serial-in parallel-out RB multiplier (LSB first)                                                            | 36                   |

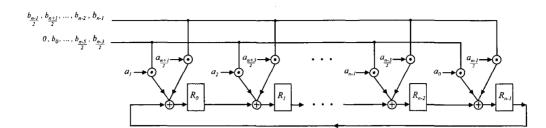

| 4.4                                           | Proposed hybrid SIPO RB multiplier (LSB first)                                                                       | 41                   |

|                                               |                                                                                                                      |                      |

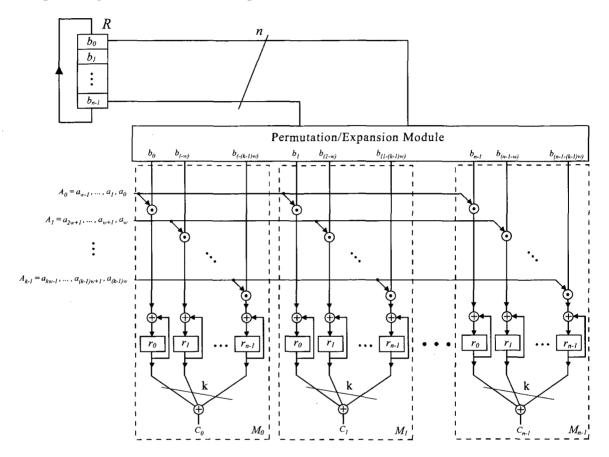

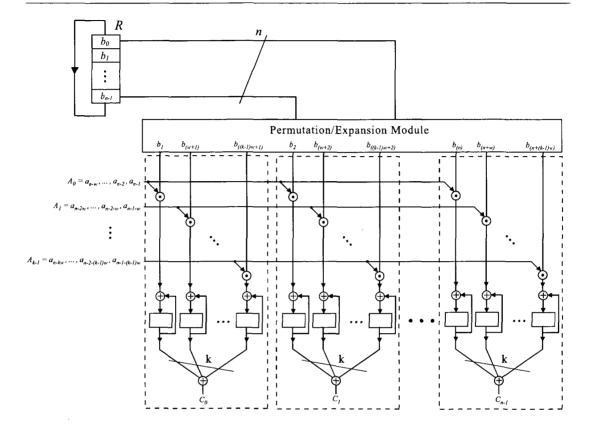

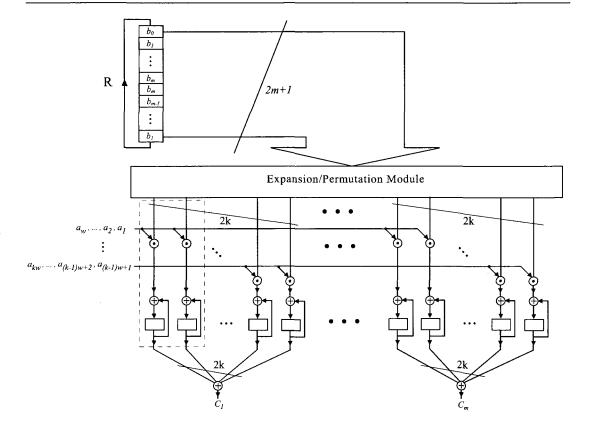

| 5.1                                           | Proposed high speed word level multiplier                                                                            | 48                   |

| 5.1<br>5.2                                    | Proposed high speed word level multiplier                                                                            | 48                   |

|                                               |                                                                                                                      |                      |

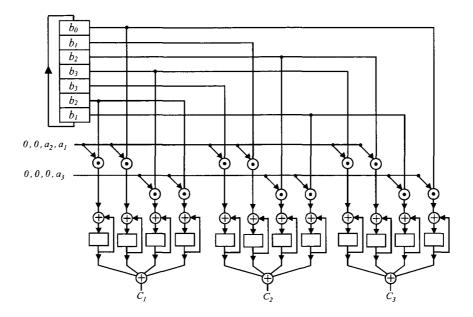

|                                               | Word level ( $w = 3$ ) multiplier in $\mathbb{F}_{2^4}$ with the padded zero bits for the input                      | 51                   |

| 5.2                                           | Word level ( $w = 3$ ) multiplier in $\mathbb{F}_{2^4}$ with the padded zero bits for the input (the second option)  | 51<br>54             |

| 5.2<br>5.3                                    | Word level $(w = 3)$ multiplier in $\mathbb{F}_{2^4}$ with the padded zero bits for the input<br>(the second option) | 51<br>54             |

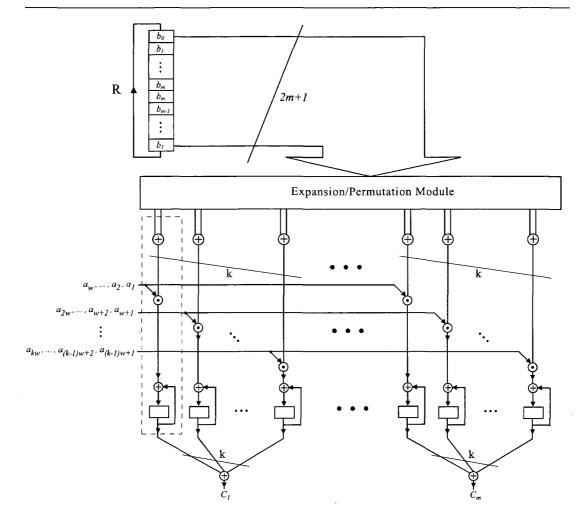

| <ul><li>5.2</li><li>5.3</li><li>6.1</li></ul> | Word level $(w = 3)$ multiplier in $\mathbb{F}_{2^4}$ with the padded zero bits for the input<br>(the second option) | 51<br>54<br>65       |

| <ul><li>5.2</li><li>5.3</li><li>6.1</li></ul> | Word level $(w = 3)$ multiplier in $\mathbb{F}_{2^4}$ with the padded zero bits for the input<br>(the second option) | 51<br>54<br>65<br>66 |

#### LIST OF FIGURES

| 6.5 | Architecture of WLM-RNB-II in $GF(2^3)$ with $w = k = 2$                 |

|-----|--------------------------------------------------------------------------|

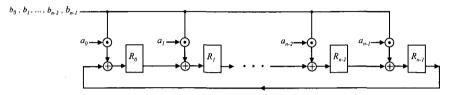

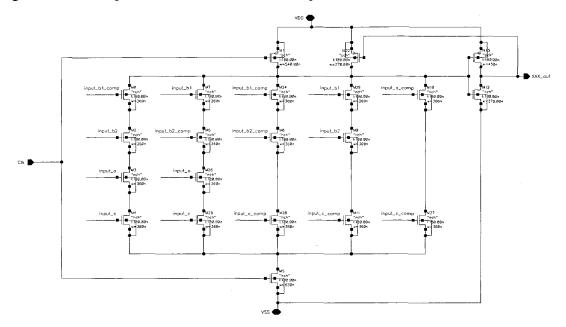

| 7.1 | High Speed Serial Multiplier in Redundant Basis                          |

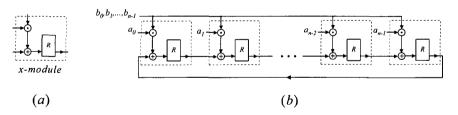

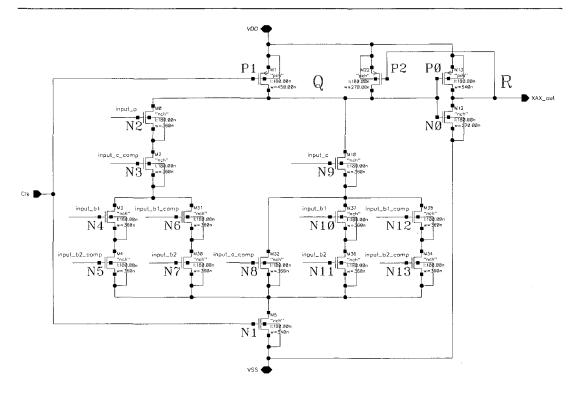

| 7.2 | (a) x-module Block Detail (b) Multiplier Composed of x-module Blocks 85  |

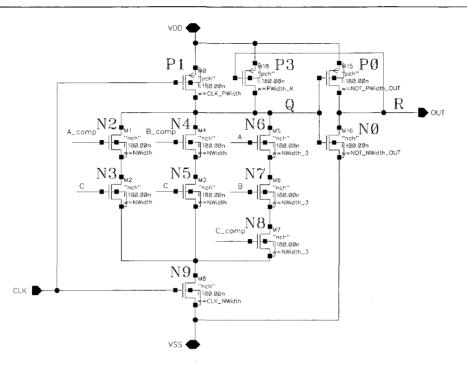

| 7.3 | AND - XOR Function in Domino Logic                                       |

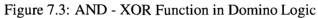

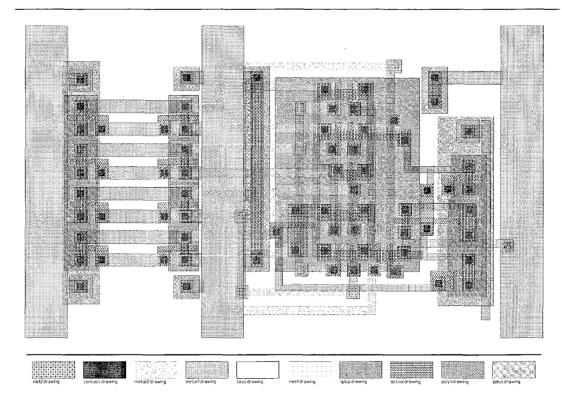

| 7.4 | Layout for the AND-XOR Function in Domino Logic                          |

| 7.5 | Proposed 197 Bit Multiplier Layout                                       |

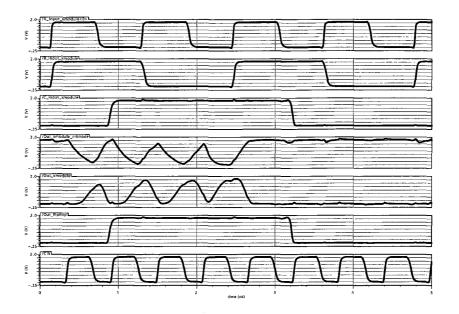

| 7.6 | Post Place-and-Route Simulation Result of the Proposed 197 Bit Multi-    |

|     | plier, from top to bottom: input A, input B, input C, node Q, node R, x- |

|     | module out, clock                                                        |

| 7.7 | Static CMOS 197 Bit Multiplier Layout                                    |

| 8.1 | Serial-In Parallel-Out Reordered Normal Basis Multiplier                 |

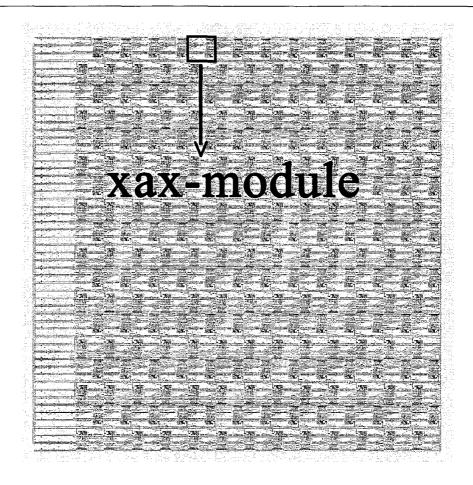

| 8.2 | xax-module and the SIPO Multiplier Composed of xax-module                |

| 8.3 | XOR-AND-XOR Function Implementation in Domino Logic 99                   |

| 8.4 | A New XOR-AND-XOR Function Implementation in Domino Logic 100            |

| 8.5 | Layout for the XOR-AND-XOR Function in Domino Logic                      |

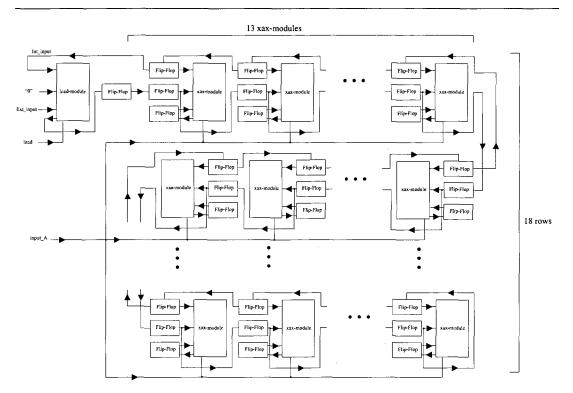

| 8.6 | Block Diagram of the 233-bit Multiplier                                  |

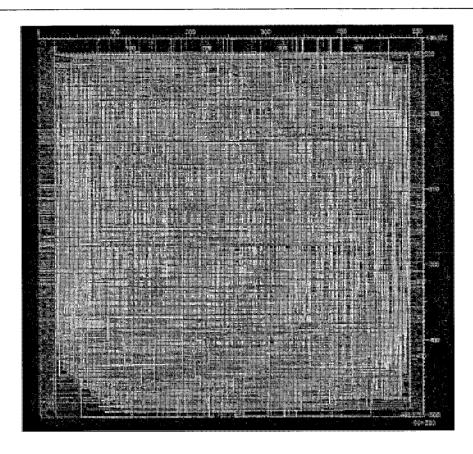

| 8.7 | 233-bit Proposed Multiplier Layout                                       |

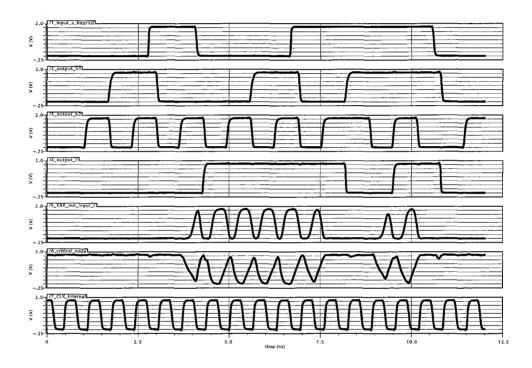

| 8.8 | Post Place-and-Route Simulation Result of the Proposed 233-bit Multi-    |

|     | plier, from top to bottom: input a, input b1, input b2, input c, node R, |

|     | node Q, clock                                                            |

| 8.9 | Static CMOS 233-bit Multiplier Layout                                    |

### **List of Tables**

| 3.1 | Complexities comparison between hybrid redundant basis multipliers                                       | 23 |

|-----|----------------------------------------------------------------------------------------------------------|----|

| 3.2 | Complexity comparison of hybrid multipliers using reordered normal basis                                 |    |

|     | or normal basis                                                                                          | 27 |

| 3.3 | Comparison of FPGA implementations of hybrid redundant basis multipliers                                 | 29 |

| 3.4 | FPGA implementation results for hybrid reordered normal basis multipliers                                | 30 |

| 4.1 | Register contents $c_j^{(k)}$ during a multiplication operation $\ldots \ldots \ldots$                   | 36 |

| 4.2 | Complexities comparison between bit-serial RB multipliers                                                | 37 |

| 4.3 | Complexities comparison between the proposed RB multiplier and bit-                                      |    |

|     | serial NB multipliers when there exists a type I optimal normal basis                                    | 38 |

| 4.4 | Complexities Comparison Between Digit-Level RB Multipliers                                               | 41 |

| 4.5 | Complexities comparison between digit-level architectures: the proposed                                  |    |

|     | RB multiplier versus some NB multipliers for a class of fields that there                                |    |

|     | exists a type I ONB                                                                                      | 42 |

| 5.1 | Contents of the flip-flops in the proposed multiplier in $\mathbb{F}_{2^4}$                              | 52 |

| 5.2 | Complexity comparison for word level redundant basis multipliers                                         | 54 |

| 5.3 | Are-Delay Complexity comparison for different architectures where there                                  |    |

|     | exist a type I ONB                                                                                       | 55 |

| 5.4 | Complexity comparison of word level type I optimal NB or RB multipliers                                  |    |

|     | in $\mathbb{F}_{2^{268}}$ for different values of $w, k, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots$ | 56 |

| 5.5 | Normalized Complexity Comparison of Different Word Size Multipliers in                 |

|-----|----------------------------------------------------------------------------------------|

|     | $\mathbb{F}_{2^{268}}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ |

| 6.1 | Complexities comparison                                                                |

| 6.2 | Complexity comparison of word-level type II optimal normal basis or re-                |

|     | ordered normal basis multipliers in $GF(2^{233})$ for different values of $w, k.$ 78   |

| 7.1 | Complexity Comparison between Two VLSI implementations for a 197 Bit                   |

|     | Multiplier                                                                             |

| 8.1 | Complexities Comparison Between Type II ONB / Reordered Normal Ba-                     |

|     | sis Multipliers                                                                        |

| 8.2 | load-module Input/Output Characteristics                                               |

| 8.3 | Complexity Comparison Between Two VLSI Implementations for a 233-                      |

|     | bit Multiplier                                                                         |

## List of Abbreviations

| AEDS  | AND-Efficient Digit-Serial.                                               |

|-------|---------------------------------------------------------------------------|

| ASIC  | Application-Specific Integrated Circuit.                                  |

| BPWS  | Bit-Parallel Word-Serial.                                                 |

| BSWP  | Bit-Seriall Word-Parallel.                                                |

| CAD   | Computer Aided Design.                                                    |

| CMOS  | Complementary Metal-Oxide-Semiconductor.                                  |

| ECC   | Elliptic Curve Cryptograhy.                                               |

| ECDSS | Elliptic Curve Digital Signature Standard.                                |

| FPGA  | Field-Programmable Gate Array.                                            |

| GF    | Galois Field.                                                             |

| IC    | Integrated Circuit.                                                       |

| IEEE  | Institute of Electrical and Electronics Engineers.                        |

| ISO   | International Organization for Standardization.                           |

| LUT   | Look-Up-Table.                                                            |

| NB    | Normal Basis.                                                             |

| NIST  | National Institute of Standards and Technology.                           |

| ONB   | Optimal Normal Basis.                                                     |

| RB    | Redundant Basis.                                                          |

| RNB   | Reordered Normal Basis.                                                   |

| SMPO  | Sequential Multiplier with Parallel Output.                               |

| VHDL  | Very high speed integrated circuit (VHSIC) Hardware Description Language. |

| VLSI  | Very-Large-Scale Integration.                                             |

| XEDS  | XOR-Efficient Digit-Serial.                                               |

### **Chapter 1**

### Introduction

Finite field is a set of finite elements where one can add, subtract, multiply, and divide such that properties of associativity, distributivity, and commutativity are satisfied [25]. Finite fields have important applications in error control coding and cryptography[29].

Two different types of finite field are commonly used in practice: prime field  $\mathbb{F}_p$ , and the binary field  $\mathbb{F}_{2^m}$ . Binary field is an extension of the prime field,  $\mathbb{F}_2$ , which contains  $2^m$  elements. Binary fields are attractive for high speed cryptography applications since they are suitable for hardware implementation [18]. For applications to elliptic curve cryptography, binary field sizes are required to be at least 160 bits respectively [18].

In  $\mathbb{F}_{2^m}$ , addition is nothing but exclusive-oring of two binary vectors. Multiplication is more complicated, while division or inversion can be broken down into a series of consecutive multiplication operations [11],[41]. In practice, the finite field multiplier becomes the key arithmetic unit for any system based on finite field computations.

Efficiency of finite field multiplication depends on the choice of the basis to represent field elements. Bases that have been used for realizing finite field multipliers include poly-

1

nomial basis, normal basis (NB), dual bases, triangular basis, redundant representation or redundant basis, and their variations (*i.e.*, shifted polynomial basis) [18, 33, 16, 10, 7, 38, 44, 17, 8].

In this work, we are mainly interested in normal basis and redundant representation, since squaring operation can be achieved by reordering the element coefficients which is free in hardware. Free squaring operation can be used to speed up the exponentiation operation by repeated squaring and multiplication [14].

In normal basis, the complexity of multiplication is measured with the multiplication matrix [30]. For a binary extension field, the multiplication matrix entries are either zero or one, and the number of ones inside the multiplication matrix is referred to as normal basis complexity. The normal basis in  $GF(2^m)$  for which the complexity achieves its minimum, 2m - 1, is referred to as the optimal normal basis (ONB). Two types of optimal normal bases have been found which are referred to as type I and type II optimal normal basis[30]. Reordered normal basis is referred to as a certain permutation of a type II optimal normal basis [12], [44].

Redundant representation is especially interesting because it not only offers almost free squaring as normal basis does, but also eliminates modular operation for multiplication. The main idea for multiplication using redundant representation is to embed a field in a larger ring and perform the multiplication there [44]. The ring used here has a simple structure and is referred to as a cyclotomic ring, such that the modular operation can be saved in a multiplication operation. Since embedding a field is not unique, each field element in the ring can be presented in more than one way, so the representation contains a certain amount of redundancy.

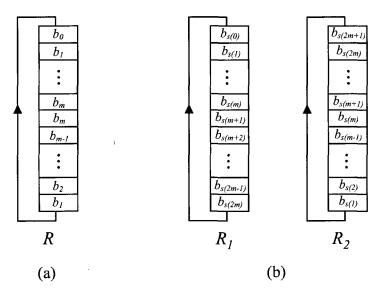

The main drawback for the redundant representation is that it uses more bits to represent a field element, where the number of representation bits depends on the size of the cyclotomic ring. For the class of fields  $\mathbb{F}_{2^m}$  such that there exist a type I optimal normal basis (ONB), the number of bits required for a redundant representation of a field element is m + 1. Also, for the class of fields  $\mathbb{F}_{2^m}$  such that there exist a type II optimal normal basis (ONB), the number of bits required for a redundant representation of a field element is 2m + 1.

Hardware implementation of finite field multipliers can usually be divided into three categories. In the first category there are bit-level or bit-serial multipliers [22],[1],[15],[11]. A bit-level multiplier takes m clock cycles to finish one multiplication in a binary field of size m. The multipliers in this class are considered to have low power consumption, occupy a small area of silicon, and operate slowly for large field sizes. The second category are bit-parallel or full-parallel multipliers [35],[24],[20],[43]. A full parallel multiplier takes one clock cycle to finish one field multiplication. These multipliers are not usually economical for implementation since they require large silicon area and high bandwidth for input and output ports.

The third category are word-level or digit-level finite field multipliers, which are the most commonly implemented in practice [12],[44],[22],[32],[31],[36],[37]. A word-level multiplier takes w clock cycles,  $1 \le w \le m$ , to finish one multiplication operation in  $\mathbb{F}_{2^m}$ . The value of w can be selected by designer to set the trade off between area and speed according to the application. Decreasing the value of w will result in faster and larger multipliers while increasing w will make smaller and slower multipliers. Note that bit-level and full parallel multipliers can be viewed as special cases of word-level multipliers for w = m and w = 1 respectively.

### **1.1 Summary of Contributions**

In this work, different word-level architectures for multiplication using binary field are proposed. It has been shown that the proposed architectures are more efficient compared to similar proposals considering area/delay complexities as a measure of performance. Practical size multipliers for cryptography applications have been realized in hardware using FPGA or standard CMOS technology. Also, different VLSI implementations for multipliers were explored, which resulted in more efficient implementations for some of the regular architectures. The new implementations use a simple module designed in domino logic as the main building block for the multiplier. Significant improvements were achieved designing practical size multipliers using the proposed methodology.

### **1.2** Outline of the Thesis

The rest of this thesis is organized as follows. Chapter 2, is a brief review of finite filed theory. After covering basic definitions and elementary properties such as group, ring and field, bases for finite fields are presented. Normal basis and redundant basis representation with their arithmetic operations are discussed in detail. Type I and II optimal normal basis, which are two important classes of normal basis, and their relationship with redundant representation are also discussed in this chapter.

Chapter 3 discusses two new high speed bit-serial word-parallel, or comb style finite field multipliers. The first proposal utilizes redundant representation for any binary field, and the other uses a reordered normal basis for the binary field where there exists a type II optimal normal basis. The proposed redundant representation architecture has a smaller critical path delay compared to the previous methods, while its complexity remains approximately the same. The proposed reordered normal basis multiplier has a significantly smaller critical path delay compared to the previous methods using the same basis or normal basis. FPGA implementation results of the proposed multipliers are compared to those of the previous methods using the same basis, confirming that the proposed multipliers allow for a much higher clock rate.

Chapter 4, presents a novel serial-in parallel-out finite field multiplier using redundant representation. It is shown that the proposed architecture has either significantly lower complexity and comparable critical path delay, or significantly smaller critical path delay

and comparable complexity, in comparison to the previously proposed architectures using the same representation. For the class of fields such that there exists a type I optimal normal basis, the proposed multiplier compares favorably to the normal basis multipliers. A digitlevel version for the new multiplier is also presented in this chapter.

In Chapter 5, a high speed word-level finite field multiplier in  $\mathbb{F}_{2^m}$  using redundant representation is proposed. For the class of fields such that there exists a type I optimal normal basis, the new architecture has significantly higher speed compared to previously proposed word-level architectures using either normal basis or redundant representation at the expense of moderately higher area complexity. One of the unique features of the proposed word-level multiplier is that the critical path delay is not a function of the field size, nor the word size. It is also shown that the new multiplier out-performs all other multipliers in the comparison when considering the product of area and delay as a measure of performance. VLSI implementation of the proposed multiplier in a  $0.18\mu m$  CMOS process is also presented as a module for an elliptic curve processor.

In Chapter 6, two high speed word-level finite field multipliers using reordered normal basis are proposed, where reordered normal basis is referred to as a certain permutation of type II optimal normal basis. Complexity comparison shows that the proposed architectures are faster than all the previously presented architectures in the open literature using either a type II optimal normal basis or a reordered normal basis at the expense of moderately higher complexity. One unique feature of the new word-level architectures is that the critical path delay is not a function of the word size or the field size. This enables the proposed multipliers to operate at very high clock rate regardless of the word or field size. Such high speed word-level multipliers are expected to have applications in public key cryptography, i.e. elliptic curve cryptosystems.

Chapter 7 presents a high speed VLSI implementation of a 233-bit Serial-In Parallel-Out finite field multiplier. The proposed design performs multiplication using a reordered normal basis; a permutation of a type II optimal normal basis. The multiplier was implemented in a .18  $\mu m$  TSMC CMOS technology using multiples of a domino logic block. The domino logic design was simulated, and functioned correctly up to a clock rate of 1.587 *GHz*, yielding a 99% speed improvement over the static CMOS' simulation results, while the area was reduced by 49%. This multiplier's size of 233 bits is currently recommended by the National Institute of Standards and Technology (NIST) in their Elliptic Curve Digital Signature Standard (ECDSS), and is used in practice for binary field multiplication in Elliptic Curve Cryptosystems.

Finally some concluding remarks and future work are presented in Chapter 8.

### Chapter 2

### **Mathematical Preliminaries**

This chapter briefly reviews the mathematical background on finite fields. It starts with reviewing basic definitions such as group, ring, and field, and then covers more advanced topics such as bases and arithmetic operations. Normal basis and redundant representation with their arithmetic operations are discussed in detail. The relationship between different classes of normal basis and redundant representation is also discussed in this chapter. For a more detailed review of finite fields and their applications readers are referred to [25, 29, 26]

### 2.1 Groups, Rings and Fields

**Definition 2.1.1.** [25] A group (G, \*) is a set G together with a binary operation \* on G such that the following three properties hold:

- 1. The binary operator \* is associative; that is, for any  $a, b, c \in G$ ,

- a \* (b \* c) = (a \* b) \* c

- There is an identity (or unity) element e in G such that for all a ∈ G,

a \* e = e \* a = a.

- For each a ∈ G, there exist an inverse element a<sup>-1</sup> in G such that a \* a<sup>-1</sup> = a<sup>-1</sup> \* a = e.

If for all  $a, b \in G$ , a \* b = b \* a, then G is referred to as an *abelian* or *commutative group*. A group with finite number of elements is referred to as a *finite group*.

**Definition 2.1.2.** [25] A ring (r, +, \*) is a set R together with two binary operations, denoted by + and \*, such that the following three properties hold:

- 1. R is an abelian group with respect to +.

- 2. The binary operator \* is associative, which means for all  $a, b, c \in R$ (a \* b) \* c = a \* (b \* c).

- 3. The distribution law holds, which means for all  $a, b, c \in R$ a \* (b + c) = a \* b + a \* c and (b + c) \* a = b \* a + c \* a.

The identity element of the abelian group R with respect to + is called the *zero element*, while the identity element with respect to \* (if it exist) is called the *identity element*. A ring is called *commutative* if the binary operator \* is commutative.

**Definition 2.1.3.** [25] A *field* (f, +, \*) is a set F together with two binary operations, denoted by + and \*, such that the following two properties hold:

- 1. F is a commutative ring under + and \*.

- 2. Nonzero elements of F from a group with the binary operation \*.

A field with a finite number of elements is referred to as a *finite field*. The order of a finite field is the number of elements in the field. There exists a finite field F of order q if and

only if q is a prime power, that is  $q = p^m$  where p is a prime number referred to as a the *characteristic* of F and m is a positive integer [18]. For any prime power q, there is essentially only one finite field of order q. This means that any two finite fields of order q are structurally the same, except that the labeling used to represent the field elements may be different. We say that any two finite fields of order q are *isomorphic*, and denote such a field by  $\mathbb{F}_{q^m}$  or  $GF(q^m)$  (GF stands for Galois Field, in honor of Evariste Galois, a French mathematician who is known for his work on the theory of equations and abelian integrals).

### 2.2 Binary Field and Bases

For a finite field F with order of  $q = p^m$ , if m = 1 then the field is referred to as a prime field. If  $m \ge 2$ , then the finite field is referred to as an extension field. Finite fields of order  $q = 2^m$  are called *binary fields* or *characteristic-two finite fields*.

An important factor that has an important effect on finite field arithmetic efficiency is the basis used to represent the field elements. Common bases used in practice are polynomial basis (PB) and normal basis (NB) [25],[33]. Polynomial basis is probably the most popular basis which has been widely used for hardware and software implementations [18]. Normal basis, on the other hand, is advantageous for hardware implementation since the squaring operation can be implemented at no cost. Free squaring operations can be used to speed up the exponentiation operation by repeated squaring and multiplication [14],[2].

Recently, a method of redundant representation of field elements has attracted attention [42, 7, 38, 44]. The idea here was to use the minimal cyclotomic ring in which the current field can be embedded in, and perform the field arithmetic operations in the ring. Advantages of using redundant representation not only include the free squaring operation offered by this method but also its 'basis' elements form a cyclic group, and thus the modulo reduction step can be avoided carrying out the field multiplication operation.

### **2.2.1** Normal Basis and Its Arithmetic in $\mathbb{F}_{2^m}$

#### 2.2.1.1 Normal Basis Representation

Theorem 2.2.1. [25] Let P(x) be a degree m irreducible polynomial over  $\mathbb{F}_{2^m}$  whose m roots  $\{\beta, \beta^2, \dots, \beta^{2^{m-1}}\}$  are linearly independent in  $\mathbb{F}_{2^m}$ . Then these m roots form a basis in  $\mathbb{F}_{2^m}$  which is referred to as *normal basis*.

It is well known that there always exists a normal basis for the finite field  $\mathbb{F}_{2^m}$  for all positive values of m [25]. Assume that  $\beta \in \mathbb{F}_{2^m}$  is an element such that  $I = \{\beta, \beta^2, \beta^{2^2}, \dots, \beta^{2^{m-1}}\}$ is a normal basis, then element  $A \in \mathbb{F}_{2^m}$  can be represented as:

$$A = \sum_{i=0}^{m-1} a_i \beta^{2^i} = a_0 \beta + a_1 \beta^2 + a_2 \beta^{2^2} + \dots + a_{m-1} \beta^{2^{m-1}}.$$

The main advantage of normal basis representation is that, element A can be squared by a simple right circular shift on its coordinates,  $A^2 = \sum_{i=0}^{m-1} a_{(i+1)}\beta^{2^i}$ , where (i+1) denotes that i+1 is to be reduced modulo m. This property for normal basis comes from the fact that  $\beta^{2^m} = \beta$ , and is used to speed up exponentiation by use of the square and multiply algorithm [18].

#### 2.2.1.2 Normal basis multiplication

Let field elements  $A, B \in \mathbb{F}_{2^m}$  be represented with respect to (w.r.t.) the normal basis  $I = \{\beta, \beta^2, \cdots, \beta^{2^{m-1}}\}$  as  $A = \sum_{i=0}^{m-1} a_i \beta^{2^i}$  and  $B = \sum_{j=0}^{m-1} b_j \beta^{2^j}$ , respectively. Then the product of A and B can be given by

$$C = A \cdot B = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j \beta^{2^i} \beta^{2^j} \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j (\beta \beta^{2^{(j-i)}})^{2^i}.$$

(2.1)

Define  $t_{i,k} \in \mathbb{F}_2$  to be the coefficient of  $\beta^{2^k}$  in the expansion of the product  $\beta\beta^{2^i}$  when represented w.r.t. *I* [30],

$$\beta \beta^{2^{i}} = \sum_{k=0}^{m-1} t_{i,k} \beta^{2^{k}}.$$

(2.2)

Then it follows from (2.2) that

$$(\beta\beta^{2^{(j-i)}})^{2^{i}} = \left(\sum_{k=0}^{m-1} t_{(j-i),k}\beta^{2^{k}}\right)^{2^{i}} = \sum_{k=0}^{m-1} t_{(j-i),k}\beta^{2^{k+i}}i = \sum_{k=0}^{m-1} t_{(j-i),(k-i)}\beta^{2^{k}}.$$

(2.3)

The last step in (2.3) follows from the proper substitution on the subscript k. Substituting  $\beta\beta^{2^{(j-i)}}$  in (2.1) using (2.3)

$$C = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j \Big( \sum_{k=0}^{m-1} t_{(j-i),(k-i)} \beta^{2^k} \Big) = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} \sum_{k=0}^{m-1} a_i b_j t_{(j-i),(k-i)} \beta^{2^k}.$$

(2.4)

Then the coefficients of the product C w.r.t. the NB I can be given by

$$C = \sum_{k=0}^{m-1} c_k \beta^{2^k}, \text{ where } c_k = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j t_{(j-i),(k-i)}.$$

(2.5)

Also note that from eqn (2.5) and after proper substitution on i and j, we can compute  $c_{k+1}$  with

$$c_{k+1} = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j t_{(j-i),(k-i+1)} = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_{(i+1)} b_{(j+1)} t_{(j-i),(k-i)}.$$

(2.6)

Eqn (2.6) shows that  $c_{i+1}$  can be computed by applying the same formula used to compute  $c_i$ , if the coefficient vectors of A and B are cyclically shifted by one.

To obtain the values of  $t_{(j-i),(k-i)}$ , a matrix  $T = [t_{l,n}]$  is created where row l corresponds to the coefficients in the expansion of the product  $\beta\beta^{2^l}$  and the column n corresponds to the coefficients of  $\beta^{2^n}$  in the expansion of the products  $\beta\beta^{2^l}$ , l = 0, 1, ..., m - 1.

Matrix T is referred to as the *multiplication table* for the normal basis in this thesis. Note that in [30] the same multiplication table was denoted by  $T_0$  while matrices  $T_k$ , k = 1, 2, ..., m-1, were defined for the expansion of  $\beta^{2^k}\beta^{2^l}$ . It also should be noted that other matrices  $T_i$ , i = 1, 2, ..., m-1 in [30], can be generated from  $T_0$  and circular row/column shifting. In this thesis we use only one multiplication matrix T when deriving the formula for computing  $c_i$ , i = 0, 1, ..., m-1.

Let the number of nonzero entries in T be denoted by  $C_N$ . It can be seen from equations (2.5) and (2.6) that the product coefficient  $c_k$  can be computed by summing up exactly  $C_N$

terms. Thus, the generation of each  $c_k$  requires  $C_N$  multiplication operations in  $\mathbb{F}_2$  and  $C_N - 1$  addition operations in  $\mathbb{F}_2$ .

$C_N$  is referred to as the complexity of a normal basis and it has been shown that  $C_N \ge 2m - 1$  [30]. When  $C_N = 2m - 1$  for a NB, it is called an optimal normal basis (ONB). Since computations in the optimal normal basis are minimized, these bases are of high importance for cryptographic applications. A type II ONB corresponds to the case where no row or column in T contains more than two nonzero entries.

**Example 1** Consider the finite field  $\mathbb{F}_{2^5}$ . The root  $\beta$  of the irreducible polynomial  $P(x) = x^5 + x^4 + x^3 + x + 1$  generates a normal basis  $I = \{\beta, \beta^2, \beta^{2^2}, \beta^{2^3}, \beta^{2^4}\}$ . The multiplication table T can be found as

$$T = \begin{bmatrix} 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 0 \\ 1 & 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 1 & 0 \end{bmatrix}$$

The closed form solution for multiplication can be easily found from (2.5) as follows:

$$c_{i} = b_{i}a_{i+3} + b_{i+1}(a_{i+2} + a_{i+4}) + b_{i+2}(a_{i+1} + a_{i+4}) + b_{i+3}(a_{i} + a_{i+4}) + b_{i+4}(a_{i+1} + a_{i+2} + a_{i+3} + a_{i+4}).$$

$$(2.7)$$

### **2.2.2** Redundant Basis and its Arithmetic in $\mathbb{F}_{2^m}$

#### 2.2.2.1 Redundant Representation

Let  $\beta$  be a primitive  $n^{\text{th}}$  root of unity in some extension field of  $\mathbb{F}_2$  ( $\beta^n = 1$ ). The splitting field of  $\beta$  is called the  $n^{\text{th}}$  cyclotomic field and denoted by  $\mathbb{F}_2^{(n)}$ . Elements in  $\mathbb{F}_2^{(n)}$  can be represented in the form

$$A = a_0 + a_1\beta + a_2\beta^2 + \dots + a_{n-1}\beta^{n-1}, \ a_i \in \mathbb{F}_2, \ i = 0, 1, \dots, n-1.$$

(2.8)

Let  $\mathbb{F}_{2^m}$  be a field that can be embedded in  $\mathbb{F}_2^{(n)}$ . The following theorem characterizes the relationship between m and n.

Theorem 2.2.2. [25] Let n be an odd positive integer. Then,  $\mathbb{F}_{2^m}$  is contained in  $\mathbb{F}_2^{(n)}$  if and only if m divides the multiplicative order of  $2 \mod n$ .

For a given  $\mathbb{F}_{2^m}$  we are particularly interested in  $\mathbb{F}_2^{(n)}$  with the minimal value of n such that  $\mathbb{F}_{2^m}$  can be embedded in  $\mathbb{F}_2^{(n)}$ . Obviously, field element  $A \in \mathbb{F}_{2^m}$  can also be represented with (2.8). Note that  $1 + \beta + \beta^2 + \cdots + \beta^{n-1} = 0$  and the representation of A is not unique. For example, the two n-tuples  $(a_0, a_1, \cdots, a_{n-1})$  and  $(a_0 + 1, a_1 + 1, \cdots, a_{n-1} + 1)$  represent the same element A. By slightly abusing the terminology, the set  $[1, \beta, \beta^2, \cdots, \beta^{n-1}]$  is denoted as *redundant basis* (RB) for  $\mathbb{F}_{2^m}$  [44]. Also note that the elements of a RB form a cyclic group of order n and

$$\beta \cdot \beta^{i} = \begin{cases} \beta^{i+1} & i \neq n-1, \\ 1 & i = n-1. \end{cases}$$

#### 2.2.2.2 Redundant Basis Multiplication

Let field elements  $A, B \in \mathbb{F}_{2^m}$  be represented with respect to the RB  $I_1 = [1, \beta, \beta^2, \dots, \beta^{n-1}]$ as n-1

$$A = \sum_{i=0}^{n-1} a_i \beta^i$$

and  $B = \sum_{i=0}^{n-1} b_i \beta^i$ ,

respectively, where  $a_i, b_i \in \mathbb{F}_2, i = 0, 1, \dots, n-1$ . Note that  $n \ge m+1$  and  $\beta^n = 1$ . Then it follows  $\beta^i \cdot B = \sum_{j=0}^{n-1} b_{(j-i)}\beta^j$ , where (j-i) denotes that j-i is to be reduced modulo n. The product of field elements A and B can be given by [44]

$$A \cdot B = \sum_{i=0}^{n-1} a_i(\beta^i \cdot B) = \sum_{i=0}^{n-1} a_i(\sum_{j=0}^{n-1} b_j \beta^{i+j}).$$

$$= \sum_{i=0}^{n-1} a_i(\sum_{j=0}^{n-1} b_{(j-i)} \beta^j) = \sum_{j=0}^{n-1} (\sum_{i=0}^{n-1} a_i b_{(j-i)}) \beta^j.$$

If we define

$$A \cdot B = C \stackrel{\Delta}{=} \sum_{j=0}^{n-1} c_j \beta^j$$

, then  $c_j$  can be given by

$c_j = \sum_{i=0}^{n-1} a_i b_{(j-i)}, \quad j = 0, 1, \dots, n-1.$

(2.9)

#### 2.2.2.3 Redundant Basis and Normal Basis