# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2009

# Testing in context: Efficiency and executability

Lihua Duan University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

# **Recommended Citation**

Duan, Lihua, "Testing in context: Efficiency and executability" (2009). *Electronic Theses and Dissertations*. 8202.

https://scholar.uwindsor.ca/etd/8202

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# NOTE TO USERS

This reproduction is the best copy available.

# UMI

# Testing in Context: Efficiency and Executability

by

Lihua Duan

A Dissertation

Submitted to the Faculty of Graduate Studies through Computer Science in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

> Windsor, Ontario, Canada 2009 ©2009 Lihua Duan

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-57572-7 Our file Notre référence ISBN: 978-0-494-57572-7

# NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Canada

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### Declaration of Co-Authorship / Previous Publication

#### I. Co-Authorship Declaration

I hereby declare that this dissertation incorporates material that is the result of joint research undertaken in collaboration with my advisor, Dr. Jessica Chen. The collaboration is covered in Chapter 7 of the dissertation.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my dissertation, and have obtained written permission from each of the co-author(s) to include the above material(s) in my dissertation.

I certify that, with the above qualification, this dissertation, and the research to which it refers, is the product of my own work.

#### **II.** Declaration of Previous Publication

This dissertation includes one original paper that have been previously published/submitted for publication in peer reviewed conference proceedings, as follows:

| Dissertation Chapter | Chapter 7                                                |  |

|----------------------|----------------------------------------------------------|--|

| Publication title    | Lihua Duan and Jessica Chen. An Approach to Testing      |  |

| /full citation       | with Embedded Context using Model Checker. Proc. of      |  |

|                      | the Ninth International Conference on Formal Engineering |  |

|                      | Methods (ICFEM'08), Lecture Notes in Computer Science    |  |

|                      | Vol. 5256, pp. 66-85, 2008. Springer-Verlag.             |  |

| Publication status   | published                                                |  |

I certify that I have obtained a written permission from the copyright owner(s) to include the above published material(s) in my dissertation. I certify that the above material describes work completed during my registration as graduate student at the University of Windsor.

I declare that, to the best of my knowledge, my dissertation does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my dissertation, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my dissertation. I declare that this is a true copy of my dissertation, including any final revisions, as approved by my dissertation committee and the Graduate Studies office, and that this dissertation has not been submitted for a higher degree to any other University or Institution.

### Abstract

Testing each software component in isolation is not always feasible. We consider testing a deterministic Implementation Under Test (IUT) together with some other correctly implemented components as its context. One of the essential issues of testing in context is test executability problem, i.e., tests generated solely from the specification of the IUT may not be executable due to the uncontrollable interaction between the IUT and its context. On the other hand, generating a test sequence from the abstract specifications of a stateful IUT and its context often suffers from the well-known state explosion problem. In this dissertation, we solve the problem of generating a minimal-length test sequence from a given specification of a stateful IUT and its embedded context. By adopting model checking techniques, we avoid the state explosion problem during test generation and avoid the test executability problem during testing in context.

**Keywords**: finite state machines, conformance testing, test generation, testing in context, test sequences.

This work is dedicated to my parents, Zhanyi Duan and Yubing Lian, who have been teaching me the value of life.

#### Acknowledgments

First and foremost, I would like to express my heartfelt thanks to my advisor, Dr. Jessica Chen, for her invaluable guidance, extensive time, extreme patience, and enthusiastic encouragement during my entire graduate studies. Without her help, the work presented here would not have been possible. I appreciate her for all she has done for me and it will always be held deeply in my memory.

I would like to thank my internal committee members, Dr. Arunita Jaekel, Dr. Jianguo Lu, and Dr. Huapeng Wu for attending a series of my research seminars and giving their precious comments and suggestions to the research work through all my Ph.D study. I would like also to express my appreciation to my external examiner, Dr. Wuwei Shen, for his zealous help of examining my dissertation work.

My special thanks go to the secretary at the School of Computer Science, Ms. Mandy Dumouchelle, for her consistent help.

Last, but not least, I would like to thank all my friends for their support and encouragement for my studies.

# Contents

| D  | eclar  | ation of Co-Authorship/Previous Publication  | iii          |

|----|--------|----------------------------------------------|--------------|

| A  | bstra  | $\mathbf{ct}$                                | $\mathbf{v}$ |

| D  | edica  | tion                                         | vi           |

| A  | ckno   | wledgements                                  | vii          |

| Li | ist of | Tables                                       | x            |

| Li | st of  | Figures                                      | xi           |

| 1  | Intr   | oduction                                     | 1            |

| 2  | Fin    | te state machines and related fault models   | 4            |

|    | 2.1    | Finite state machines                        | 4            |

|    | 2.2    | Fault models                                 | 7            |

| 3  | Ma     | in issues in testing in context              | 9            |

|    | 3.1    | External equivalence                         | 11           |

|    | 3.2    | Main issues                                  | 12           |

| 4  | Fau    | lt coverage and test optimization            | 14           |

|    | 4.1    | Graph representations of FSMs                | 14           |

|    | 4.2    | T-method                                     | 15           |

|    | 4.3    | U-method                                     | 16           |

|    |        | 4.3.1 Test optimization                      | 20           |

|    |        | 4.3.2 Weakness and strength of the U-method  | 22           |

|    | 4.4    | D-method                                     | 24           |

|    |        | 4.4.1 The test optimization approach in [39] | 30           |

|    |        | 4.4.2 The test optimization approach in [86] | 33           |

|    | 4.5    | W-method                                     | 35           |

|    | 4.6    | Summary                                      | 37           |

| 5 | Test        | t executability problem                      | 39 |

|---|-------------|----------------------------------------------|----|

| 6 | Test        | t generation with stateless embedded context | 40 |

|   | 6.1         | Solving test executability problem           | 41 |

|   | 6.2         | Reducing the use of the context              | 44 |

|   | 6.3         | An application                               | 44 |

| 7 | Tes         | t generation with stateful embedded context  | 47 |

|   | <b>7</b> .1 | The proposed method                          | 50 |

|   | 7.2         | Test generation using model checking tools   | 53 |

|   |             | 7.2.1 Finding transitions in $\mathcal{R}$   | 54 |

|   |             | 7.2.2 Finding a distinguishing sequence      | 56 |

|   | 7.3         | An application                               | 57 |

| 8 | Cor         | nclusion                                     | 62 |

| R | efere       | nces                                         | 63 |

| V | ita A       | uctoris                                      | 72 |

# List of Tables

| 1 | Transitions in $M_0$                   | 7  |

|---|----------------------------------------|----|

| 2 | UIO sequences for each states in $M_1$ | 16 |

# List of Figures

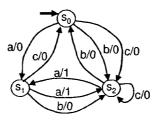

| 1        | An example FSM $M_0$                                                                      | 7  |

|----------|-------------------------------------------------------------------------------------------|----|

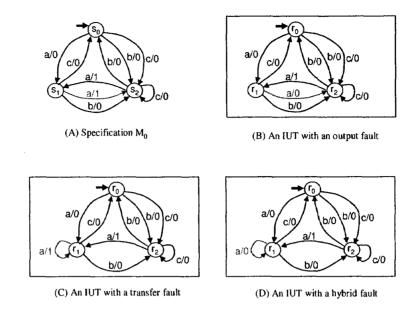

| <b>2</b> | Faulty IUTs of example FSM $M_0$                                                          | 8  |

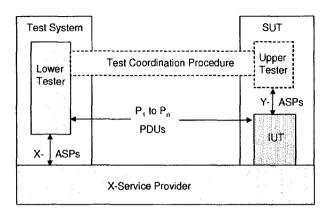

| 3        | A test architecture of distributed systems [48]                                           | 9  |

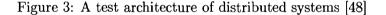

| 4        | Context-based testing: types of test architecture                                         | 10 |

| 5        | FSM $M_1$ of the connection establishment protocol for one participant $\ldots$           | 17 |

| 6        | Illustration of the weakness of the U-method                                              | 23 |

| 7        | An illustration of the necessity of state identification                                  | 26 |

| 8        | An illustration of the necessity of transition verification $\ldots \ldots \ldots \ldots$ | 27 |

| 9        | Illustration of the construction of $G'$ . The nodes in $U'$ and $V$ are on the           |    |

|          | top and at the bottom respectively. The solid bold arrows and the dashed                  |    |

|          | arrows denote the edges in $E_{\alpha'} \cup E_C$ and $E_T$ , respectively                | 32 |

| 10       | An illustration of the construction of $G^* = (V^*, E^*)$ . Paths in $A \cup B$ are       |    |

|          | represented by bold solid arrows, and D-overlaps among paths in $A\cup B$ are             |    |

|          | represented by the dashed arrows.                                                         | 34 |

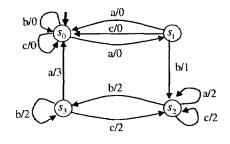

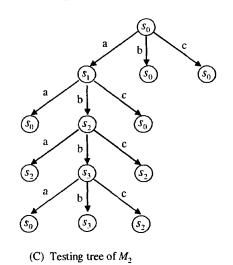

| 11       | An example FSM $M_2$                                                                      | 38 |

| 12       | An illustration of test executability problem caused by improper order of                 |    |

|          | test sequence                                                                             | 40 |

| 13       | An illustration of test executability problem caused by intrinsically non-                |    |

|          | executable transitions                                                                    | 41 |

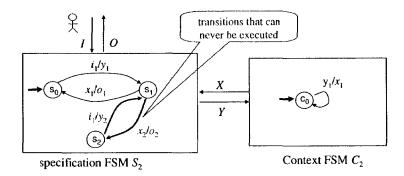

| 14       | An example application of stateless embedded context $\ldots \ldots \ldots \ldots$        | 41 |

| 15       | An illustration of solving executability problem for an IUT with stateless                |    |

|          | embedded comtext                                                                          | 42 |

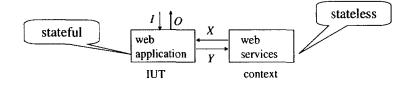

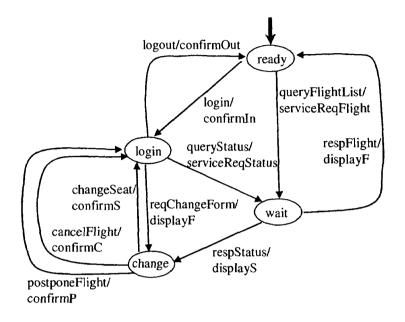

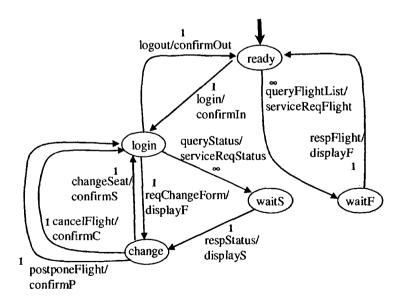

| 16       | An example: online flight reservation system                                              | 46 |

| 17       | An example with split states and weights                                                  | 46 |

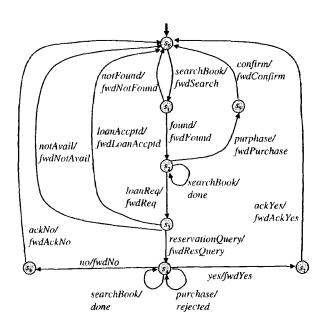

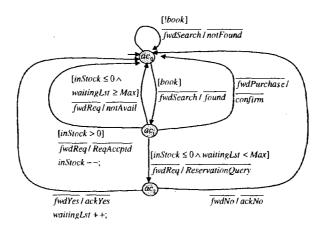

| 18       | Specification FSM of the borrowing library                                                | 59 |

| 19       | Specification extended FSM of the lending library                                         | 60 |

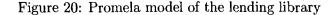

| 20       | Promela model of the lending library                                                      | 61 |

xi

#### 1 INTRODUCTION

# 1 Introduction

Finite State Machines (FSMs) have been widely used to model the abstract behavior of sequential circuits [32, 74], lexical analysis systems [51], and more recently, communications protocols [1, 11, 63, 85]. Furthermore, some more expressive specification languages such as Specification and Description Languages (SDLs) [50], Estelle [49], and Statecharts [69] are based on *extensions* of FSMs. The demand of ensuring the correctness of computer systems motivates the research on *conformance testing* in a setting where system specifications are given in FSMs or FSM-based languages [1, 6, 11, 32, 38, 59, 63, 77, 80, 85].

Given an *implementation under test* (IUT) for which we can only observe its input/output behavior, conformance testing can be conducted to improve our confidence that this implementation *conforms* to its specification. Conformance testing is often carried out by i) constructing from the specification of the system a *test sequence*, which is an input sequence with an expected output sequence; ii) applying the input portion of this sequence to the IUT, which is considered as a *black box*, according to the given test architecture; and iii) determining whether the actual output sequence is produced as expected.

Given specification M describing the expected behavior of the IUT, we can imagine that the IUT behaves according to a certain abstract machine N in the same format. In this setting, conformance testing amounts to establishing the correspondence between Mand N. In doing so, it is essential to understand the fault models. In the following, for convenience, we also use the IUT to represent the implementation FSM N.

A faulty IUT falls into one of the following categories.

- output faults: the IUT produces an incorrect output in response to an input in a state.

- transfer faults: the IUT ends at an incorrect state after applying an input sequence.

- hybrid faults: the IUT has both output faults and transfer faults.

Based on these fault models, a series of fault coverage criteria and test generation methods have been proposed, see [53, 56] for comprehensive surveys on this topic. Testing an IUT in isolation is not always feasible in the unit testing. There are situations when we have to test the IUT together with some other components. As pointed out in [73], this can be the case when the IUT is an embedded component of a complex system, called a *context* of the IUT, only through which the IUT can be accessed. As another example, suppose we want to test a web-based implementation  $WS_1$ , which makes use of web service  $WS_2$ . Due to the difficulty in providing input and observing output all encapsulated according to certain protocol such as SOAP [91], testing  $WS_1$  invokes the necessity of activating  $WS_2$ . Here, again,  $WS_2$  is considered as the *context* of  $WS_1$ . In general, the context can be the system components, the drivers, the stubs, the test beds, and so on.

Obviously, it is worthful to study how to test an IUT within its context. Petrenko et al. first presented a test generation framework for an embedded IUT whose communication with the environment has to be carried out through its context [72, 73]. In particular, the problems of *test executability* and *fault propagation* are addressed in the presence of the context. The test executability problem describes the situation where a test sequence generated from a given specification solely without taking into account the behavior of the context may not be executable when testing in context, and the fault propagation problem describes the situation where the faults of the IUT are masked by the context. In [23, 24, 57, 70], different approaches are discussed for solving the problem of translating internal tests derived for an embedded component into external observable tests of the entire system.

Different from their application domain, our work is applicable to an IUT with an embedded context, i.e. it does not communicate with any component other than  $\mathcal{I}$ . In our current work, we consider the problem of FSM-based deterministic testing on  $(\mathcal{I}, \mathcal{I}_c)$  which is an IUT implementation  $\mathcal{I}$  together with a correct context implementation  $\mathcal{I}_c$ . The communication port between  $\mathcal{I}$  and  $\mathcal{I}_c$  is not controllable but observable. This means that the tester can neither provide input to the IUT using this port nor stop an input from the context to the IUT. It can, however, observe all the input from and all the output to the context. The specification of  $\mathcal{I}$  is given in terms of an FSM.  $\mathcal{I}_c$  can be either stateless or stateful. When  $\mathcal{I}_c$  is stateless, its specification can be given in form

#### 1 INTRODUCTION

of a set of  $\langle request, response \rangle$  pairs. When  $\mathcal{I}_c$  is stateful, we assume that it is specified by a specification language or a structural modelling language. In both cases, we present methods to generate a minimal-length test sequence that can be used to test  $(\mathcal{I}, \mathcal{I}_c)$  without encountering test executability problem during testing.

When the context is stateful, the existing test generation techniques of testing in context often suffer from the state explosion problem. This is caused by requiring the computation of the product of several auxiliary components in addition to the model of the specification of  $\mathcal{I}$ . The ultimate goal of our work is to avoid generating the operational model of the given specification of  $\mathcal{I}_c$  (if a higher level specification is provided) and constructing the global model of  $\mathcal{I}$  and  $\mathcal{I}_c$ . In order to do so, we employ model checking tools to retrieve necessary information from the context specification so that test sequences for  $(\mathcal{I}, \mathcal{I}_c)$  can be generated. The idea of using a model checking tools to generate tests is not new. In the literature, various applications have presented. Ammann et al. combined model checking with *mutation analysis* to generate test cases [2]: after a specification model is mutated by applying mutation operators, a model checker generates counter-examples to distinguish the mutant models from the original specification model, and thus test cases are derived. Gargantini and Heitmeyer presented a technique to construct test sequences upon a special class of so-called Software Cost Reduction requirements, by using a model checker [26]. In order to save memory from a huge predefined test suite, Tretmans and de Vries [17] used model checker SPIN to generate tests *during testing* for non-deterministic stateful systems. How to generate test cases according to some data flow test selection criteria is discussed in [45]. In [75], Goltz et al. used a model checker to generate a shortest distinguishing sequence of an EFSM.

Note that it is straightforward to extend our work to a more general case where the embedded context consists of a set of components, each having its own port to communicate with  $\mathcal{I}$ . In terms of applying model checking tools for test generation, we have added one more example along this line of research, particularly for testing in context.

We consider conformance testing of *deterministic* systems in this dissertation. The readers who are interested in conformance testing of *non-deterministic* systems should refer to [25, 35, 36, 58, 71, 82, 96].

The rest of the dissertation is organized as follows. In Chapter 2, we give a brief introduction to FSMs and the related notations and terminologies that will be used later on, followed by a discussion of the fault models of FSMs. The main issues of testing in context are addressed in Chapter 3. Among those issues, four widely used fault coverage criteria together with some existing test generation and optimization techniques are discussed in Chapter 4. In Chapter 5, test executability problem is explained. Test generation techniques for an IUT with stateless and stateful embedded context are presented in Chapter 6 and 7, respectively. In the end, we conclude our work with some final remarks.

# 2 Finite state machines and related fault models

There are various formalisms to describe the expected behavior of a stateful system. Suitable for different levels of abstractions, they range from formal specification languages such as process algebras, to structural/operational modelling languages such as (input/output) *labelled transition systems (LTSs)* and *Finite State Machines (FSMs)*. Here, we use FSMs to show the main issues related to testing in context.

#### 2.1 Finite state machines

There are two types of FSMs: Mealy machines [61] and Moore machines [66]. The difference between them lies in how an output is determined: For the former, an output is determined by the current state and an input; while for the latter, an output is determined by the current state alone (not directly by an input). Usually, the number of states in a Moore machine is greater than or equal to that in an equivalent Mealy machine. We adopt Mealy machines since they are more natural to model software systems. As mentioned in the Introduction, we consider deterministic FSMs. In order to explicitly associate each input and output with a *port* (an *interface* to communicate with a certain component), we use n-port FSM to describe the abstract behavior of the systems with n ports.

**Definition 1 (Finite state machines)** A deterministic n-port Finite State Machine (also called finite state machine for short) is defined by a tuple  $(S, I, O, \delta, \lambda, s_0)$ .

• S is a finite set of states where  $s_0 \in S$  is its initial state.

- I = ∪<sub>i=1</sub><sup>n</sup> I<sub>i</sub>, where I<sub>i</sub> is the input alphabet of port i (i = 1,...,n). Being abstract, these input symbols encapsulate the information of the communication channels. Thus, without loss of generality, we can assume that the input symbols at different ports are distinct, i.e. I<sub>i</sub> ∩ I<sub>j</sub> = Ø for i ≠ j.

- O = Π<sup>n</sup><sub>i=1</sub>O<sub>i</sub> where O<sub>i</sub> is the output alphabet of port i (i = 1,...,n).

Each o ∈ O is a vector of outputs denoted by o = ⟨o<sub>1</sub>,...,o<sub>n</sub>⟩ where o<sub>i</sub> ∈ O<sub>i</sub> for i = 1,...,n. We do not consider the order in which we observe output o<sub>i</sub> and o<sub>j</sub> at different ports. When there is no output at a port i, we use a distinct symbol to denote it.

- $\delta$  is the transition function that maps  $S \times I$  to S, and

$\lambda$  is the output function that maps  $S \times I$  to O.

A "slow environment" assumption is usually used in the literature. That is, whenever an input reaches the system, the system will always prompt the output for it before the second input can reach the system.

The inputs and the outputs are abstract symbols. The discussions on data types and complicate data structures in the inputs and outputs are beyond the scope of this dissertation.

Note that functions  $\lambda$  and  $\delta$  can be partial, i.e., it is possible that there exists  $i \in I$  for some  $s \in S$  such that  $\lambda(s, i) = null$  and  $\delta(s, i) = null$ . We will use  $\delta(s, x) = null$  to denote that there is no image of  $\delta$  for the given state s of S and the given input x of I. In this case, we also have  $\lambda(s, x) = null$ . Furthermore, we extend the input of  $\lambda$  and  $\delta$  from an input alphabet to a sequence of input alphabets with their meanings obtained straightforwardly from the original ones.

For simplicity, we assume the number of states of M is n and the states of M are enumerated, giving  $S = \{s_0, \ldots, s_{n-1}\}$ .

A transition t is defined by a tuple  $(s_1, s_2, x/y)$  in which  $s_1$  is the starting state, x is the input,  $s_2 = \delta(s_1, x)$  is the ending state, and  $y = \lambda(s_1, x)$  is the output. The input/output x/y is called the *label* of t. Note that when an FSM has only one port or there is exactly

one output for each transition of an FSM, we use a single output alphabet instead of an output vector to denote the output for simplicity.

Let  $t_i$  be a transition for  $1 \le i \le k$ . A path  $\rho = t_1 t_2 \ldots t_k$  is a finite sequence of transitions such that for  $k \ge 2$ , the ending state of  $t_i$  is the starting state of  $t_{i+1}$  for all  $1 \le i \le k - 1$ . A tour is a path whose starting state and ending state are the same. For convenience, we use  $start(\rho)$ ,  $end(\rho)$ ,  $label(\rho)$ , and  $in(\rho)$  to denote the starting state, the ending state, the label, and the input portion of the label of  $\rho$ , respectively.

Let  $\rho_1$  and  $\rho_2$  be two paths of M. When  $end(\rho_1)$  and  $start(\rho_2)$  are the same, we use  $\rho_1\rho_2$  to denote the *concatenation* of  $\rho_1$  and  $\rho_2$ . For clarity, sometimes we also use  $\rho_1 \circ \rho_2$  for  $\rho_1\rho_2$ . For  $\rho_1 = (s_1, s_h, T_1)$  and  $\rho_2 = (s_h, s_r, T_2)$ , we have  $\rho = \rho_1 \circ \rho_2 = (s_1, s_r, T_1 \circ T_2)$ .

A state  $s \in S$  is *reachable* if there exists a path starting from  $s_0$  and ending at s. We consider FSMs where all states are reachable.

An FSM is completely specified if functions  $\lambda$  and  $\delta$  are total; otherwise, it is partially specified. When an FSM M is not completely specified, it is possible to make M completely specified. Two typical ways of doing so are named after [16].

- angelic completion: for any  $(s, x) \notin domain(\delta)$ , add transition (s, s, x/null).

- demonic completion: i) add an erroneous state s<sub>err</sub>; ii) for any (s, x) ∉ domain(δ), add transition (s, s<sub>err</sub>, x/null); and iii) for any x ∈ I, add transition (s<sub>err</sub>, s<sub>err</sub>, x/null).

The completion, however, slightly changes the meaning of the FSM and is not always acceptable.

Two states  $s_i$  and  $s_j$  are equivalent if, for every input sequence  $\sigma$ ,  $\lambda(s_i, \sigma) = \lambda(s_j, \sigma)$ . If  $\lambda(s_i, \sigma) \neq \lambda(s_j, \sigma)$  then  $\sigma$  distinguishes between  $s_i$  and  $s_j$ . An FSM M is minimal if every state can be reached from the initial state of M and no two states of M are equivalent. Since only deterministic FSMs are considered, we can easily obtain a minimal FSM from any given FSM [27, 46]. In the following, we assume that all given FSMs are minimal.

When the specification of an IUT is given in the form of an FSM, we would like to automatically generate an efficient and effective *test sequence* from it. Here, a *test sequence* refers to an input sequence, which is typically obtained from a path of the given specification FSM. That is, our goal is usually to find a path in the given specification FSM such that

| transition     | starting state        | ending state          | label       |

|----------------|-----------------------|-----------------------|-------------|

| $t_0$          | $s_0$                 | $s_1$                 | a/0         |

| $t_1$          | $s_0$                 | $s_2$                 | <i>b/</i> 0 |

| $t_2$          | $s_0$                 | $s_2$                 | <i>c</i> /0 |

| $t_3$          | $s_1$                 | <i>s</i> <sub>2</sub> | a/1         |

| t4             | $s_1$                 | s2                    | <i>b/</i> 0 |

| $t_5$          | $s_1$                 | $s_0$                 | <i>c/</i> 0 |

| $t_6$          | <i>s</i> <sub>2</sub> | <i>s</i> <sub>1</sub> | a/1         |

| t <sub>7</sub> | <i>s</i> <sub>2</sub> | $s_0$                 | <i>b/</i> 0 |

| $t_8$          | <i>s</i> <sub>2</sub> | $s_2$                 | <i>c/</i> 0 |

Figure 1: An example FSM  $M_0$

Table 1: Transitions in  $M_0$

the input portion of this path is the desired test sequence and the output portion of this path is the expected output sequence.

**Example 1** An example 1-port FSM  $M_0$  is given in Figure 1. Here,  $S = \{s_0, s_1, s_2\}$ ,  $I = \{a, b, c\}$ , and  $O = \{0, 1\}$ . Transitions in  $M_0$  are listed in Table 1.

# 2.2 Fault models

Fault models can serve as a guide to test generation and fault coverage analysis, as claimed in [89]. When a specification M and its IUT have the same input alphabet and output alphabet, faulty IUTs can be classified into three types.

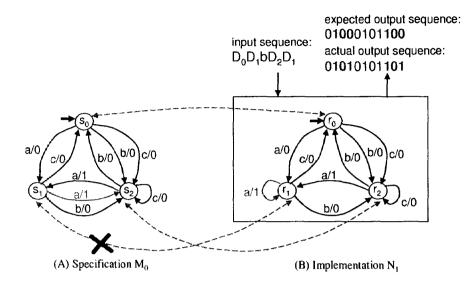

Figure 2: Faulty IUTs of example FSM  $M_0$

- An IUT has only *output faults* if *M* can be obtained from the IUT by changing the outputs of one or more transitions in the IUT.

- An IUT has only transfer faults if M can be obtained from the IUT by changing the ending states of one or more transitions in the IUT.

- An IUT has *hybrid faults* if *M* can be obtained from the IUT by changing the outputs and/or the ending states of one or more transitions in the IUT.

Here, we do not consider the fault type of *extra states*, i.e., the number of states of the implementation FSM will not exceed that of the specification FSM. We argue that this assumption is reasonable. As we know, the purpose of the conformance testing is to ensure that the behavior of the implementation *conforms to* the behavior specified by the specification. The existence of the extra states means the existence of the extra behavior which is not specification, and thus will not be tested.

**Example 2** Figure 2 shows three faulty IUTs of  $M_0$ . The shaded area surrounding an IUT represents the black box where only inputs and outputs can be observed. When transition  $(s_1, s_2, a/1)$  in  $M_0$  is concerned, IUTs shown in Figure 2(B), (C), and (D) have an output

### 3 MAIN ISSUES IN TESTING IN CONTEXT

(N) - ASP: abstract N-service primitive, an implementation-independent description of an interaction between a service-user and a serviceprovider at an (N)-service boundary. PDU: protocol data unit.

fault, a transfer fault, and a hybrid fault, respectively.

Based on the above fault models, we want to *automatically* generate an *effective and efficient* test sequence from a given specification, i.e., it is desirable to generate a test sequence as short as possible while detecting as many faults as possible. This is known as the *fault coverage* problem and the *test optimization* problem. We will discuss the existing solutions to these two problems in Chapter 4.

# 3 Main issues in testing in context

Ideally, an IUT can be tested in isolation, i.e., a tester can apply a desired input directly to the IUT and observe the actual output produced by the IUT directly. In practice, however, it is not always feasible: the IUT is often tested through its environment, called *context*. For example, in the distributed test architecture shown in Figure 3, the underlying network is the context of the IUT since it has to be used when the lower tester interacts with the IUT.

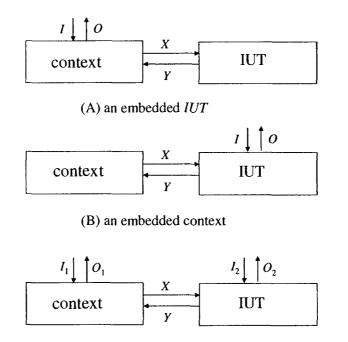

According to the ways of the interactions among the tester, the IUT, and the context, the architectures of testing in context can be classified into three types as shown in Fig-

$\diamond$

### 3 MAIN ISSUES IN TESTING IN CONTEXT

(C) a generic model

Figure 4: Context-based testing: types of test architecture

ure 4. Here, for simplicity, we demonstrate these architectures by treating the context as one component even though it may include multiple components instead. Petrenko et al. considered the situation where the IUT is an embedded component whose communication with the environment has to be carried out through its context, as shown in Figure 4(A). In [72, 73], they presented a framework of testing an embedded component in context. Along this direction, different approaches [23, 57, 70] are discussed for solving the problem of translating internal tests derived for an embedded component into external observable tests of the entire system. Different from their test architecture, we consider how to test an IUT that is associated with an embedded context as shown in Figure 4(B) [21].

The existence of the context may introduce additional problems for testing. In the previous example, when the underlying network is not transparent, in the sense that it has its own behavior, it is possible that both the inputs applied from the lower tester and the outputs produced by the IUT are modified by the underlying network. Consequently, the validity of the testing is problematic. Thus, the behavior of the context of the IUT has

to be considered for the test generation. In the following, we first introduce the *external* equivalence for context-based systems and then discuss the main issues in this setting.

#### **3.1** External equivalence

Let  $\mathcal{K}$  be a system consisting of a finite set of FSMs  $M_i = (S_i, s_{i,0}, X_i, Y_i, \delta_i, \lambda_i)$ , where  $i = 1, \ldots, k$ . Here, we assume all the actions in  $X_i, Y_i$  are distinct. Suppose  $I \subseteq \bigcup_i X_i$  and  $O \subseteq \bigcup_i Y_i$  are the sets of the *external inputs* and the *external outputs* regarding the entire system, respectively. For  $\mathcal{K}$  to be a meaningful system, we have the following assumptions.

- $I \cap (\bigcup_i Y_i) = \emptyset$ , i.e., an external input cannot be produced by any component FSM.

- $O \cap (\bigcup_i X_i) = \emptyset$ , i.e., an external output cannot be accepted by any component FSM.

- $(\bigcup_i Y_i) \setminus O \subseteq (\bigcup_i X_i) \setminus I$ , i.e., any internal output should be accepted by some component FSM.

We say FSM  $M_i$  communicates with FSM  $M_j$  if there exists an internal action in set  $Y_i \cap X_j$ . The communication among component FSMs can be either synchronous or asynchronous. We assume that the communication channels are reliable. A global FSM of a asynchronous/synchronous communication can be composed by performing reachability analysis [7, 62, 90, 93, 97]. In black-box testing, we are particularly interested in synchronous composition, where all the internal actions are hidden and only external inputs and outputs are indicated. In the following, we use operator  $\times$  to denote the synchronous product of component FSMs.

In the realm of deterministic FSMs, two FSMs are *trace equivalent* if for any input sequence, they produce the same output sequence in response. For testing in context, *external equivalence* is defined by taking into account the behavior of the context. Note that the following definition is adopted from [73] with slight modification.

**Definition 2 (External equivalence)** Let  $S_1$  and  $S_2$  be two FSMs, and C their context FSM.  $S_1$  is externally equivalent to  $S_2$  w.r.t. C, denoted by  $S_1 =_C S_2$ , if  $S_1 \times C$  is trace equivalent to  $S_2 \times C$ .

The goal of testing in context is to ensure that the IUT is *externally equivalent* to its specification in a given context. Test generation aiming at ensuring *external equivalence* needs to take into account the behavior of the context.

# 3.2 Main issues

Many issues arise for testing in context.

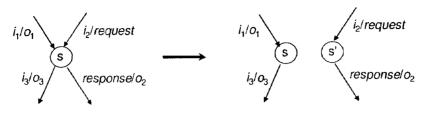

- stateless v.s. stateful. When the IUT and its context are stateful, test generation may suffer from the state explosion problem. Specification languages such as FSMs, Extended FSMs, and Labeled Transition Systems are often used to specify stateful systems. In this work, we consider the situation where the stateful IUT is specified by an FSM while its embedded context is either stateless or stateful. In the latter case, we require that the context be specified by a specification language that can be translated to *Extended Finite State Machines* (EFSMs), which is a concise specification formalism that allows the use of variables.

- deterministic v.s. non-deterministic. Studies on both deterministic testing and nondeterministic testing have practical significance and confront different challenges. We are particularly interested in test generation techniques of deterministic systems because two benefits can be provided.

- A high level confidence on the correctness of the IUT can be ensured by applying a test sequence whose length is polynomial to the size of the IUT. For example, trace equivalence can be guaranteed with a *checking sequence* whose length is polynomial to the number of transitions under certain conditions. The detailed discussion on this regard is in Chapter 4. On the other hand, test sequences of non-deterministic systems are often of infinite length [82] or much more costly by requiring to repeat the testing for many times with the fairness hypothesis that all the possible paths with non-deterministic choices are tested, which it actually can not be always guaranteed.

- If we can derive from deterministic testing that components  $I_1$  and  $I_2$  are trace equivalent to their respective specification  $P_1$  and  $P_2$ , then under certain circum-

stances we know  $I_1||I_2$  is a correct implementation of  $P_1||P_2$  without performing further *integration testing* or *system testing* which involves nondeterministic system specifications.

In this work, we consider the case when both the IUT and its context are deterministic.

- test criteria. Many fault coverage criteria have been proposed in the literature. In Chapter 4, four widely used criteria for FSM-based test sequence generation are explained, namely, the T-method, the U-method, the D-method, and the W-method. In this work, we choose the T-method in Chapter 6 and the W-method in Chapter 7 to demonstrate our proposed methods. Other criteria are applicable with proper adaptation.

- optimization on the efficiency. It is always desirable to reduce the time complexity to generate tests and to reduce the time to carry out the testing while a certain desired fault coverage is satisfied. The existing optimization techniques for different fault coverage criteria are discussed in Chapter 4.

- internal observer v.s. external observer only. An internal observer is an observer who can passively observe the interactions between IUT and its context although it has no control on them. An external observer is actually a tester who has the control to give the inputs and observe the outputs. When an internal observer is available, better testing results can be achieved by making use of the knowledge obtained by observing the internal interactions. We assume the internal observer is available.

- fault propagation. The problem of *fault propagation* describes the fact that some faults of the IUT can be tolerated by the context. There are two types of reasons resulting in the tolerance: i) the selected test sequence is incomplete in the sense that it can not distinguish all the faulty implementation; and ii) some faults are *intrinsically* tolerated by the context such that *no tester* can detect them. Note that the fault propagation problem does not exist when an internal observer is available. Thus, we do not consider fault propagation as we assume the internal observer.

• test executability. Test executability problem describes the situation where a test sequence generated solely from a given specification without taking into account the behavior of the context may not be executable when we carry out testing in context. This problem is caused by the uncontrollable interaction between IUT and its context during testing. This problem is crucial in testing in context, and we have a detailed discussion in Chapter 5.

# 4 Fault coverage and test optimization

It is well known that the exhaustive testing is impossible in practice, and a tester has to make a tradeoff between the fault coverage and the cost. When the IUT has certain properties, it is possible to utilize these properties to maximize the fault coverage. These desirable properties include the reliable reset, the existence of some special input sequences which can be used to identify the states in the IUT, etc. In this chapter, we introduce four typical test generation methods along with the corresponding optimization techniques. Namely, these methods are the T-method [68], the U-method [1, 63, 76], the D-method [29, 32, 85], and the W-method [11]. Actually, these methods can also serve as fault coverage criteria.

### 4.1 Graph representations of FSMs

Since most of the algorithms for test sequence generation are based on some well-known algorithms in graph theory, in the following, we introduce the graph representation of an FSM and several typical problems in graph theory.

Each FSM M has a graph representation G = (V, E, L), in which a state of M is represented by a vertex from V and a transition of M is represented by an edge from E. We use  $G_M$  to denote the graph representation of FSM M, where state  $s_i$  is represented by vertex  $v_i$ , and transition from  $s_i$  to  $s_j$  with label x/y is represented by edge  $(v_i, v_j, x/y)$ .

Terminologies and notations defined for FSMs are naturally extended to their graph representations.

A digraph is strongly connected if for any ordered pair of vertices  $(v_i, v_j)$  there is a path from  $v_i$  to  $v_j$ . When G is strongly connected, a Postman Tour of G is a tour which contains every edge of E at least once. Given digraph G = (V, E, cost), where cost is a cost function that associates each edge in E with a cost, we say G is a weighted digraph. The *Chinese Postman Problem (CPP)* is to find the minimum-cost Postman Tour in a strongly connected (weighted) digraph. Given a strongly connected G = (V, E) and  $E_1 \subseteq E$ , a *Rural Postman Tour* is a tour which contains each edge in  $E_1$  at least once. The *Rural Chinese Postman Problem (RPP)* is to find a Rural Postman Tour with minimum cost. CPP has a polynomial time solution while RPP is in general NP-hard. Various sophisticated heuristics have been proposed in the literature for RPP (see e.g. [22]).

### 4.2 T-method

The fault coverage criterion specified by the T-method [68] is as follows.

• T-method: The corresponding path of the generated test sequence in the specification FSM *M* should contain each transition in *M* at least once.

According to the T-method, a transition is tested to be correct when its output is correct in response to the corresponding input. If a faulty IUT has only output faults, test sequences generated with the T-method are capable of detecting any faults; otherwise, a faulty IUT may not be distinguished. The advantage of the T-method is that shorter test sequences are generated.

Clearly, the optimization problem of generating a minimal-length test sequence can be reduced to Chinese Postman Problem (CPP).

**Example** 3 Given specification  $M_0$  in Figure 1, a tour  $\rho$  is found:

## $\varrho = t_0 t_3 t_6 t_5 t_1 t_8 t_6 t_4 t_7 t_2 t_7$

$\diamond$

Then a test sequence of length 11 can be derived by concatenating the inputs of  $\rho$ :  $\chi = in(\rho) = aaacbcabbcb$ , whose expected output sequence is 01100010000.

The faulty IUTs in Figure 2(B) and (D) can be distinguished by  $\chi$  since the actual output sequences are 00100010000 and 00000010000, respectively. However, the faulty IUT in Figure 2(C) cannot be distinguished since it yields the same output sequence as expected.

| states                | ates UIO sequence                 |  |

|-----------------------|-----------------------------------|--|

| $s_0$                 | IntFromU                          |  |

| $s_1$                 | $ReqFromL \circ RspFromL$         |  |

| $s_2$                 | RspFromL • PerRspFromU            |  |

| <i>s</i> <sub>3</sub> | PerRspFromU                       |  |

| <i>s</i> <sub>4</sub> | ReqFromL • RspFromL • PerRspFromU |  |

Table 2: UIO sequences for each states in  $M_1$

#### 4.3 U-method

The U-method can be applied to a special class of FSMs that have a Unique Input/Output sequence (UIO sequence) for each of their states. Given an FSM M, a UIO sequence of a state s is an input sequence such that the corresponding output sequence obtained by applying this input sequence at s in M is unique from those obtained by applying this input sequence at any other state. We use  $UIO_i$  to denote the UIO sequence for state  $s_i$ . Formally,

**Definition 3 (UIO sequences)** Given an FSM  $M = (S, I, O, \delta, \lambda, s_0)$ , an input sequence UIO<sub>i</sub> is a UIO sequence of state  $s_i$  if for any  $s_j \in S$ ,  $s_j \neq s_i$  implies  $\lambda(s_j, \text{UIO}_i) \neq \lambda(s_i, \text{UIO}_i)$ .

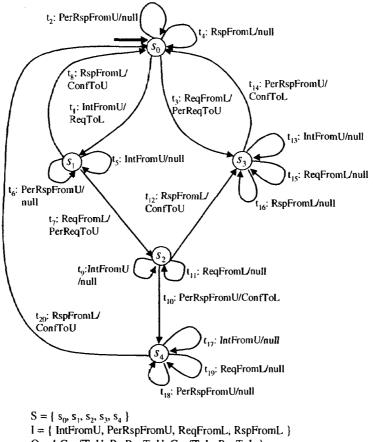

**Example 4** We present here a protocol for establishing service connection, which is commonly used in peer-to-peer systems. In this protocol, any participant, upon receiving a request from its user, can initiate a connection with any other peer participant by issuing a *connection request*. The connection will not be established until the confirmations from all peer participants are received. Each confirmation represents the permission from another participant. For simplicity, we consider such a protocol with two participants.

Note that the *connection requests* can be issued concurrently by both participants. That is, the two participants may issue the requests at about the same time. Consequently, it is possible that each participant receives a *connection request* from the other participant right after it has sent out its own request and yet before it receives the confirmation from its

Figure 5: FSM  $M_1$  of the connection establishment protocol for one participant

partner. In this case, in order to establish a connection, each participant should respond to the request from its partner as well as receive the confirmation from its partner for its own request.

The specification FSM  $M_1 = (S, I, O, \delta, \lambda, s_0)$  of a participant in this protocol is shown in Figure 5. The service primitives and their symbolic representations for each participant in this protocol are listed below.

- *IntFromU*: user's intention for establishing a service connection;

- *ReqToL*: message to request the partner to establish connection;

- *RspFromL*: response from the partner for service connection;

- *ConfToU*: confirmation of the service connection to the user;

- *ReqFromL*: request from the partner for service connection;

- *PerReqToU*: request for the user's permission for service connection;

- *PerRspFromU*: user's permission for a service connection;

- ConfToL: confirmation of the service connection to the partner.

Suppose process A is a participant of this connection establishment protocol modeled by  $M_0$ . I/O pair IntFromU/ReqToL means that upon receipt of message IntFromU, A will send a request to its partner for the connection establishment. I/O pair ReqFromL/PerReqToU represents that when A receives message ReqFromL, it will send a request to its user asking for permission.

Table 2 shows the shortest UIO sequences for each state.

$\diamond$

Not every FSM has a UIO sequence for each of its states, and the problem of finding UIO sequences for an FSM is very hard [55]. For a given specification M, the following decision problems are proven to be PSPACE-complete: i) whether a specific state s of M have a UIO sequence; ii) whether all states of M have UIO sequences; iii) whether some of the states of M have UIO sequences. Furthermore, even though a state has a UIO

sequence, it is possible that this UIO sequence is of exponential length. In this case, there is no value for testing purpose. Note that these are the worst case result. In practice (e.g. communication protocols), short UIO sequences exist for most cases and can be found quickly [56]. Discussions on finding the UIO sequences from a given FSM can be found in [12, 28, 18, 47, 56, 76].

For conformance testing,  $UIO_i$  can be used to *verify* whether an IUT is in a state corresponding to state  $s_i$  since the desired output sequence is supposed to be produced when applying  $UIO_i$  in  $s_i$ . This property can be used to tackle the transfer faults in IUTs in the sense that the ending states of transitions can be verified with UIO sequences. Thus, the U-method is inspired.

The fault coverage criterion specified by the U-method [1, 63, 76] is as follows.

• U-method: The corresponding path of the generated test sequence in the specification FSM M should contain each transition in M with its ending state in the implementation FSM verified.

**Example 5** Suppose we want to generate a test sequence from specification  $M_1$  in Figure 5 with the U-method. For simplicity, we only consider two transitions, namely,  $t_9$  and  $t_{20}$ , as examples.

Let  $\rho_9 = t_9 t_{12} t_{14}$  and  $\rho_{20} = t_{20} t_1$  be two paths in  $M_1$ . Since the input portion of  $label(t_{12}t_{14})$  is a UIO sequence for the ending state of transition  $t_9$ , the ending state of  $t_9$  is verified by applying the input portion of  $\rho_9$ . That is,  $\rho_9$  can be used to test the correctness of  $t_9$ . We call such a path a *test segment* of  $t_9$ . Similarly,  $\rho_{20}$  is a test segment of  $t_{20}$ . Using transfer sequence  $t_1 t_7 t_{10}$  to connect these two test segments, we get

$\rho = t_9 t_{12} t_{14} t_1 t_7 t_{10} t_{20} t_1$

which is a path containing both test segments.

Analogously, a path  $\rho$  in M can be found containing the test segments of all the transitions in  $M_1$ . Then the input sequence  $in(\rho)$  is a desired test sequence satisfying the U-method.

#### 4.3.1 Test optimization

As the U-method is effective to detect the transfer faults in the IUTs, it is appealing to study on how to minimize the lengths of the generated test sequences. In the literature, a lot of contribution has been made in this regard [1, 9, 10, 20, 33, 34, 63, 76, 78, 95], and the main ideas of these work are to maximize the *overlaps* among the test segments and to reduce the use of the transfer sequences connecting test segments. In the following, we explain some latest results along this approach.

In [33], Hierons proposed the notion of the *invertible transitions*<sup>1</sup>. A transition  $(s_i, s_j, x/y)$  is *invertible* if it is the only transition entering state  $s_j$  with input x and output y. In the example FSM  $M_1$ ,  $t_1$ ,  $t_2$ ,  $t_3$  are invertible transitions while  $t_8$  and  $t_{20}$  are not because both  $t_8$  and  $t_{20}$  end at  $s_0$  with the same label RspFromL/ConfToU.

The existence of invertible transitions in existing protocol descriptions has been the major source of the recent success in reducing the lengths of the generated U-sequences. This is based on the following observation ([63, 33]):

$\mathcal{O}$ ) If t is an invertible transition and  $UIO_i$  is a UIO sequence of end(t), then the input sequence  $in(t) \circ UIO_i$  is a UIO sequence for start(t).

Suppose that t is an invertible transition, and  $t\sigma$  is a test segment for t in the sense that  $\sigma$  is a path induced by applying the UIO sequence of state end(t) at end(t). Now if t' is a transition adjacent to t in the sense that end(t') = start(t), then path  $t't\sigma$  is a test segment for t'. As  $t't\sigma$  contains test segments for both t' and t, we say there is an overlap between test segment  $t't\sigma$  and test segment  $t\sigma$ . By using invertible transitions, the overlap between test segments is increased. It follows that the length of the generated U-sequence can be reduced.

Some heuristic algorithms have been proposed in [63, 33] to maximize the use of invertible transitions to reduce the lengths of the U-sequences. In doing so, the notion of *invertible transition* is extended to that of *invertible sequence* [34]. A path  $\rho$  is an *invertible* sequence if it is the only path with label  $label(\rho)$  that ends at  $end(\rho)$ . That is, for any path

<sup>&</sup>lt;sup>1</sup>A similar notion called *non-converging edge* was defined on the digraphs that represent the FSMs ([63]).

$\rho'$ ,  $start(\rho) \neq start(\rho')$  implies  $end(\rho) \neq end(\rho')$  or  $label(\rho) \neq label(\rho')$ . Clearly, when the length of an invertible sequence is 1, it is actually an *invertible transition*.

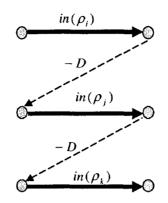

Similar to  $\mathcal{O}$ ), we have the following result [34]:

$\mathcal{O}'$ ) If  $\rho$  is an invertible sequence and  $UIO_i$  is a UIO sequence of  $end(\rho)$ , then the input sequence  $in(\rho) \circ UIO_i$  is a UIO sequence of  $start(\rho)$ .

Note that the additional UIO for  $start(\rho)$  obtained from  $\mathcal{O}'$ ) may be longer than the given UIO sequence for  $start(\rho)$ . For the example in Figure 5,  $t_{10}t_{20}$  is an invertible sequence ending at  $s_0$ . We know that  $UIO_0 = IntFromU$  and  $UIO_2 = RspFromL \circ PerRspFromU$ . By using invertible sequence  $t_{10}t_{20}$ , we have another UIO sequence for  $s_2$ :

# $UIO'_{2} = PerRspFromU \circ RspFromL \circ IntFromU.$

Although this newly found UIO sequence is longer than the given one, it may help to reduce the *total* length of a U-sequence since the test segment it produced has an *overlap* with other test segment(s). Let us use  $\rho_i$  to denote the test segment formed by concatenating  $t_i$ and the path induced by applying the originally given UIO sequence of  $end(t_i)$  at  $end(t_i)$ . Consider the two test segments for transitions  $t_9$  and  $t_{20}$  in  $M_0$ . We have  $\rho_9 = t_9t_{12}t_{14}$  and  $\rho_{20} = t_{20}t_1$ . Using transfer sequence  $t_1t_7t_{10}$  to connect these two test segments, we get

$\rho = t_9 t_{12} t_{14} t_1 t_7 t_{10} t_{20} t_1$

which is a path containing both test segments. The length of  $\rho$  is 8. If we use the UIO sequence derived according to  $\mathcal{O}'$ ), one of the test segments for  $t_9$  is  $\rho'_9 = t_9 t_{10} t_{20} t_1$  which contains  $\rho_{20}$ . In this case,  $\rho'_9$  can be used to verify both  $t_{20}$  and  $t_9$  and its length is only 4. With this observation, a heuristic algorithm was given in [34] to use the invertible sequences to reduce the length of U-sequences.

As from  $\mathcal{O}$ ) an optimal solution was derived for finding a minimal-length U-sequence in the special case when *all* transitions in M are invertible, now for general FSMs which may contain both invertible transitions and non-invertible ones,  $\mathcal{O}'$ ) leads to the following idea:

a') Determine a minimal-length path  $\rho = t_0 \sigma_1 t_1 \sigma_2 t_2 \dots \sigma_k t_k \sigma_0$ , where for  $0 \le i \le k$ ,  $\sigma_i t_i$ is an invertible sequence and for each  $t \in M$ , there exists  $i \ (0 \le i \le k)$  such that  $t_i = t$ . Without loss of generality, we assume  $t_0$  is a transition starting from the initial state  $s_0$ .

b') Obtain  $\rho$  by removing  $\sigma_0$  from  $\rho$  and appending path  $\rho'$  induced by applying the UIO sequence of  $end(t_k)$  at state  $end(t_k)$ .

Then,  $in(\rho)$  can be used as the desired test sequence. This is formally introduced below.

**Definition 4 (proximate test path)** Let M be a given FSM. Suppose  $t_i$  is a transition in M and  $\sigma_i$  is a path in M ( $0 \le i \le k$ ). A proximate test path of M is  $\varrho = t_0 \sigma_1 t_1 \sigma_2 t_2 \dots \sigma_k t_k \sigma_0$  such that:

- $t_0$  is a transition starting from the initial state  $s_0$ ;

- $\forall i \in \{0, \ldots, k\}, \sigma_i t_i \text{ is an invertible sequence};$

- $\forall t \in M, \exists i \ (0 \leq i \leq k) \text{ such that } t = t_i.$

Let  $\rho = t_0 \sigma_1 t_1 \sigma_2 t_2 \dots \sigma_k t_k \sigma_0$  be a proximate test path of a given specification M, where  $t_i$  is a transition and  $\sigma_i$  is a path in M such that  $\sigma_i t_i$  is an invertible sequence for  $1 \leq i \leq k$ . If  $end(t_k) = s_m$ , then  $in(t_0\sigma_1 t_1\sigma_2 t_2 \dots \sigma_k t_k) \circ UIO_m$  is a test sequence satisfying the U-method.

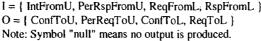

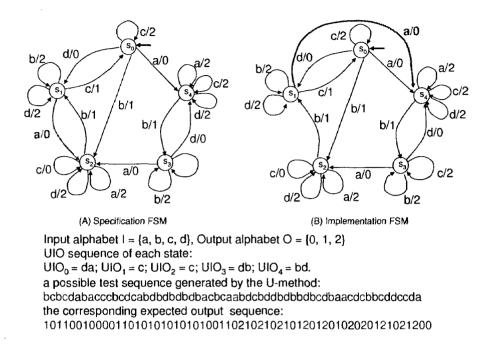

The algorithms on how to find a minimal-length proximate test path of M is explained in details in [20]. Given specification  $M_1$  in Figure 5, a test sequence of length 26 can be generated by the approach in [20] compared with that of length 72 by the approach in [1] and that of length 31 by the approaches in [63, 33].

#### 4.3.2 Weakness and strength of the U-method

The U-method does not support the *full* fault coverage due to the following two main reasons.

i) It does not check whether the starting states of transitions are correct. That is, when a transition starts from a wrong state in the IUT, no mechanism from the U-method intends to check it directly.

Figure 6: Illustration of the weakness of the U-method

ii) The uniqueness of the output sequence in response to a UIO sequence in the specification does not guarantee the uniqueness of that in the IUT. In a faulty IUT, it is possible that there are other states such that the same output sequence is produced by applying the UIO sequence in those states. Consequently, the state verification fails.

**Example** 6 A faulty IUT (Figure 6(B)) of the specification shown in Figure 6(A) has a transfer fault for transition  $(s_1, s_2, a/0)$ : instead of ending at state  $s_2$ , it ends at state  $s_4$  in the IUT. The IUT passes the testing with a test sequence generated by the U-method since the actual output sequence produced by the faulty IUT is the same as the expected one with this test sequence. In this case, the testing fails to detect the above transfer fault.  $\diamond$

The strength of the U-method is that it can achieve a *satisfactory* fault coverage with an *acceptable* cost [92, 79, 67]: On one hand, compared to the T-method, the U-method is much more effective in detecting faults; On the other hand, the U-method generates much shorter test sequences and are less restrictive than those methods (e.g. the D-method and the W-method) supporting the full fault coverage. For example, the U-method does not require a completely specified specification, reliable reset, a distinguishing sequence, etc.

Due to the benefits the U-method provides, it is desirable to incorporate the U-method with the characterization sets (see Chapter 4.5 for the definition), which exist for all the minimal FSMs, such that the U-method is applicable to all the FSMs. For example, in [37], Hierons proposed a technique to generate a minimal-length test sequence satisfying the U-method with a characterization set.

#### 4.4 D-method

The D-method is applicable to a special class of FSMs that have a distinguishing sequence (DS) [27, 52]. Given an FSM M, a distinguishing sequence is an input sequence D with the following characteristics: the output sequences produced by M in response to D in different states of M are all different. Formally,

**Definition 5 (distinguishing sequences)** Given an FSM  $M = (S, I, O, \delta, \lambda, s_0)$ , an input sequence D is a distinguishing sequence of M if for all  $s_i, s_j \in S$ ,  $s_i \neq s_j$  implies  $\lambda(s_i, D) \neq \lambda(s_j, D)$ .

Not every FSM has a DS. It is a PSPACE-complete problem to determine whether a given FSM has a DS [55]. The classical algorithms of finding a DS are of exponential time as discussed in [27, 52].

Clearly, a DS is a UIO sequence applicable to all the states. The existence of a DS of an FSM implies the existence of a UIO sequence for each state of the FSM; but the reverse is not true.

**Example** 7 In Figure 1, a distinguishing sequence for  $M_0$  is D = aba: when we apply this input sequence to states  $s_0$ ,  $s_1$  and  $s_2$ , the output sequences are 001, 100, and 101, respectively. They are all different.

Two FSMs  $M_1$  and  $M_2$  are equivalent if and only if for every state of  $M_1$  there is an equivalent state of  $M_2$  and vice versa. An input sequence is a checking sequence of M if

and only if it distinguishes between M and any FSM that has the same sets of input and output alphabets as M but is not equivalent to M. Clearly, a checking sequence is a special test sequence that guarantees the full fault coverage.

Assume that the IUT behaves like some (unknown) FSM N with the number of states no greater than that of the specification M. Since M and N are deterministic and minimal, determining whether N is equivalent to M can be achieved by establishing isomorphism between M and N. More precisely,

- for each state s in M, we identify a state r in N that corresponds to s.

- for each transition  $t = (s_1, s_2, x/y)$  in M, we verify that there exists a transition  $t' = (r_1, r_2, x/y)$  in N which starts from a state corresponding to  $s_1$ , ends at a state corresponding to  $s_2$ , and gives the same output y upon the same input x.

A checking sequence is designed to help us to achieve the above two goals. With respect to these goals, the construction of a checking sequence usually involves two steps: one for *state identification* and one for *transition verification* [56].

The purpose of state identification is to build a one-to-one correspondence between the states in M and those in N. State identification using UIOs is possible but it turns out to be hard and less practical [40]. A characterization set (which is discussed in Chapter 4.5) is easier to find than a distinguishing sequence, yet a test suite generated using a characterization set [11] is usually much longer than that generated using a distinguishing sequence in terms of total length of the test sequences [8, 29, 32, 85]. Of course, DS can also be used for state verification in the sense of verifying the ending states of transitions.

Recall that D = aba is a distinguishing sequence of  $M_0$  in Figure 1. If we apply D to the IUT of  $M_0$  and observe 001, then we know that the state of N before we apply D corresponds to  $s_0$ , which is the only state in  $M_0$  that gives output sequence 001 in response to input sequence aba. Similarly, if we apply D to the IUT several times (at different states of N) and observe 001, 100, and 101, then we know that N has (at least) three states and the states of N before we apply each D correspond to  $s_0$ ,  $s_1$  and  $s_2$  respectively.

**Example** 8 Suppose  $N_1$  shown in Figure 7(B) is an FSM describing the behavior of a possible implementation of specification  $M_0$  in Example 2.1.

Figure 7: An illustration of the necessity of state identification

Recall that for  $M_0$  in Figure 1, we have distinguishing sequence D = aba. As the dashed arrows in Figure 7 show, we have  $r_0$  corresponds to  $s_0$  and  $r_2$  corresponds to  $s_2$  in the sense that  $\lambda(s_0, D) = \lambda(r_0, D) = 001$  and  $\lambda(s_2, D) = \lambda(r_2, D) = 101$ . However,  $\lambda(s_1, D) \neq \lambda(r_1, D)$ :  $M_0$  (at  $s_1$ ) and  $N_1$  (at  $r_1$ ) give different output sequences 100 and 101 respectively in response to input sequence D. In other words, at  $r_1$ , the implementation FSM  $N_1$  does not behave like  $M_0$ .

We can detect that  $N_1$  is a faulty implementation of  $M_0$  on the stage of state identification: by applying D to the IUT, we fail to find a state in  $N_1$  which produces output sequence 100 in response to D, as  $s_1$  does.

When a distinguishing sequence D of M is given, sometimes a prefix of D is sufficient in helping us identify a state in N with a state in M. For example, in Figure 1, state  $s_0$  is the only one that gives output 0 in response to input a. Thus, we can simply use a (which is a prefix of D) as input to the IUT to identify a state in N that corresponds to  $s_0$ . We will use  $D_i$  to denote the *prefix distinguishing sequence for*  $s_i$ . It is the shortest prefix of D that is sufficient to distinguish state  $s_i$  from others, i.e., for any state  $s_j$  where  $s_i \neq s_j$ ,  $\lambda(s_i, D_i) \neq \lambda(s_j, D_i)$ . In Figure 1, with D = aba, the prefix distinguishing sequences for

$\diamond$

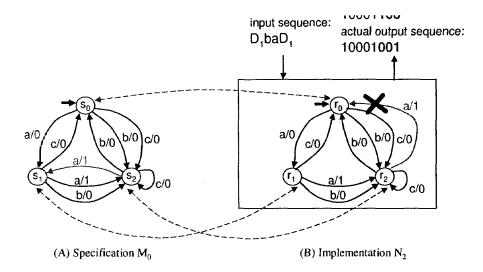

Figure 8: An illustration of the necessity of transition verification

states  $s_0$ ,  $s_1$ , and  $s_2$  are:  $D_0 = a$  and  $D_1 = D_2 = aba$ . In the following, we consider the situation when the prefix distinguishing sequence  $D_i$  is given for all i < n, where n is the number of states in M.

An  $\alpha'$ -sequence [39] is an input/output sequence used to identify some states in N with D or  $D_i$  ( $0 \le i < n$ ). A set of  $\alpha'$ -sequences that can jointly identify all the states of N is called an  $\alpha'$ -set. These two terminologies are evolved from similar but more restrictive terminologies  $\alpha$ -sequences and  $\alpha$ -set [85], respectively.

**Example** 9 In the previous example, let  $\rho_0 = (s_0, s_1, a/0)$ ,  $\rho_1 = (s_1, s_1, aba/100)$ , and  $\rho_2 = (s_2, s_1, aba/101)$  be the paths induced by applying  $D_0$ ,  $D_1$ , and  $D_2$  to  $s_0$ ,  $s_1$ ,  $s_2$ , respectively. Let  $\rho = \rho_0 \circ \rho_1 \circ (s_1, s_2, b/0) \circ \rho_2 \circ \rho_1$ . Then,  $label(\rho) = aabababaabaa/01000101100$  is an  $\alpha'$ -sequence, and  $\{label(\rho)\}$  is an  $\alpha'$ -set. In fact, we can use this  $\alpha'$ -sequence to identify all states in  $N_1$ : When we apply the input portion of  $label(\rho)$ , i.e.,  $D_0D_1bD_2D_1 = aabababaabaa,$  to  $N_1$ , if the expected output sequence 01000101100 is produced, then we can conclude that there are three distinct states in  $N_1$  corresponding to those in  $M_0$ . However, the actual output sequence produced is 01010101101 which is different from the expected one. Consequently, the one-to-one correspondence cannot be found between the states in  $M_0$  and those in  $N_1$ . Thus, we can conclude that  $N_1$  is a faulty implementation. **Example** 10 Suppose that the FSM  $N_2$  shown in Figure 8(B) describes another implementation of specification  $M_0$ .

Using the same  $\alpha'$ -sequence aabababaaba/01000101100 on  $N_2$ , we observe output sequence 01000101100 as expected upon the input sequence aabababaabaa. Thus, we conclude that there are three states in  $N_2$  corresponding to  $s_0, s_1$ , and  $s_2$  in  $M_0$ , respectively.

Later on we will show that even though  $N_2$  passes the test for state identification, it fails the test for transition verification.

Suppose that the state identification has been achieved. We can use this knowledge to investigate the structure of N to determine whether it is equivalent to the specification FSM M. This can be realized by transition verification which builds the one-to-one correspondence between the transitions in M and those in N. More precisely, for each transition  $t = (s_i, s_j, x/y)$  in M, we verify the existence of a corresponding transition t' in N. This is basically achieved by the following three steps: i) lead N to the state corresponding to  $s_i$ ; ii) verify the label of t' by applying x to N to check whether the output is y; and iii) verify whether the ending state of t' corresponds to  $s_j$ .

Steps ii) and iii) are usually realized by including  $\beta$ -sequences into checking sequence construction. A  $\beta$ -sequence of transition  $t = (s_i, s_j, x/y)$  is the input/output sequence  $x/y \circ D_j/\lambda(s_j, D_j)$ . For example, in the FSM  $M_0$  in Figure 1, the  $\beta$ -sequence of  $t = (s_2, s_1, a/1)$  is  $a/1 \circ D_1/\lambda(s_1, D_1) = aaba/1100$ .

When N is led to such a state r that its correspondence with a state in M can be derived, typically via state identification, we say r is recognized. A state r in N is verified if we apply an input sequence, typically a (prefix) distinguishing sequence, to N at this state in order to check the output sequence to confirm the correspondence between r and a state in M. If an input sequence allows us to lead N to a state recognized as  $s_i$ , check its output y in response to input x, and subsequently verify that the ending state corresponds to  $s_j$ , then we say transition  $t = (s_i, s_j, x/y)$  is verified in this input sequence. The formal definitions of the notions can be found in [85].

$\diamond$

#### 4 FAULT COVERAGE AND TEST OPTIMIZATION

Suppose we want to verify the correspondence between transition  $t = (s_2, s_1, a/1)$  in  $M_0$  and some  $t' = (r_2, r_1, a/y)$  in  $N_2$  in Figure 8(B). To apply the  $\beta$ -sequence of t, we first need to make sure that the current state in  $N_2$  is recognized as  $s_2$ . This can be realized by making use of the result of state identification. Recall that we use  $\alpha'$ -sequence  $D_0D_1bD_2D_1/\lambda(s_0, D_0D_1bD_2D_1) = aabababaaba/01000101100$  to identify states in  $N_2$ . This implies that if the current state in  $N_2$  is recognized as  $s_0$ , then after applying input sequence  $D_0D_1b$  and observing correct output sequence 01000, we know the current state of  $N_2$  is recognized as  $s_2$ . This is because we have already checked the output of  $D_0D_1bD_2$  for state identification. Similarly, if the current state of  $N_2$  is recognized as  $s_1$ , then after applying input sequence of  $N_2$  is recognized as  $s_2$ . In fact, whether the current state in  $N_2$  corresponds to  $s_1$  or not is also known after we apply input sequence  $D_1b$ . We just need to check whether the output sequence in response to  $D_1$  is 100.

Now we use this knowledge to lead  $N_2$  to a state recognized as  $s_2$ . Suppose  $N_2$  is currently in state  $r_0$ . We apply input a to  $N_2$ , and  $r_1$  is *supposed* to be reached. Next, we apply  $D_1b$  on  $N_2$ . If the expected output sequence 1000 is produced in response, we can conclude that: i) before applying  $D_1b$ ,  $N_2$  was *indeed* in a state corresponding to  $s_1$ ; and ii) after applying  $D_1b$ , a state recognized as  $s_2$  is reached.

Having reached a state recognized as  $s_2$ , we are ready to use  $\beta$ -sequence to test whether the label and the ending state of t' are correct. We apply input a to  $N_2$ , and output 1 is produced as expected. That is, the label of t' is correct. Finally, we verify that the ending state in  $N_2$  corresponds to  $s_1$  by applying  $D_1$ : The expected output sequence is 100 while the actual output sequence is 001.

In summary, we use input sequence  $D_1baD_1$  to verify the correspondence between transition t and t', where  $D_1b$  is used to lead  $N_2$  to reach  $r_2$ , and the last  $D_1$  is used to verify the ending state of t'. This is shown in Figure 8. Since the expected output sequence is 010001100 and the actual one is 010001001, there does not exist a transition in  $N_2$  corresponding to t. Therefore, we conclude that  $N_2$  is a faulty implementation of  $M_0$ .

Let n be the number of states in a given FSM M, and p the size of the input alphabet. According to [88], when a DS exists, the lower bound of the length of the generated checking sequence is  $\Omega(pn^3)$ ; and an algorithm is given to find a checking sequence of length  $O(p^2n^4\log(qn))$ . By making use of the prefix distinguishing sequences, Lee et al. proved in [56] that a checking sequence of length  $O(pn^3)$  can be found.

As shown above, when there exists a DS for a given FSM M, the D-method can be used to generate a checking sequence for M; and under a different condition (which will be discussed in Chapter 4.5), the W-method also applies.

The fault coverage criterion for checking sequences (the D-method and the W-method) [11, 32, 29, 85] is as follows.

• checking sequences: The corresponding path of the generated checking sequence in the specification FSM *M* should contain each transition in *M* with its starting state in the implementation FSM *identified* and its ending state in the implementation FSM *verified*.

When generating a checking sequence, it generally requires a completely specified specification FSM.

#### 4.4.1 The test optimization approach in [39]

Besides its advantage of guaranteeing a full fault coverage, the use of checking sequences for unit testing also provides an additional benefit for the *integration testing* or system testing. In the *unit testing*, if we can derive from deterministic testing that components  $I_1$  and  $I_2$ are trace equivalent to their respective specifications  $P_1$  and  $P_2$ , then without performing the *integration testing* or system testing, we know that the integration of  $I_1$  and  $I_2$  is a correct implementation of the parallel composition of  $P_1$  and  $P_2$ .

As the checking sequence usually suffers from too long a length, researchers are interested in the optimization techniques to reduce the testing cost in terms of the lengths of the generated checking sequence [8, 19, 39, 40, 81, 85, 86, 94]. Among these pieces of work, [39, 85, 86] consider how to reduce the length of the checking sequence by reducing the length of  $\alpha$ -sequences or by increasing the chances of overlaps among  $\alpha$ -sequences (or  $\alpha'$ -sequences) and  $\beta$ -sequences. [8, 81] focus on how to reduce the length of the checking sequence by exempting some transitions from being verified under certain conditions. [19, 94] introduce alternative  $\beta$ -sequences to expand the selection pool of test subsequences for transition verification such that the chance of the maximum overlaps is increased. Here, we explain two typical approaches in [39] and [86] on this topic. Note that the reduction techniques presented in [8, 19, 81, 94] can work together with those in [39] and [86] under certain circumstance.

In the work of Hierons and Ural [39], a checking sequence is generated in two steps: i) construct an auxiliary graph G' = (V', E') from  $G_M$ ; ii) find an RPP tour  $\rho$  in G', and then a checking sequence can be easily derived from  $\rho$ .

According to [39] as well as some other work [8, 41, 81, 85], a set of  $\alpha'$ -sequences that can form an  $\alpha'$ -set was first constructed. Each  $\alpha'$ -sequence will be used to identify a (sub)set of states in the implementation FSM. Suppose an  $\alpha'$ -sequence  $\rho$  can be used to identify those states in the implementation FSM that correspond to  $s_1, \ldots, s_k$  ( $k \ge 1$ ).  $\rho$  can be considered as some subsequences concatenated together, where each subsequence starts with an input/output sequence corresponding to the (prefix) distinguishing sequence of  $s_i$ for some  $1 \le i \le k$ . That is, each subsequence has form  $T_i = D_i/\lambda(s_i, D_i) \circ I_i$ , where  $I_i$  is a possibly null input/output sequence called transfer sequence. Input/output sequence  $T_i$  is called a *T*-sequence. According to the explanation of [39],  $I_i = \phi$  for all  $i \in \{0, \ldots, n-1\}$ . In this setting, an  $\alpha'$ -sequence is actually a concatenation of *T*-sequences.